? ?1緒論

計數器是數字邏輯系統中的基本部件,它是數字系統中用得最多的時序邏輯電路,其主要功能就是用計數器的不同狀態來記憶輸入脈沖的個數。除此以外還具有定時、分頻、運算等邏輯功能。計數器不僅能用于對時鐘脈沖的計數,還可使用于定時、分頻、產生節拍脈沖以及進行數字運算等。只要是稍微復雜一些.

采用中規模集成計數器來設計任意進制計數器,使設計和調試工作更趨于簡單,并且具有體積小,功耗低,可靠性高等優點。本文主要闡述了用中規模集成計數器設計任意進制同步加法計數器的設計思想,并對設計方法和步驟作了討論。

2.MSI中規模計數器概述

2.1MSI中規模計數器芯片種類

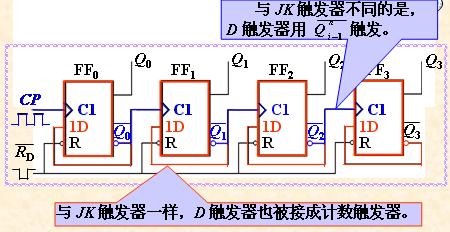

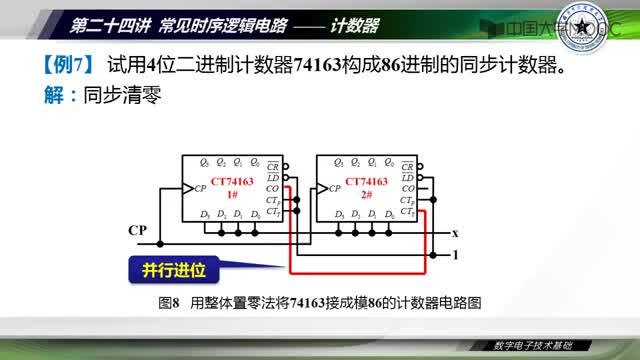

MSI中規模計數器芯片有非常多的種類。若按觸發時鐘的方式分類有:同步計數器、異步計數器;若按進制的“模”分類有:二進制計數器、十進制計數器;若按計數的方式分類:有加法計數器、減法計數器和可逆(加/減)計數器;若按芯片的型號分類就更多了,如:僅74系列的4位二進制計數器芯片就有161、163、191、193、197等,十進制計數器芯片有160、162等。

2.2MSI中規模計數器工作原理

2.2.1.以十進制同步計數器74LS160為例

74LS160的功能

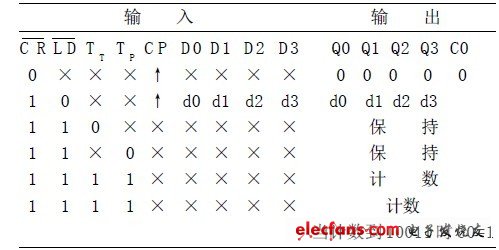

表174LS160功能表

?

根據功能表,74LSl60的功能說明如下:

(1)異步清零功能。當CR=0時,不論其他輸入如何,輸出Q3Q2Q1Q0為0000,表中“×”表示任意。

(2)同步并行置數功能。LD為預置數控制端,在CR=1的條件下,LD=0時,在CP上升沿的作用下,預置好的數據d3d2dld0被并行地送到輸出端,即此時的Q3Q2Q1Q0為d3d2dld0。

(3)保持功能。在CR=1和LD=1的前提下,只要TTTP=0,則計數器不工作,輸出保持原狀態不變。

(4)計數功能。正常計數時,必須使CR=1,LD=1,TTTP=1,此時在CP的上升沿的作用下,計

數器對CP的個數進行加法計數。當計數到輸出Q3Q2Q1Q0為1001時,C0=1,C0=1的維持時間是從Q3Q2QlQ0為1001時起到QaQ2Q1Q0狀態變化時止。

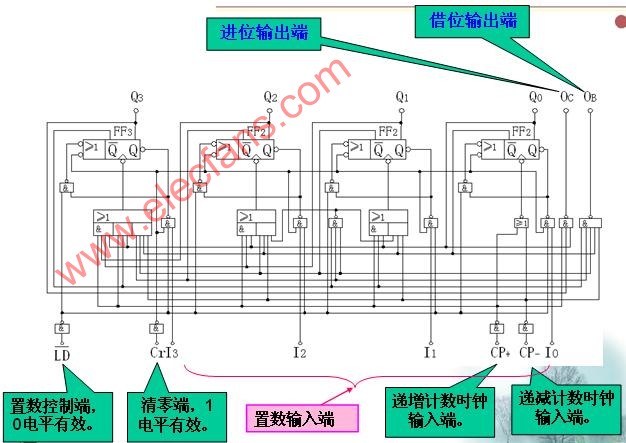

2.2.2以四位二進制計數器為例

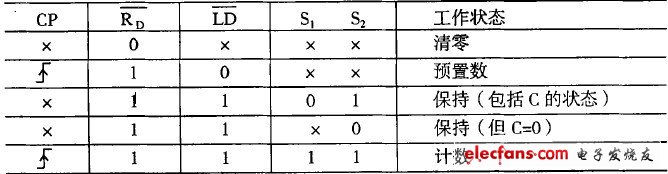

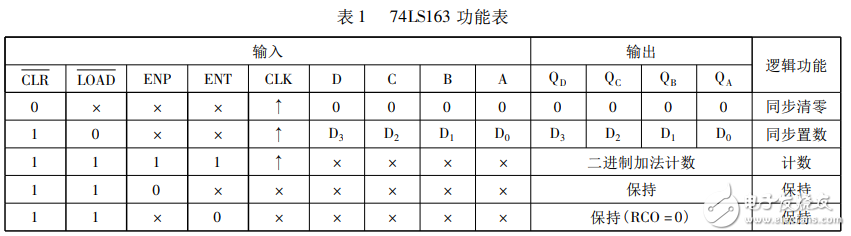

74LS161功能

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 表274LS161功能表

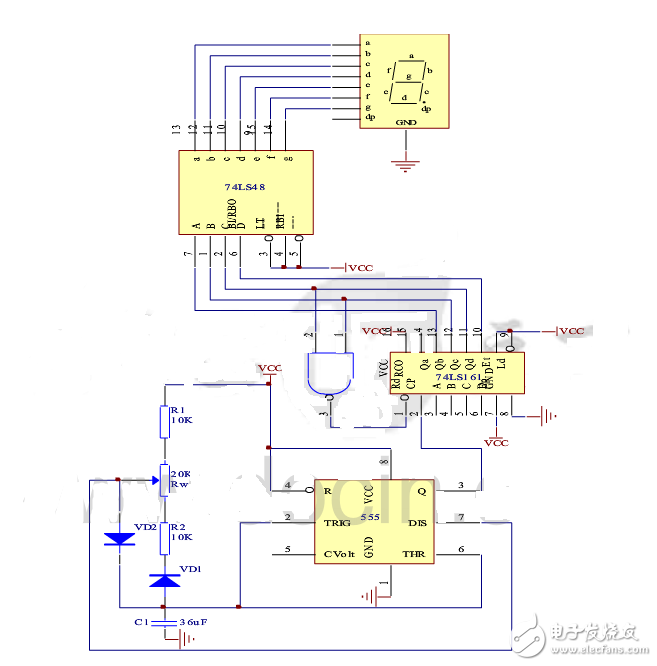

從功能表(一)可以看到,74LS161處于計數狀態時,引出端RD,LD,S:,S:都應為“1”(接高電平)。如果取其中一片T4161作為低位計數器〔記作(1)〕,對該片計數器來講,每來一個CP就計一次數,它始終工作在計數狀態。

3.設計方案

3.1采用反饋置零法來設計任意進制計數器

對于74LS160屬于異步置零輸入端的計數器,它是當置零輸入端出現有效電平(低電平)后計數器立即被置零,不受時鐘信號的控制。而對于74LS162/74LS163屬于同步置零輸入端的計數器。它是當置零輸入端出現有效電平(低電平)后計數器并不會立即被置零,必須等下一個時鐘信號到達后,才能將計數器置零。兩者用時必須加以區分。

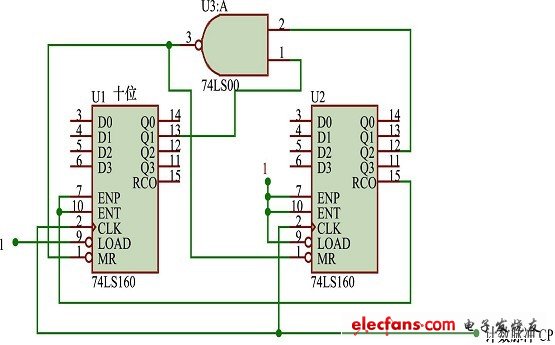

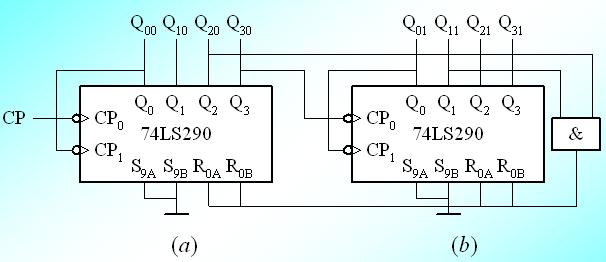

3.1.1采用并行法來設計24進制計數器

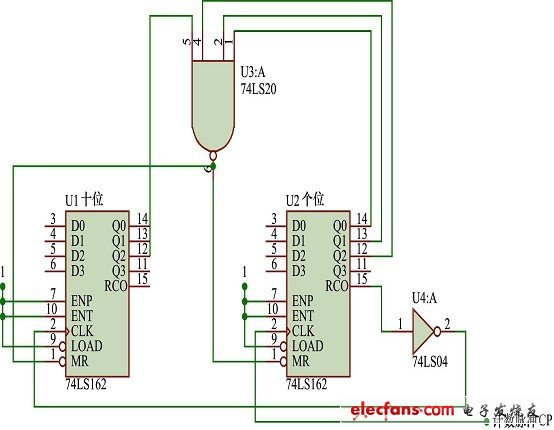

用74LS160并行置零法設計24進制計數器的電路圖如圖1所示。此電路的工作原理:先假設兩芯片的置零輸入端為1,則個位芯片由于計數控制端ENP=ENT=1,故該芯片始終處于計數狀態;而十位芯片的ENP、ENT連接的是個位芯片的進位控制端RCO,只有當個位芯片的計數狀態Q3Q2Q1Q0為1001時,RCO才為1.十位芯片才能計數。如果沒有反饋置零(即MR端恒接高電平)則電路是一個100進制計數器。現在電路中加上了反饋,當計數狀態(00100100)8421BCD碼=(24)10時,與非門輸出為零。由于74LS160屬于異步置零,且復位控制端MR低電平有效,所以計數器立即置零。由于電路中的狀態(24)10轉瞬即逝,顯示不出。故電路的有效狀態從(00)10到(23)10共24個,故此電路為24進制計數器。

圖1用74LS160并行置零法設計24進制計數器

另外如果采用同步置零74LS162計數器來設計24進制計數器,那么反饋代碼必須是(23)10相應的8421BCD碼為00100011.由此可見反饋信號應取自十位芯片的Q1及個位芯片的Q1和Q0,相應的與非門應改成四輸入端與非門。用74LS162并行置零法設計24進制計數器的電路圖如圖2所示。

圖2用74LS162并行置零法設計24進制計數器

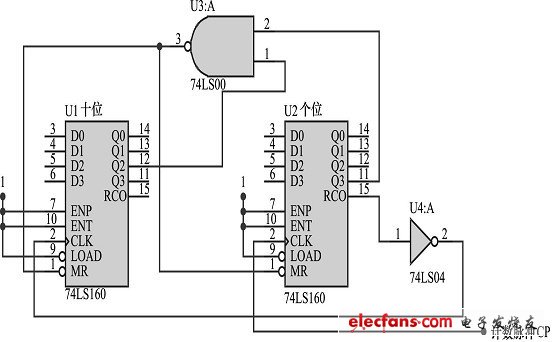

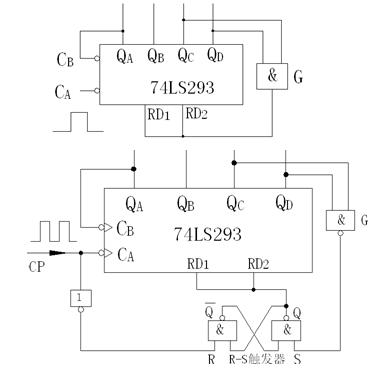

3.1.2采用串行法來設計48進制計數器

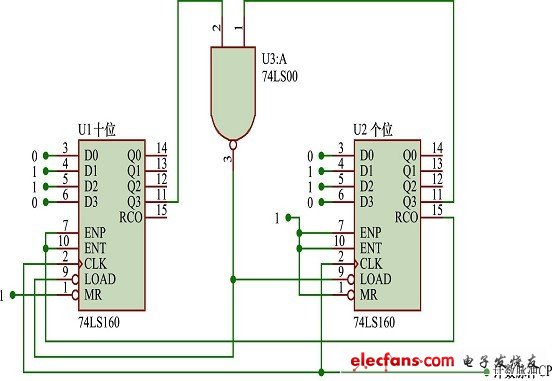

用74LS160串行置零法設計48進制計數器的電路圖如圖3所示。

?

圖3用74LS160串行置零法設計48進制計數器

此電路的工作原理:先假設兩芯片的置零輸入端為1,則個位芯片由于計數控制端ENP=ENT=1,故該芯片始終處于計數狀態;而十位芯片的ENP=ENT=1,但十位芯片的計數脈沖CLK是通過個位芯片的進位控制端RCO取反來控制的。當個位芯片的計數狀態Q3Q2Q1Q0為1001時,RCO為1.當下一個計數脈沖到來時RCO又為0.又由74LS160計數器的時鐘脈沖CLK是上升沿有效,與此同時,個位的RCO由1到0相當于一個下降沿,通過非門74LS04控制就得到一個上升沿,同時十位芯片才能計數。如果沒有反饋置零(即MR恒接高電平)則電路是一個100進制計數器。現電路中加上了反饋。當計數狀

態(01001000)8421BCD碼=(48)10時,與非門輸出為零。由于74LS160屬于異步置零,且復位控制端低電平有效,所以計數器立即置零。如果采用同步置零74LS162計數器來設計48進制計數器,那么反饋代碼必須是(47)10相應的8421BCD碼為01000111.由此可見反饋信號應取自十位芯片的Q2及個位芯片的Q2,Q1及Q0,相應的與非門應改成四輸入端與非門。74LS162串行置零法設計48進制計數器的電路圖如圖4所示。

圖4用74LS162串行置零法設計48進制計數器

另外,采用串行法設計時,十位芯片的計數脈沖CLK還可以通過個位芯片的最高位Q3端通過非門取反來控制,其他線路保持不變。只要對圖3或圖4稍加修改即可。

3.2采用反饋置數法來設計任意進制計數器

此方法適用于某些具有預置數的計數器,它是采用預置數控制端LOAD來實現。對于74LS160屬于同步式預置數的計數器來說,當LOAD出現有效電平低電平后待下一個時鐘脈沖信號到來后計數器輸出端的狀態Q3Q2Q1Q0=D3D2D1D0.使其跳過某些狀態來設計任意進制計數器。下面就以74LS160為例,用并行置數法設計23進制計數器,其中預置數端D3D2D1D0可以置零,也可以置十以內的任意四位二進制數。那么此電路在其置數時十位和個位的D3D2D1D0置入(01100110)8421BCD碼=(66)10,而反饋代碼十位和個位為(10001000)8421BCD碼=(88)10,相當于十進制數的88.由此分析可得到計數器的模為(88-66)+1=23,故計數器為23進制計數器,其設計電路圖如圖5所示。由此可以得到置數法的設計要點為:反饋代碼轉換成的十進制數-預置數端的代碼轉換成的十進制數+1=所設計的計數器的模。同樣我們也可以仿照前面的設計用串行置數法設計任意進制計數器。

圖5用74LS160并行置數法設計23進制計數器

4設計步驟

由于反饋置數法不太常用,且難于理解?下面我們就以反饋置零法為例,通過以上分析和經驗總結,可以得出任意N進制計數器的設計方法及步驟。

(1)根據計數模N來確定所需要計數器芯片的個數n.n=INT(logm(N-1))+1,INT表示取整。m:當芯片為十進制計數器時m取10,當芯片為四位二進制計數器時m取16.

(2)當n個計數器芯片連接成模為m的計數器

(3)選用并行法或串行法將n個計數器連接起來。

(4)確定反饋置零代碼。如果計數器芯片采用異步置零反饋代碼為(N)10,若是采用同步置零,則反饋代碼為(N??1)10.

(5)反饋置零代碼形式的轉換。如果芯片為十進制制計數器,將反饋代碼轉換成8421BCD碼的形式。若是四位二進制計數器,則將反饋代碼轉換成二進制數。

(6)將轉換結果與計數器的狀態輸出端進行比較,讓與1對應的引腳作用到與非門(反饋置零端低電平有效)或者與門(反饋置零端高電平有效)的輸入端,然后將與非門或者與門的輸出,連接到計數器芯片的反饋置零端即可。

電子發燒友App

電子發燒友App

評論