1.亞穩(wěn)態(tài)與設(shè)計可靠性設(shè)計數(shù)字電路時大家都知道同步是非常重要的,特別當要輸入一個信號到一個同步電路中,但是該

2017-12-18 09:53:13 8585

8585

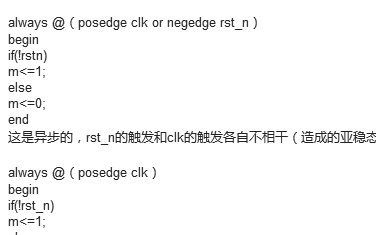

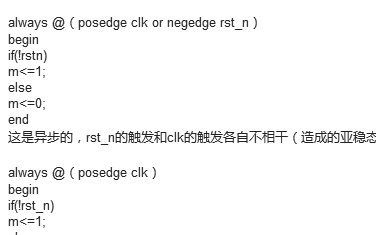

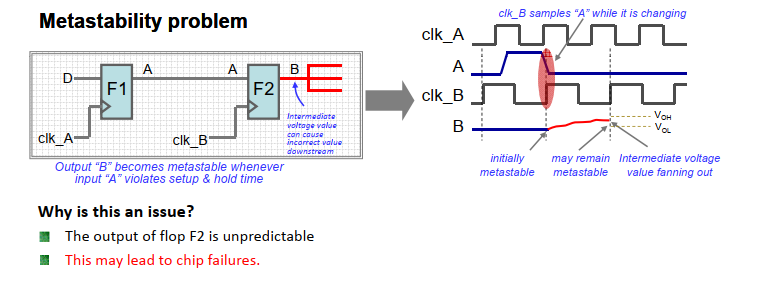

在復(fù)位電路中,由于復(fù)位信號是異步的,因此,有些設(shè)計采用同步復(fù)位電路進行復(fù)位,并且絕大多數(shù)資料對于同步復(fù)位電路都認為不會發(fā)生亞穩(wěn)態(tài),其實不然,同步電路也會發(fā)生亞穩(wěn)態(tài),只是幾率小于異步復(fù)位電路。

2020-06-26 16:37:00 1232

1232

只要系統(tǒng)中有異步元件,亞穩(wěn)態(tài)就是無法避免的,亞穩(wěn)態(tài)主要發(fā)生在異步信號檢測、跨時鐘域信號傳輸以及復(fù)位電路等常用設(shè)計中。

2020-09-30 17:08:43 3521

3521

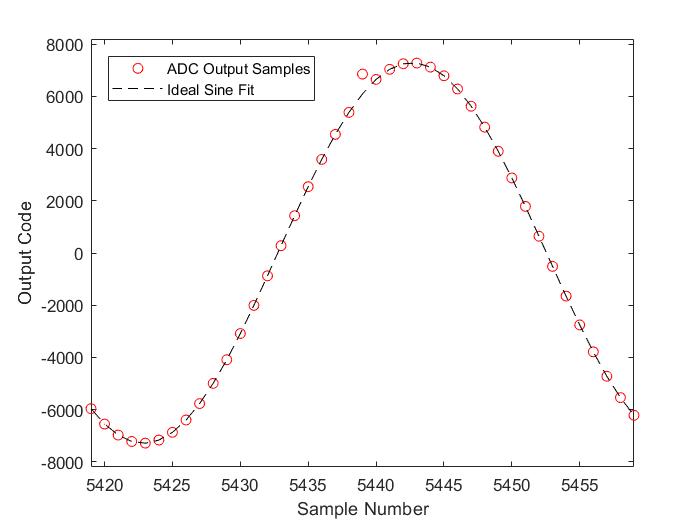

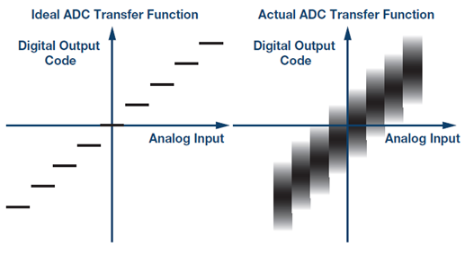

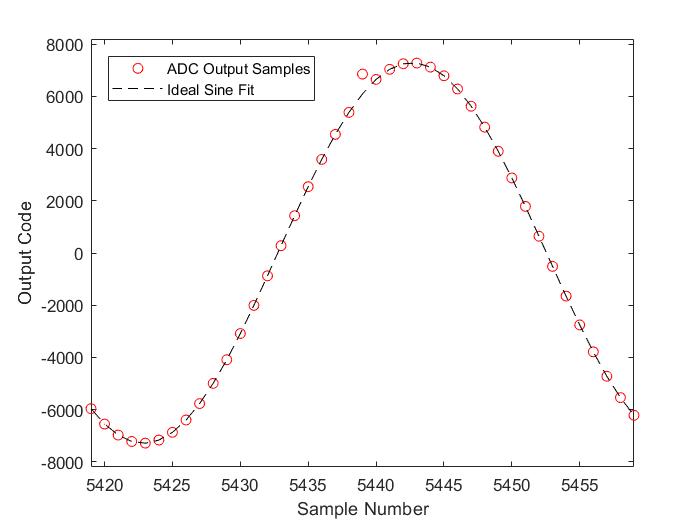

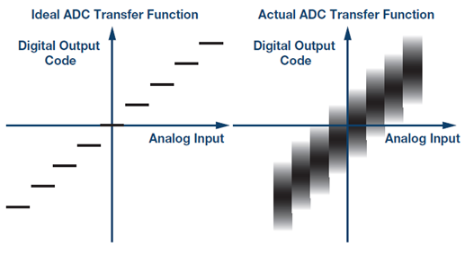

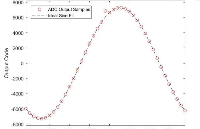

TI 解釋了什么對 ADC 的代碼錯誤率影響最大,它如何影響您的示波器測量,以及如何消除代碼錯誤或閃爍代碼

2022-08-10 15:09:54 433

433

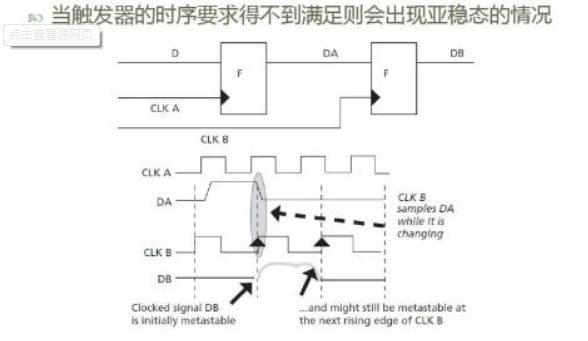

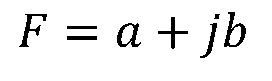

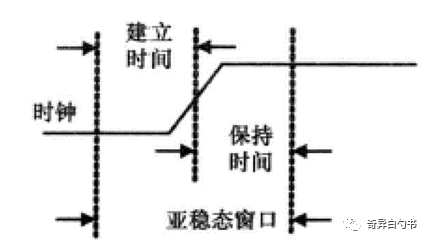

發(fā)生亞穩(wěn)態(tài)的原因是信號在傳輸?shù)倪^程中不能滿足觸發(fā)器的建立時間和保持時間。

2023-06-20 15:29:58 710

710

亞穩(wěn)態(tài)這種現(xiàn)象是不可避免的,哪怕是在同步電路中也有概率出現(xiàn),所以作為設(shè)計人員,我們能做的是減少亞穩(wěn)態(tài)發(fā)生的概率。

2023-08-03 09:04:49 246

246

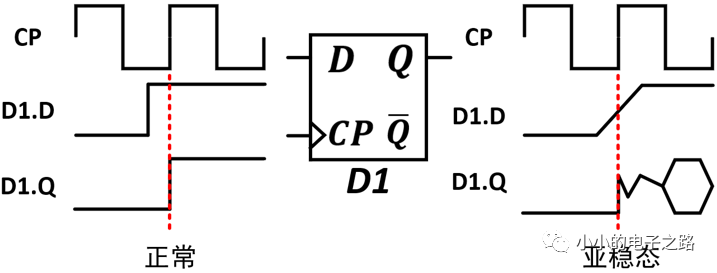

亞穩(wěn)態(tài)是指觸發(fā)器的輸入信號無法在規(guī)定時間內(nèi)達到一個確定的狀態(tài),導(dǎo)致輸出振蕩,最終會在某個不確定的時間產(chǎn)生不確定的輸出,可能是0,也可能是1,導(dǎo)致輸出結(jié)果不可靠。

2023-11-22 18:26:09 1115

1115

亞穩(wěn)態(tài)是數(shù)字電路設(shè)計中最為基礎(chǔ)和核心的理論。同步系統(tǒng)設(shè)計中的多項技術(shù),如synthesis,CTS,STA等都是為了避免同步系統(tǒng)產(chǎn)生亞穩(wěn)態(tài)。異步系統(tǒng)中,更容易產(chǎn)生亞穩(wěn)態(tài),因此需要對異步系統(tǒng)進行特殊的設(shè)計處理。學(xué)習(xí)SoC芯片設(shè)計,歡迎加入啟芯QQ群:275855756

2013-11-01 17:45:15

CC2538+CC2592通信錯誤率很高,什么原因?CC2538+CC2592原理圖就是按照ti給的原理圖設(shè)計的,CC2538連接CC2592,PA_EN接的PC3,LAN_EN接的PC2,HGM接

2016-03-25 11:54:57

`CC254x專有模式包錯誤率測試`

2016-02-25 14:14:13

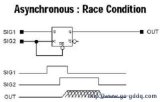

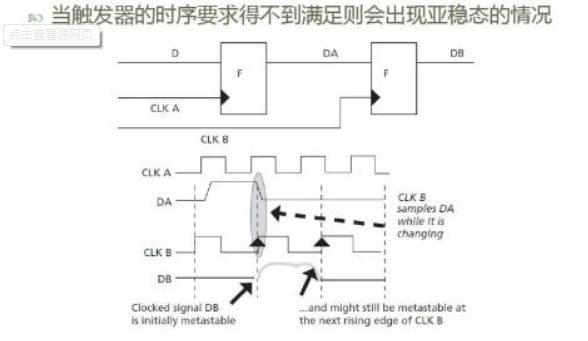

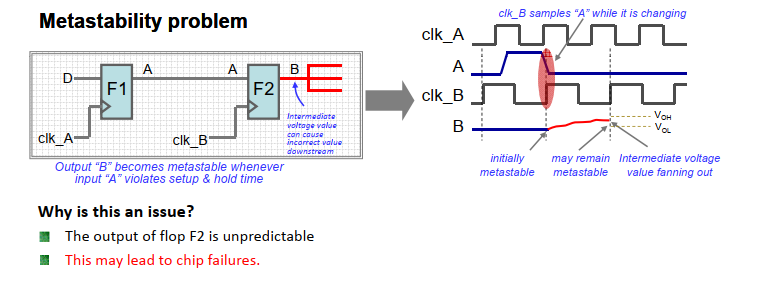

的邏輯是同步邏輯。在一個模塊中不具有相同相位和時間關(guān)系的時鐘被視為不同的時鐘域,其所驅(qū)動的邏輯是異步邏輯。亞穩(wěn)態(tài):如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的建立時間和保持時間,或者復(fù)位過程中復(fù)位信號的釋放相對于有效

2021-07-26 07:03:57

非必要(未使用)位,工具還提供用戶設(shè)計的預(yù)測平均軟錯誤率”。我的問題是:可以使用什么工具來估算XQR4VS??X55??上的設(shè)計的DVF,以及如何估算軟錯誤率。我知道帶有-essentialbits

2019-02-26 10:24:45

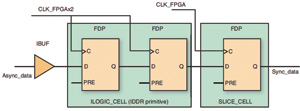

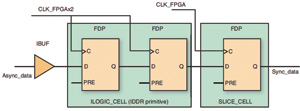

FPGA 設(shè)計需要重視的一個注意事項。理論分析01 信號傳輸中的亞穩(wěn)態(tài)在同步系統(tǒng)中,輸入信號總是系統(tǒng)時鐘同步,能夠達到寄存器的時序要求,所以亞穩(wěn)態(tài)不會發(fā)生。亞穩(wěn)態(tài)問題通常發(fā)生在一些跨時鐘域信號傳輸以及異步

2020-10-22 11:42:16

導(dǎo)致復(fù)位失敗。怎么降低亞穩(wěn)態(tài)發(fā)生的概率成了FPGA設(shè)計需要重視的一個注意事項。2. 理論分析2.1信號傳輸中的亞穩(wěn)態(tài)在同步系統(tǒng)中,輸入信號總是系統(tǒng)時鐘同步,能夠達到寄存器的時序要求,所以亞穩(wěn)態(tài)不會

2012-04-25 15:29:59

注意事項。2. 理論分析2.1信號傳輸中的亞穩(wěn)態(tài)在同步系統(tǒng)中,輸入信號總是系統(tǒng)時鐘同步,能夠達到寄存器的時序要求,所以亞穩(wěn)態(tài)不會發(fā)生。亞穩(wěn)態(tài)問題通常發(fā)生在一些跨時鐘域信號傳輸以及異步信號采集上。它們發(fā)生

2012-01-11 11:49:18

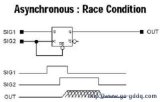

說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時鐘域之間傳輸時導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

2019-09-11 11:52:32

可能會出現(xiàn)非法狀態(tài)---亞穩(wěn)態(tài)。亞穩(wěn)態(tài)是一種不穩(wěn)定狀態(tài),在一定時間后, 最終返回到兩個穩(wěn)定狀態(tài)之一。亞穩(wěn)態(tài)輸出的信號是什么樣子的? 對于系統(tǒng)有什么危害? 如果降低亞穩(wěn)態(tài)帶來的危害? 這是下面要探討

2012-12-04 13:51:18

FPGA項目開發(fā)之同步信號和亞穩(wěn)態(tài)

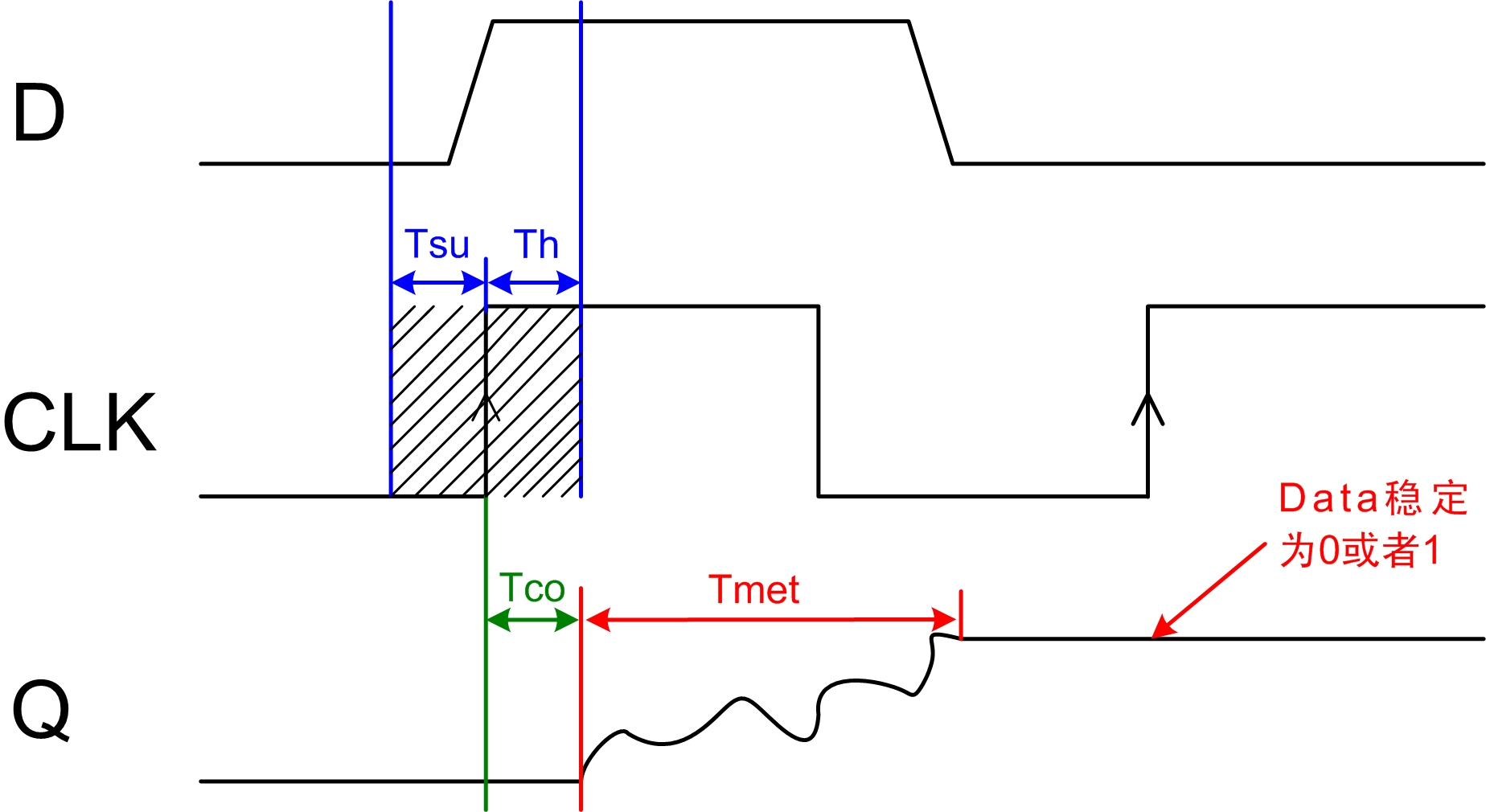

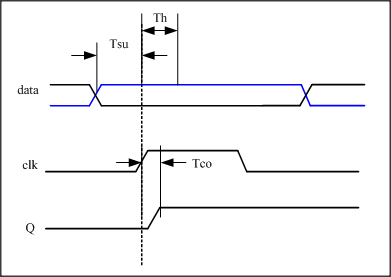

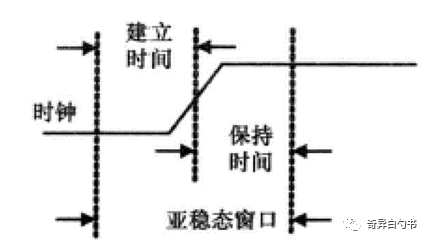

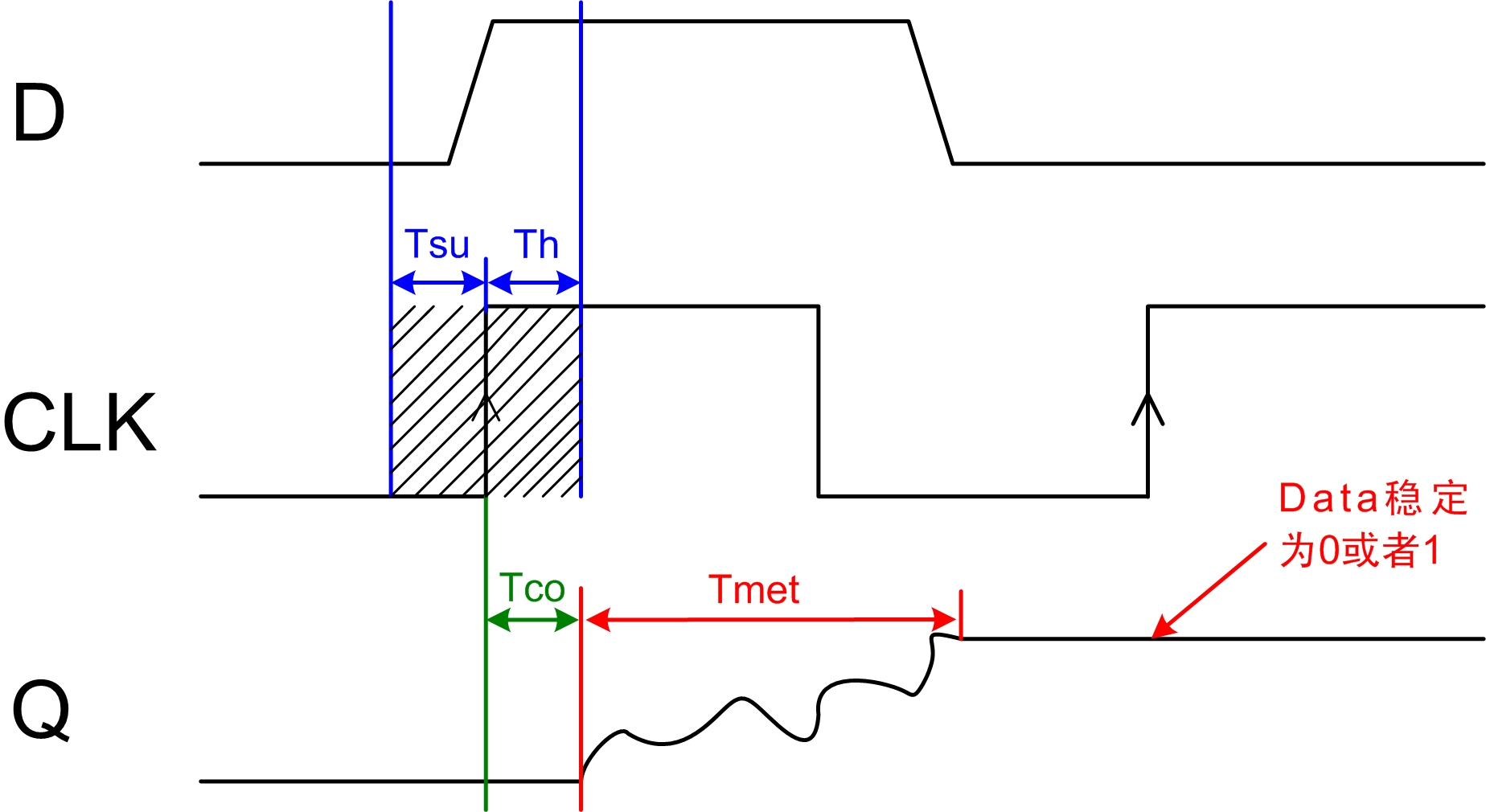

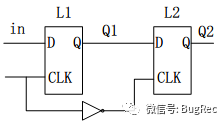

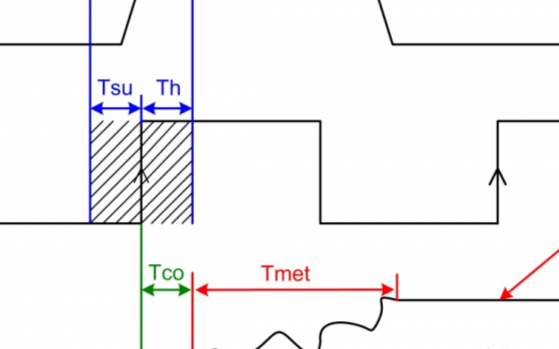

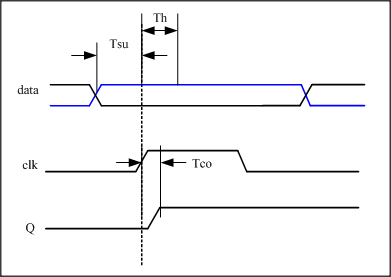

讓我們從觸發(fā)器開始,所有觸發(fā)器都有一個圍繞活動時鐘沿的建立(setup time)和保持窗口(hold time),在此期間數(shù)據(jù)不得更改。如果該窗口中的數(shù)據(jù)

2023-11-03 10:36:15

中找到任何最小數(shù)量的寄存器的建議。我需要有關(guān)同步器鏈長度的任何建議或任何文檔,以便針對Virtex-5器件提供更好的亞穩(wěn)態(tài)保護。我還需要Virtex-6的類似信息。很抱歉,如果這不是此主題的正確論壇。提前致謝,阿姆魯

2020-06-12 09:27:03

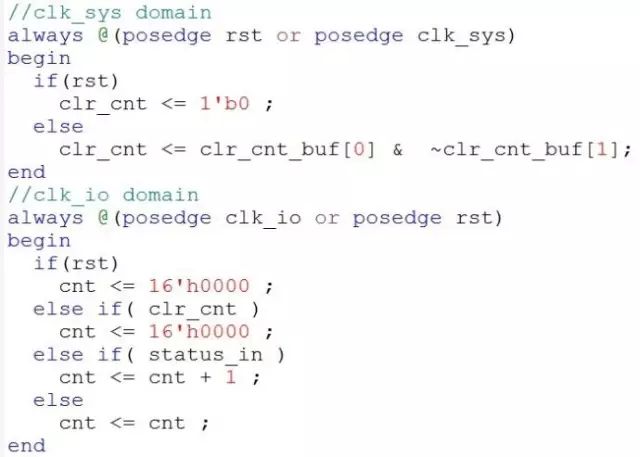

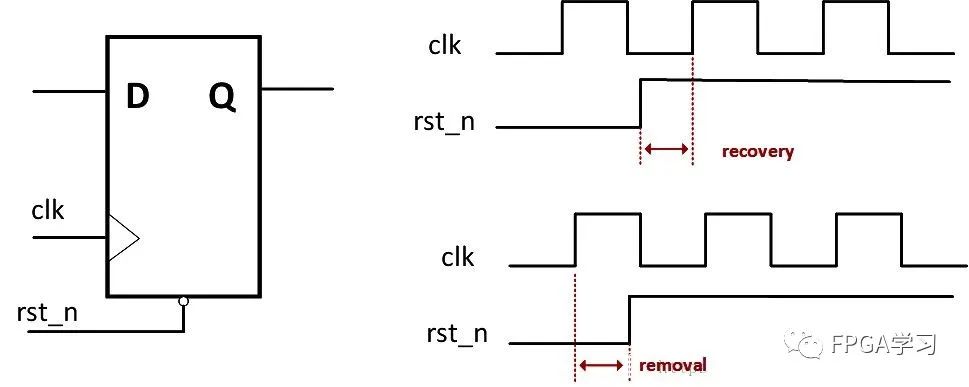

和t2之間的情況。這種情況下,觸發(fā)器CNT[15:0]就會錯誤的采樣到”cnt+1”,而不是期望的hex”0000”值。 忽略次要參數(shù)和亞穩(wěn)態(tài)事件,故障出現(xiàn)的概率可以被估算為 (t2-t1

2012-12-04 13:55:50

的亞穩(wěn)態(tài)事件,結(jié)合實例講解,語言通俗易懂,由淺入深,特別舉了多個實例以及解決方案,非常具有針對性,讓人受益匪淺,非常適合對亞穩(wěn)態(tài)方面掌握不好的中國工程師和中國的學(xué)生朋友,是關(guān)于亞穩(wěn)態(tài)方面不可多得的好資料,強烈推薦哦!!![hide] [/hide]`

2012-03-05 14:11:41

通過獨立按鍵控制LED燈狀態(tài)變化這樣一個實驗,來驗證獨立按鍵消抖是否成功,另外,由于獨立按鍵作為一個外部異步輸入信號,因此借此機會剛好給大家詳細介紹了亞穩(wěn)態(tài)的原理和應(yīng)對策略。希望大家在觀看學(xué)習(xí)時,重點

2015-09-29 14:27:58

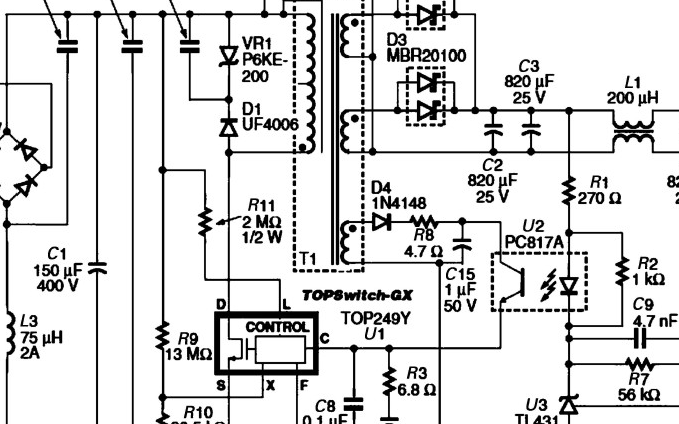

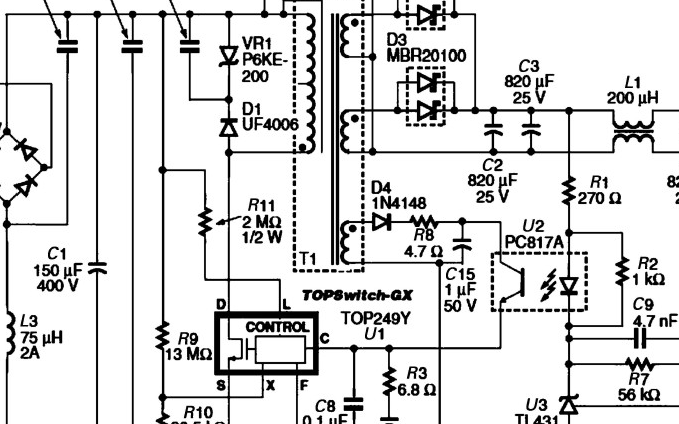

網(wǎng)上看到不對稱半橋后面都是加全波整流,我因為輸出電壓比較高,所以設(shè)計了不對稱半橋加倍壓整流的結(jié)構(gòu),但是在穩(wěn)態(tài)分析的時候搞不清楚了,想問一下后面加全波整流和倍壓整流會影響整個拓撲結(jié)構(gòu)的穩(wěn)態(tài)分析嗎

2020-04-10 20:46:25

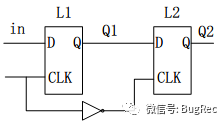

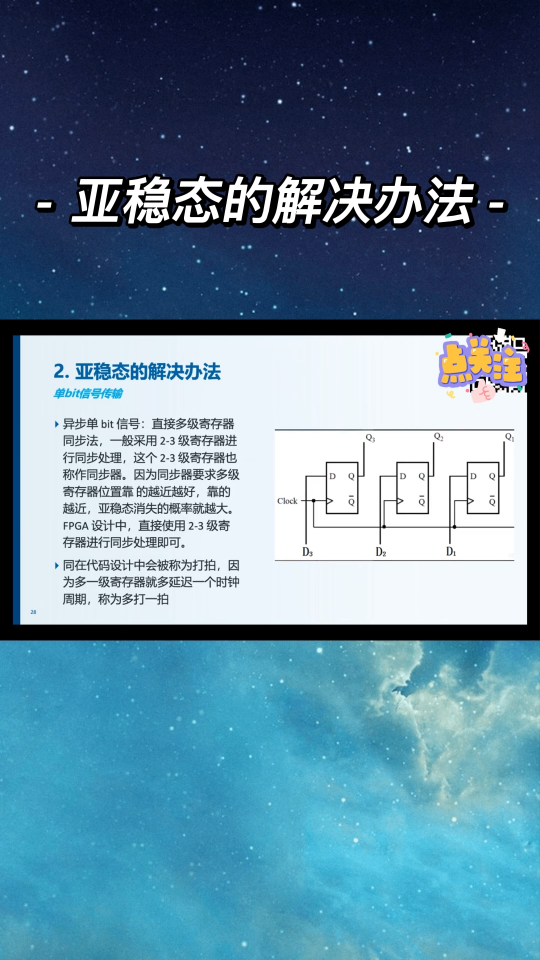

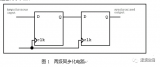

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時間和保持時間?什么是亞穩(wěn)態(tài)?為什么兩級觸發(fā)器可以防止亞穩(wěn)態(tài)傳播?

2021-08-09 06:14:00

的分析一下。

背景

1、亞穩(wěn)態(tài)發(fā)生原因

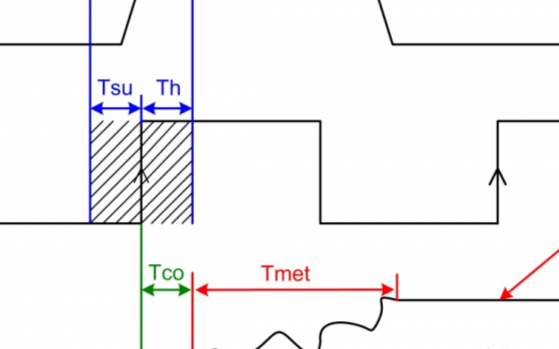

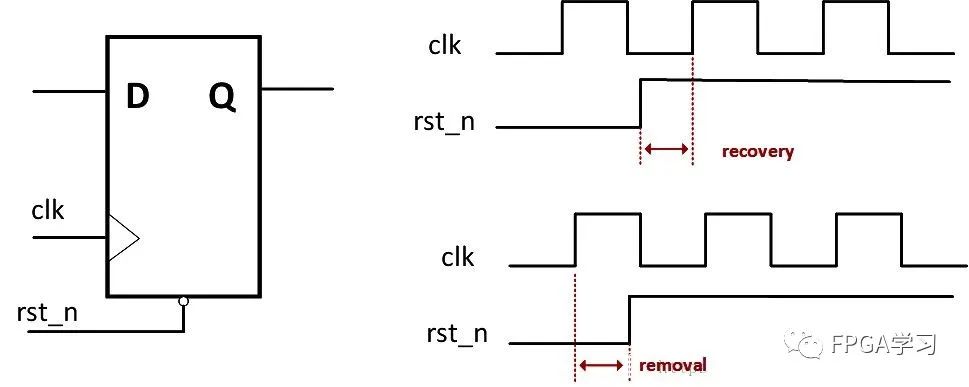

在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過程中復(fù)位信號的釋放相對于有效時鐘沿的恢復(fù)時間(recovery time)不滿足

2023-04-27 17:31:36

的時鐘域時,我們就需要仔細考慮設(shè)計,以確保我們不會違反建立和保持時間并導(dǎo)致亞穩(wěn)態(tài)。當然,無論哪種情況,我們都無法阻止亞穩(wěn)態(tài)事件的發(fā)生,但我們可以確保我們的設(shè)計不會因為亞穩(wěn)態(tài)事件的發(fā)生而出現(xiàn)不正確的數(shù)據(jù)

2022-10-18 14:29:13

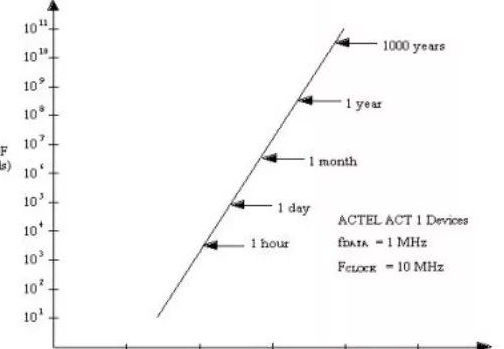

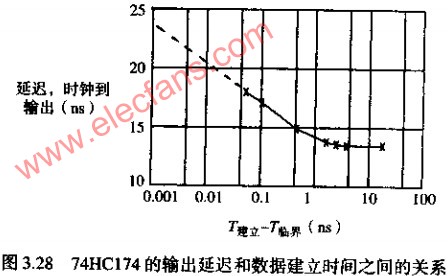

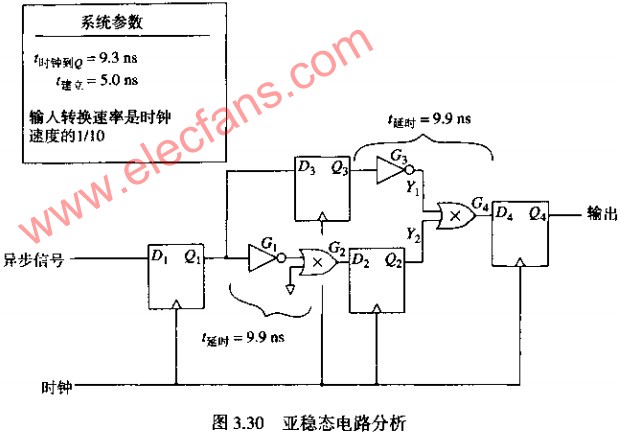

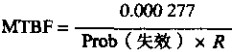

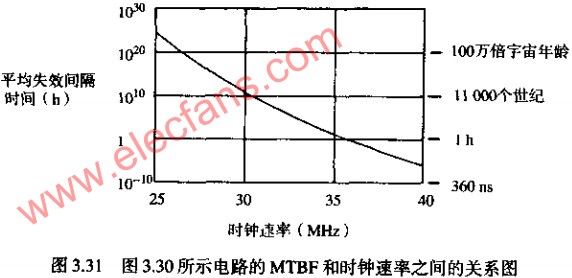

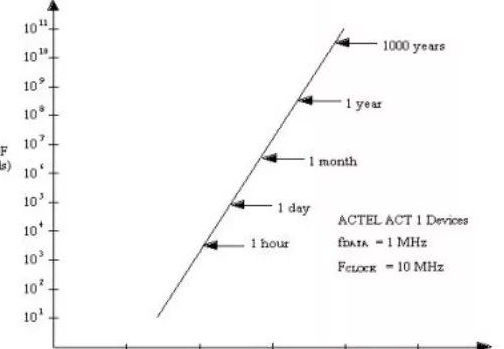

。可用以下方程式計算出寄存器的MTBF:在本例中,C1和C2代表寄存器技術(shù)相關(guān)常數(shù),tMET代表亞穩(wěn)態(tài)的穩(wěn)定時間。可根據(jù)每個寄存器的MTBF,確定總的MTBF值。同步器的故障率為1/MTBF,則將每個

2010-12-29 15:17:55

(50Hz),然后去掉負載(為空載)測量其輸出電壓為整定(400V)。逐級加載,25%、50%、75%、100%(或逐級減載)待穩(wěn)定后,測得輸出電壓,經(jīng)計算得穩(wěn)態(tài)電壓調(diào)整率dU應(yīng)符合要求。&

2010-11-03 16:44:01

的電平值不高也不低,但是此電平不穩(wěn)定,稱為亞穩(wěn)態(tài)(類似于健康和亞健康)。亞穩(wěn)定是不穩(wěn)定的,終究要向高或者低電平進行變化。那么有人說,亞穩(wěn)態(tài)終究會走向穩(wěn)態(tài),那么豈不是沒有影響了。答案是錯誤的。可以想象

2023-02-28 16:38:14

。怎么降低亞穩(wěn)態(tài)發(fā)生的概率成了 FPGA 設(shè)計需要重視的一個注意事項。理論分析01 信號傳輸中的亞穩(wěn)態(tài)在同步系統(tǒng)中,輸入信號總是系統(tǒng)時鐘同步,能夠達到寄存器的時序要求,所以亞穩(wěn)態(tài)不會發(fā)生。亞穩(wěn)態(tài)問題通常發(fā)生

2020-10-19 10:03:17

描述對于存在位錯誤并產(chǎn)生采樣錯誤(也稱為閃碼、字碼錯誤或代碼錯誤)的應(yīng)用,能否測出這些位錯誤導(dǎo)致的錯誤率十分重要。這份基于 FPGA 固件的應(yīng)用手冊建議了一種在無限期時間內(nèi)準確測出這些錯誤的方法

2018-07-24 06:36:26

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的測量。我正在尋找Virtex6和7Series部件的類似亞穩(wěn)態(tài)參數(shù)測量。是否存在應(yīng)用說明?我猜猜V6& 7應(yīng)該比

2020-07-18 16:58:50

你好,我們正在對2個CY3255 DEVICIT之間的通信質(zhì)量進行測試。為了檢查封包錯誤率,我設(shè)置以下寄存器:rx_overwrite = 1,這樣的rx_packet_dropped狀態(tài)標志不會

2019-07-30 09:24:28

微分型單穩(wěn)態(tài)觸發(fā)器的Multisim分析

2012-08-06 13:13:22

,最新研究的研究人員通過改進微軟語音識別系統(tǒng)的神經(jīng)網(wǎng)絡(luò)聲學(xué)和語言模型,將錯誤率降低了約12%。

[img][/img]

值得注意的是,他們還讓自己的語音識別器使用整個對話,讓它根據(jù)上下文調(diào)整

2017-08-23 09:18:35

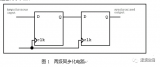

新建兩個D觸發(fā)器的目的是什么?何謂亞穩(wěn)態(tài)?解決亞穩(wěn)態(tài)的方法是什么?

2021-11-09 07:15:01

描述 對于存在位錯誤并產(chǎn)生采樣錯誤(也稱為閃碼、字碼錯誤或代碼錯誤)的應(yīng)用,能否測出這些位錯誤導(dǎo)致的錯誤率十分重要。這份基于 FPGA 固件的應(yīng)用手冊建議了一種在無限期時間內(nèi)準確測出這些錯誤的方法

2022-09-22 06:32:27

說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時鐘域之間傳輸時導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。接下來主要討論在異步時鐘域之間數(shù)據(jù)傳輸所產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象,以及如何降低

2018-08-01 09:50:52

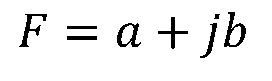

正弦穩(wěn)態(tài)電路分析8.1 正弦量與正弦穩(wěn)態(tài) 8.2 相量變換 8.3電路定律和電路元件的相量形式 8.4 阻抗和導(dǎo)納 8.5正弦穩(wěn)態(tài)電路的分析 8.6正弦穩(wěn)態(tài)

2008-12-04 17:53:07 0

0 非穩(wěn)態(tài)導(dǎo)熱的分析解視頻教程

2009-07-05 19:11:30 18

18

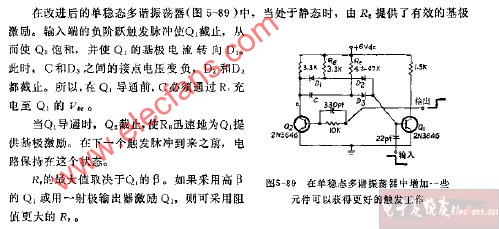

消除了錯誤觸發(fā)的單穩(wěn)態(tài)多諧振蕩器電路圖

2009-06-26 13:38:24 466

466

均勻傳輸線正弦穩(wěn)態(tài)分析

一、長線復(fù)數(shù)方程的推導(dǎo)

在正弦激勵下,沿線各處的電壓、電流在穩(wěn)態(tài)時都

2009-07-27 11:53:53 1148

1148

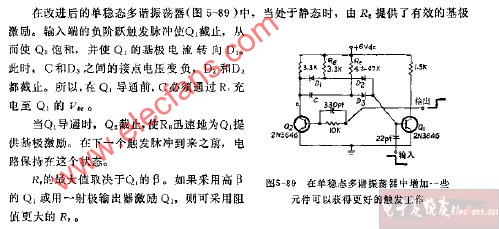

圖3.27所示的是一個觀察D觸發(fā)器亞穩(wěn)態(tài)的電路圖。使用這個電路至少需要一個雙通道示波器。

2010-06-08 14:31:27 1088

1088

什么是亞穩(wěn)態(tài)

在FPGA等同步邏輯數(shù)字器件中,所有器件的寄存器單元都需要預(yù)定義信號時序以使器件正確

2010-11-29 09:18:34 2973

2973

在本文的第一章對跨時鐘域下的同步問題和亞穩(wěn)態(tài)問題做了概述。 在第二章中對時鐘同步需要考慮的基本問題做了介紹。 在第三章中仔細分析了現(xiàn)在常用的幾種同步方法。包括使用G

2011-09-06 15:24:12 42

42 本文分析了異步電路中亞穩(wěn)態(tài)產(chǎn)生的原因和危害, 比較了幾種常用的降低亞穩(wěn)態(tài)發(fā)生概率的設(shè)計方法, 針對這些方法不能徹底消除亞穩(wěn)態(tài)的不足, 設(shè)計了一種消除亞穩(wěn)態(tài)的外部邏輯控制器

2011-10-01 01:56:02 55

55 基于FPGA的亞穩(wěn)態(tài)參數(shù)測量方法_田毅

2017-01-07 21:28:58 0

0 雙饋風(fēng)電機組變流器IGBT結(jié)溫計算與穩(wěn)態(tài)分析_李輝

2017-01-08 11:51:41 6

6 正弦激勵,穩(wěn)態(tài)分析

2017-03-01 13:11:43 0

0 在進行FPGA設(shè)計時,往往只關(guān)心“0”和“1”兩種狀態(tài)。然而在工程實踐中,除了“0”、“1”外還有其他狀態(tài),亞穩(wěn)態(tài)就是其中之一。亞穩(wěn)態(tài)是指觸發(fā)器或鎖存器無法在某個規(guī)定時間段內(nèi)達到一個可確認的狀態(tài)[1]。當一個觸發(fā)器進入亞穩(wěn)態(tài)時,既無法預(yù)測該單元的輸出電平,也無法預(yù)測何時輸出才能穩(wěn)定在某個正確的電平上。

2019-10-06 09:42:00 908

908

亞穩(wěn)態(tài)是指觸發(fā)器無法在某個規(guī)定時間段內(nèi)達到一個可確認的狀態(tài)。當一個觸發(fā)器進入亞穩(wěn)態(tài)時,既無法預(yù)測該單元的輸出電平,也無法預(yù)測何時輸出才能穩(wěn)定在某個正確的電平上。在這個穩(wěn)定期間,觸發(fā)器輸出一些中間級電平.

2017-12-02 10:40:12 42902

42902

通常情況下(已知復(fù)位信號與時鐘的關(guān)系),最大的缺點在于異步復(fù)位導(dǎo)致設(shè)計變成了異步時序電路,如果復(fù)位信號出現(xiàn)毛刺,將會導(dǎo)致觸發(fā)器的誤動作,影響設(shè)計的穩(wěn)定性。同時,如果復(fù)位信號與時鐘關(guān)系不確定,將會導(dǎo)致 亞穩(wěn)態(tài) 情況的出現(xiàn)。

2018-03-15 16:12:00 3330

3330

大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊FPGA學(xué)習(xí)中,亞穩(wěn)態(tài)現(xiàn)象。 說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時鐘域之間傳輸時導(dǎo)致數(shù)字器件失效的一種

2018-06-22 14:49:49 3222

3222

在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過程中復(fù)位信號的釋放相對于有效時鐘沿的恢復(fù)時間(recovery time)不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時觸發(fā)器輸出端Q在有

2018-06-27 10:11:00 9241

9241

本文檔的主要內(nèi)容詳細介紹的是正弦穩(wěn)態(tài)電路的分析,重點內(nèi)容有1.阻抗和導(dǎo)納 2. 正弦穩(wěn)態(tài)電路的分析;3. 正弦穩(wěn)態(tài)電路的功率分析;4.復(fù)功率 5最大功率傳輸

2018-07-25 08:00:00 7

7 亞穩(wěn)態(tài)是指觸發(fā)器無法在某個規(guī)定時間段內(nèi)達到一個可確認的狀態(tài)。

2018-09-22 08:25:00 8718

8718

據(jù)外媒報道,此前谷歌曾表示他們已經(jīng)在語音識別領(lǐng)域獲得了突破,將錯誤率降低到了30%。不過,最近IBM在他們的官網(wǎng)上宣布,他們已經(jīng)創(chuàng)造了自家語音識別的新紀錄,錯誤率僅為5.5%,與去年的6.9%相比又一次的實現(xiàn)了提升。

2019-10-24 10:12:26 741

741 7月,NIST發(fā)布了一份報告,指出口罩正在挫敗常規(guī)的人臉識別算法,錯誤率從5%到50%不等。NIST被廣泛認為是人臉識別準確率測試的權(quán)威機構(gòu),并期望算法能在識別戴著口罩的人方面有所改進。研究發(fā)現(xiàn)

2020-08-28 14:48:00 390

390 如此強調(diào)電子領(lǐng)域的熱條件,邏輯上必須保證特定類型的熱分析。一種這樣的分析形式稱為穩(wěn)態(tài)熱分析,這是我們將要重點關(guān)注的。

2021-02-17 10:31:00 2960

2960 這樣的分析形式稱為穩(wěn)態(tài)熱分析,這是我們將要重點關(guān)注的。 什么是穩(wěn)態(tài)? 在物理學(xué)領(lǐng)域中,穩(wěn)態(tài)是不隨時間變化的穩(wěn)定狀態(tài),或者是一個方向的變化被另一方向的變化連續(xù)平衡的穩(wěn)定狀態(tài)。在化學(xué)中,穩(wěn)態(tài)是指盡管進行中的過程試圖更改它們

2021-01-14 14:56:28 7988

7988 硅作為電腦、手機等電子產(chǎn)品的核心材料,是現(xiàn)代信息產(chǎn)業(yè)的基石。另外硅的多種亞穩(wěn)態(tài)也是潛在的重要微電子材料,其每種亞穩(wěn)態(tài)因其結(jié)構(gòu)的不同而具有獨特的電學(xué)、光學(xué)等性質(zhì),在不同領(lǐng)域都具有重要的應(yīng)用前景。亞穩(wěn)態(tài)

2020-10-17 10:25:26 3001

3001 本文是一篇詳細介紹ISSCC2020會議上一篇有關(guān)亞穩(wěn)態(tài)解決方案的文章,該技術(shù)也使得FPGA在較高頻率下的時序收斂成為了可能。亞穩(wěn)態(tài)問題是芯片設(shè)計和FPGA設(shè)計中常見的問題,隨著FPGA的發(fā)展,時序

2020-10-22 18:00:22 3679

3679

亞穩(wěn)態(tài)概述 01亞穩(wěn)態(tài)發(fā)生原因 在 FPGA 系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的 Tsu 和 Th 不滿足,或者復(fù)位過程中復(fù)位信號的釋放相對于有效時鐘沿的恢復(fù)時間(recovery time

2020-10-25 09:50:53 2196

2196

本文檔的主要內(nèi)容詳細介紹的是正弦穩(wěn)態(tài)電路的分析學(xué)習(xí)課件免費下載包括了:1.阻抗和導(dǎo)納,2電路的相量圖,3正弦穩(wěn)態(tài)電路的分析,4正弦穩(wěn)態(tài)電路的功率,5復(fù)功率,6最大功率傳輸

2020-11-03 17:30:47 17

17 在同步系統(tǒng)中,如果觸發(fā)器的setup time / hold time不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時觸發(fā)器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態(tài),在這段時間里Q端毛刺、振蕩、固定的某一電壓值,而不是等于數(shù)據(jù)輸入端D的值。

2021-03-09 10:49:23 1321

1321

電子發(fā)燒友網(wǎng)為你提供亞穩(wěn)態(tài)的原理、起因、危害、解決辦法資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-30 08:45:27 9

9 電子發(fā)燒友網(wǎng)為你提供什么是亞穩(wěn)態(tài)資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-16 08:43:07 24

24 今天寫一下時序問題常見的跨時鐘域的亞穩(wěn)態(tài)問題。 先說明一下亞穩(wěn)態(tài)問題: D觸發(fā)器有個明顯的特征就是建立時間(setup time)和保持時間(hold time) 如果輸入信號在建立時間和保持時間

2021-06-18 15:28:22 2683

2683 正弦電路的穩(wěn)態(tài)分析:用相量法分析動態(tài)電路在正弦激勵下的穩(wěn)態(tài)響應(yīng)。

2021-06-19 16:12:10 1

1 亞穩(wěn)態(tài)的概念 亞穩(wěn)態(tài)是指觸發(fā)器無法在某個規(guī)定時間段內(nèi)達到一個可確認的狀態(tài)。當一個觸發(fā)器進入亞穩(wěn)態(tài)引時,既無法預(yù)測該單元的輸出電平,也無法預(yù)測何時輸出才能穩(wěn)定在某個正確的電平上。在這個穩(wěn)定期間,觸發(fā)器

2021-07-23 11:03:11 3928

3928

什么問題。 亞穩(wěn)態(tài) 我們都知道數(shù)字電路中有兩個最重要的概念,建立時間和保持時間。通過滿足建立時間和保持時間,我們可以確保信號被正確的采樣,即1采到便是1,0采到便是0。但是如果不滿足建立時間和保持時間,采到的信號會進入一個不穩(wěn)定的狀態(tài),無法確定是1還是0,我們稱之

2021-08-25 11:46:25 2087

2087 電路分析基礎(chǔ)第五章正弦電路的穩(wěn)態(tài)分析課件下載

2022-02-11 09:09:42 0

0 可能很多FPGA初學(xué)者在剛開始學(xué)習(xí)FPGA設(shè)計的時候(當然也包括我自己),經(jīng)常聽到類似于”這個信號需要打一拍、打兩拍(寄存),以防止亞穩(wěn)態(tài)問題的產(chǎn)生“這種話,但是對這個打拍和亞穩(wěn)態(tài)問題還是一知半解,接下來結(jié)合一些資料談下自己的理解。

2022-02-26 18:43:04 6004

6004

亞穩(wěn)態(tài)問題是數(shù)字電路中很重要的問題,因為現(xiàn)實世界是一個異步的世界,所以亞穩(wěn)態(tài)是無法避免的,并且亞穩(wěn)態(tài)應(yīng)該也是面試常考的考點。

2022-09-07 14:28:37 367

367 亞穩(wěn)態(tài)問題是數(shù)字電路中很重要的問題,因為現(xiàn)實世界是一個異步的世界,所以亞穩(wěn)態(tài)是無法避免的,并且亞穩(wěn)態(tài)應(yīng)該也是面試常考的考點。

2022-09-07 14:28:00 7116

7116 亞穩(wěn)態(tài)是我們在設(shè)計經(jīng)常遇到的問題。這個錯誤我在很多設(shè)計中都看到過。有人可能覺得不以為然,其實你現(xiàn)在沒有遇到問題只能說明。

2022-10-10 09:30:10 596

596 即使 “打兩拍”能阻止“亞穩(wěn)態(tài)的傳遞”,但亞穩(wěn)態(tài)導(dǎo)致后續(xù)FF sample到的值依然不一定是符合預(yù)期的值,那 “錯誤的值” 難道不依然會向后傳遞,從而造成錯誤的后果嗎?

2022-10-19 14:14:38 602

602 元器件在現(xiàn)實運行時,觸發(fā)器輸出的邏輯0/1需要時間跳變,而不是瞬發(fā)的。因此,若未滿足此cell的建立時間、保持時間,其輸出值則為中間態(tài),那在logic上可能算成0也可能算成1很難講(波形顯示上可能是毛刺、振蕩、固定值等),這就是亞穩(wěn)態(tài)。

2022-10-19 14:13:47 1474

1474 一個不穩(wěn)定的狀態(tài),無法確定是1還是0,我們稱之為亞穩(wěn)態(tài)。這個亞穩(wěn)態(tài)的信號會在一段時間內(nèi)處于震蕩狀態(tài),直到穩(wěn)定,而穩(wěn)定后的狀態(tài)值與被采樣值無關(guān),可能是0也可能是1。

2022-12-12 14:27:52 652

652 犯錯是人之常情。但是,對于您系統(tǒng)的模數(shù)轉(zhuǎn)換器(ADC),可以提出哪些要求?我們將回顧高速ADC的轉(zhuǎn)換錯誤率(CER)測試和分析范圍。ADC CER測量過程可能需要數(shù)周或數(shù)月才能完成,具體取決于采樣

2023-02-28 15:54:34 422

422

相量法是線性電路正弦穩(wěn)態(tài)分析的一種簡易方法。

2023-03-09 11:35:59 3876

3876

看的東西多了,發(fā)現(xiàn)有些并未領(lǐng)會到位。單bit信號的跨時鐘域傳輸,可以使用兩級同步,但后果呢?

重復(fù)一下亞穩(wěn)態(tài),違反觸發(fā)器的時序特性,可能導(dǎo)致觸發(fā)器的輸出進入亞穩(wěn)態(tài),亞穩(wěn)態(tài)不在0和1的電壓范圍內(nèi)。數(shù)字電路的功能體現(xiàn)在0和1上,亞穩(wěn)態(tài)可能導(dǎo)致功能錯誤

2023-05-11 16:24:07 380

380

本系列整理數(shù)字系統(tǒng)設(shè)計的相關(guān)知識體系架構(gòu),為了方便后續(xù)自己查閱與求職準備。對于FPGA和ASIC設(shè)計中,D觸發(fā)器是最常用的器件,也可以說是時序邏輯的核心,本文根據(jù)個人的思考歷程結(jié)合相關(guān)書籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-05-12 16:37:31 1345

1345

亞穩(wěn)態(tài)在電路設(shè)計中是常見的屬性現(xiàn)象,是指系統(tǒng)處于一種不穩(wěn)定的狀態(tài),雖然不是平衡狀態(tài),但可在短時間內(nèi)保持相對穩(wěn)定的狀態(tài)。對工程師來說,亞穩(wěn)態(tài)的存在可以帶來獨特的性質(zhì)和應(yīng)用,如非晶態(tài)材料、晶體缺陷

2023-05-18 11:03:22 2583

2583 前面在時序分析中提到過亞穩(wěn)態(tài)的概念,每天學(xué)習(xí)一點FPGA知識點(9)之時序分析并且在電路設(shè)計中如果不滿足Tsu(建立時間)和Th(保持時間),很容易就出現(xiàn)亞穩(wěn)態(tài);在跨時鐘域傳輸?shù)囊幌盗写胧┮彩菫榱私档?b class="flag-6" style="color: red">亞穩(wěn)態(tài)發(fā)生的概率。

2023-05-25 15:55:43 885

885

點擊上方 藍字 關(guān)注我們 1.1 亞穩(wěn)態(tài)發(fā)生原因 在 FPGA 系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足 觸發(fā)器 的Tsu和Th不滿足,或者復(fù)位過程中復(fù)位信號的釋放相對于有效時鐘沿的恢復(fù)時間(recovery

2023-06-03 07:05:01 1007

1007 本文主要介紹了亞穩(wěn)態(tài)的分析與處理。

2023-06-21 14:38:43 2073

2073

CPLD規(guī)模雖小,其原理和設(shè)計方法和FPGA確是一樣的。輕視在CPLD上的投入,就有可能存在設(shè)計隱患,導(dǎo)致客戶使用產(chǎn)品時出現(xiàn)故障,從而給公司帶來不可挽回的信譽損失。

2023-06-27 15:14:17 217

217

本系列整理數(shù)字系統(tǒng)設(shè)計的相關(guān)知識體系架構(gòu),為了方便后續(xù)自己查閱與求職準備。對于FPGA和ASIC設(shè)計中,D觸發(fā)器是最常用的器件,也可以說是時序邏輯的核心,本文根據(jù)個人的思考歷程結(jié)合相關(guān)書籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-07-25 10:45:39 556

556

隨著高速模數(shù)轉(zhuǎn)換器(ADC)采樣率的提高,ADC輸出數(shù)據(jù)中的代碼錯誤(也稱為閃爍代碼)問題也隨之增加。代碼錯誤定義為ADC輸出代碼中的錯誤超過定義的閾值。閾值通常定義為誤差超過ADC噪聲預(yù)期幅度

2023-08-17 15:09:24 578

578

亞穩(wěn)態(tài)(Metastability)是由于輸入信號違反了觸發(fā)器的建立時間(Setup time)或保持時間(Hold time)而產(chǎn)生的。建立時間是指在時鐘上升沿到來前的一段時間,數(shù)據(jù)信號就要

2023-09-19 09:27:49 360

360

說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時鐘域之間傳輸時導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

2023-09-19 15:18:05 1050

1050

復(fù)位信號存在亞穩(wěn)態(tài),有危險嗎? 復(fù)位信號在電子設(shè)備中起著重要的作用,它用于使設(shè)備回到初始狀態(tài),以確保設(shè)備的正常運行。然而,我們有時會發(fā)現(xiàn)復(fù)位信號存在亞穩(wěn)態(tài),這意味著信號在一定時間內(nèi)未能完全復(fù)位

2024-01-16 16:25:56 113

113 兩級觸發(fā)器同步,就能消除亞穩(wěn)態(tài)嗎? 兩級觸發(fā)器同步可以幫助消除亞穩(wěn)態(tài)。本文將詳細解釋兩級觸發(fā)器同步原理、亞穩(wěn)態(tài)的定義和產(chǎn)生原因、以及兩級觸發(fā)器同步如何消除亞穩(wěn)態(tài)的機制。 1. 兩級觸發(fā)器同步

2024-01-16 16:29:38 252

252

電子發(fā)燒友App

電子發(fā)燒友App

評論