隨著通信產業尤其是移動通信的高速發展,無線電頻譜的低端頻率已趨飽和。采用各種調制方法或多址技術擴大通信系統的容量,提高頻譜的利用率,也無法滿足未來通信發展的需求,因而實現高速、寬帶的無線通信勢必向微波高頻段開發新的頻譜資源。毫米波由于其波長短、頻帶寬,可以有效地解決高速寬帶無線接入面臨的許多問題,因而在短距離無線通信中有著廣泛的應用前景。各種半導體器件是信息和通信技術(ICT )的硬件基礎,創造性研發滿足毫米波無線通信應用的新興半導體技術和電路,是提升通信系統容量、解決構建新一代通信系統關鍵問題的主要技術推手。文章沿著毫米波半導體器件技術創新發展脈絡,從相控陣等關鍵技術的系統架構、半導體材料和工藝、器件設計和封裝測試入手,分析總結了第五代(5G )、第六代( 6G )移動通信技術毫米波系統和器件技術發展趨勢。以美國 DARPA 的 MIDAS 計劃為例,闡釋了軍用毫米波器件技術的研究前沿和進展。

信息時代通信技術所面臨的主要問題就是解決海量數據生成與通信容量不足之間的矛盾。預計到2032 年,每年約有 45 萬億個傳感器從物理世界中采集巨量模擬信息(等價于 ?) 。現有通信網絡系統遠遠不能滿足未來對信息傳輸容量的需求。解決現有無線通信系統數據傳輸速率低下與信息高生成率之間的巨大差距問題,成為無線通信技術發展的關鍵點。當前主要解決方法之一是每隔幾年引入一個新的無線標準來定義新協議,即采用更復雜的調制方案,以增加數據吞吐量。然而,調制復雜度增加到某種程度不再能顯著提高吞吐量,創造新的解決方案已經成為當務之急。

?) 。現有通信網絡系統遠遠不能滿足未來對信息傳輸容量的需求。解決現有無線通信系統數據傳輸速率低下與信息高生成率之間的巨大差距問題,成為無線通信技術發展的關鍵點。當前主要解決方法之一是每隔幾年引入一個新的無線標準來定義新協議,即采用更復雜的調制方案,以增加數據吞吐量。然而,調制復雜度增加到某種程度不再能顯著提高吞吐量,創造新的解決方案已經成為當務之急。

著名的香農 - 哈特利( Shannon - Hartley )定理指出,通信系統的容量與帶寬呈線性函數關系。為了快速傳輸更多的數據,理論上可以采用另一種更為長效的 提 高 系 統 吞 吐 量 的 方 法,即 將 調 制 信 號(FBW )擴展到更寬的頻率范圍內來增加其帶寬,當前無線通信的發展主要就是遵循這一思路。目前蜂窩網絡的許可運行頻段主要在 6GHz 頻率以下,可用頻譜受到一定限制。順應趨勢要求,運行頻譜向更高頻段拓展是必然的。毫米波頻段(一般指30~300GHz電磁波頻段)無線通信具有頻譜寬和較強有效視距通信能力,能夠大幅提高帶寬、數據傳輸率,以及降低端到端延時,實現通信容量的大幅提升,因而獲得了越來越多的關注。更多毫米波高端頻段(一般指 >6GHz頻段)被使用,毫米波產業鏈也快速發展起來。

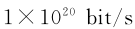

一般認為第五代移動通信技術(5G )將部署電磁頻譜的毫米波頻段,第六代移動通信技術(6G )將開發利用太赫茲(0.1~10THz )頻段。5G和6G 回程數據容量從10Gbit / s增加到100Gbit/ s ,只能通過壓縮更高調制格式的數據,以在毫米波模式下工作,如圖1所示 ?,這里更高的工作帶寬是可用的。達到這一目的的主要技術途徑就是進行半導體技術創新,開發毫米波、太赫茲頻段工作的半導體器件、材料和架構。一些在軍事應用中采用多年的關鍵技術已經成為5G 電信的理想技術。例如,相控陣技術是具有良好發展前景的重點技術。5G 電信正致力實現防務行業利用相控陣天線所帶來的益處,克服毫米波信號容易受阻于建筑物或者障礙物的缺點。軍事應用面臨更為復雜的通信環境,距離通常相隔幾十公里甚至幾百海里。系統容量、數據傳輸速率同樣也是軍用通信系統所追求的關鍵指標。毫米波相控陣在軍用通信、雷達、電磁頻譜戰領域的發展意義重大。軍用和民用5G 通信建立起的良性循環有利于形成相互利用和促進的局面。

圖 1 商用無線數據服務速率每十年增加十倍的毫米波技術趨勢

1

毫米波技術趨勢

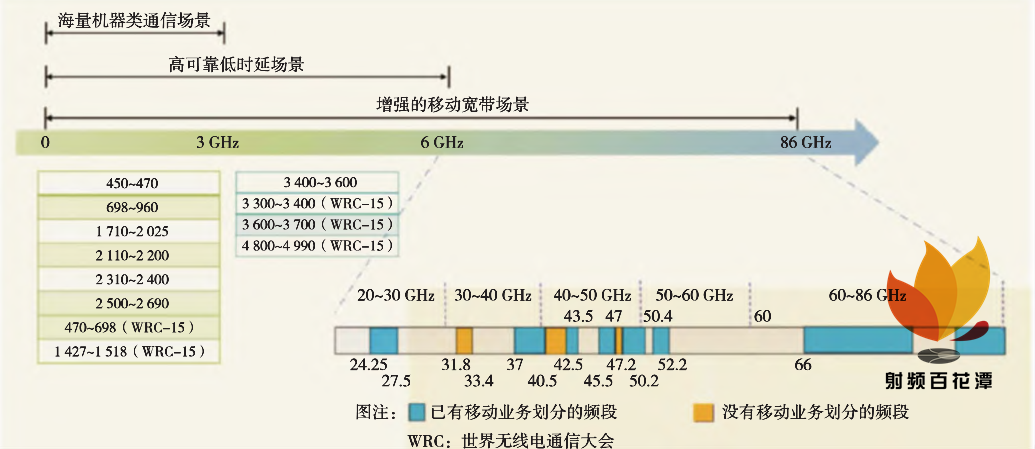

從當前 國 際 5G 技 術 發 展 來 看,主 要 國 家 6GHz以下頻段已經全面實現商用。無線通信要實現更高的數據容量或更高帶寬,主要的著力點是開發利用24.25GHz以上頻段的毫米波高頻段。在2019年世界無線電通信大會( WRC - 19 )上,基于國際電信聯盟(ITU )、第三代合作伙伴計劃( 3GPP )等國際標準化組織框架,各國代表就 5G 毫米波頻譜使用達成共識:全球范圍將24.25~27.5GHz 、 37~43.5GHz 、 66~71GHz共14.75GHz帶寬的毫米波頻率標識用于5G 及國際移動通信系統( IMT )的未來發展。WRC - 19的決議規劃了大量連續帶寬的毫米波頻率用于 5G 技術 ,如圖 2 所示。這為 5G/6G相關產業鏈的發展和成熟奠定了基礎,全球5G系統部署和商用步伐正在加速。

半導體工業的關鍵挑戰是開發并提供可賦能給5G 、 6G 信息傳輸網絡的技術,增加信息傳輸吞吐量、覆蓋空間和傳輸距離。這些需求將轉化成對半導體器件射頻和基帶帶寬、工作頻率、功耗、增益、噪聲系數、線性度、發射功率等性能指標的要求。除最可能優先部署的26GHz / 28GHz/ 39GHz頻段之外,近年業界對工作在 V 波段( 57~66GHz )、 E 波段(71~86GHz )和 W 波段( 75-110GHz )的半導體技術給予越來越多的關注。高于90GHz和高達300GHz的頻段也已經開始開發。6G 網絡通信頻段將向上擴展至太赫茲頻段并延伸到三維空間,可連接衛星、飛機、船舶和陸基基礎設施,實現真正的全球覆蓋智能化通信 ?。

圖 2 5G 關鍵場景對應頻譜分布

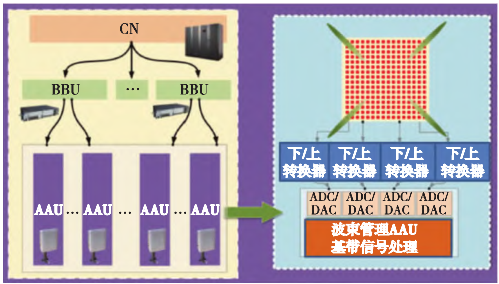

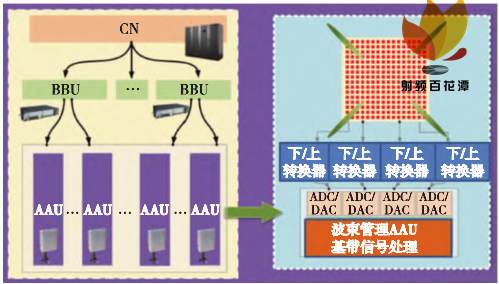

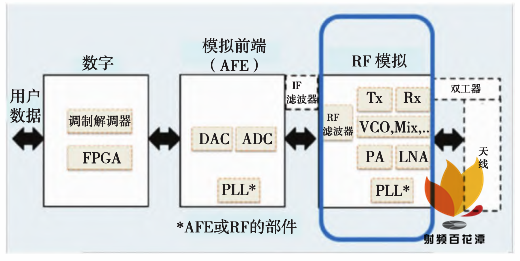

新一代毫米波無線通信系統技術主要包括工作于毫米波頻段的大規模 MIMO 系統架構、波束成形芯片、基站( BS )和用戶終端(UT )的天線、系統測量和校準技術以及無線信道表征。通信基站是移動通信網絡中最關鍵的基礎設施。圖 3 所示為核心網( CN ) 5G 毫 米 波 基 站 基 帶 單 元 - 有 源 天 線 單 元(BBU - AAU )架構的示意圖。該基站主要完成新空口( NR )基帶信號與射頻信號的轉換及NR 射頻信號的收發處理功能。

圖 3 一種 5G 毫米波基站架構示意圖

發射信號時,從 5G 基帶單元傳來的基帶信號,經過上變頻、 D / A 轉換以及射頻調制、濾波、信號放大等發射鏈路( TX )處理后,再由開關、天線單元發射出去。接收信號時,5G射頻單元通過天線單元接收射頻信號,經過低噪放、濾波、解調等接收鏈路( RX )處理后,再進行 A / D 轉換、下變頻,轉換為基帶信號并發送給 5G 基帶單元 。

2

毫米波波束成形系統構成

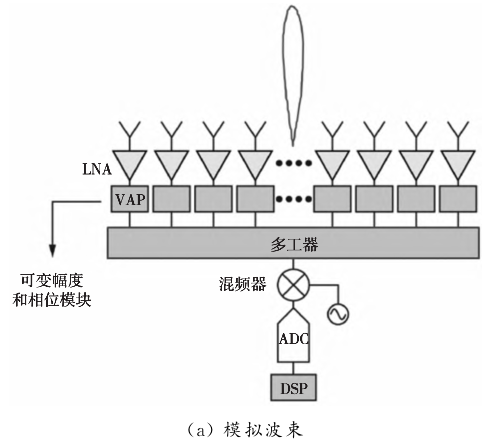

根據每個天線元件的相位,5G無線波束成形按系統架構分為三種類型:模擬波束成形 ?、全數字波束成形和混合波束成形 ?。

2.1 模擬和數字波束成形架構

基于相控陣的模擬波束成形在模擬域內進行相位移動。模擬波束成形系統分為三個模塊:數字模塊、位到毫米波模塊和波束成形模塊。根據模擬移相的位置,可以將移相分為中頻移相?、本地振蕩器移相和射頻移相。采用數字控制移相器(如6 位 移 相 器)或 靜 態 模 擬 波 束 成 形 結 構 (如Butler矩陣?、Blass矩陣和 Lenses?)來實現相移。圖 4 ( a )所示為射頻波束成形接收機的一種架構,來自天線元件的信號經過加權和合并,產生一個波束,然后由混頻器和信號鏈其余部分加以處理。這是相控陣的傳統實現方式。優勢是實現成本較低、部署簡便,缺點是較難產生多波束。

數字波束成形的原理是:每個元件單元的信號在獨立數字化后,完全在數字電路中實現相移,結構如圖3(b )所示,通過收發器陣列饋送到天線陣列。全數字相控陣是最有發展前途的架構。每個天線單元被連接到一個獨立的高速、高精度 A /D轉換器( ADC)或 D/ A 轉換器( DAC )上。若選用低分辨率的 ADC / DAC ,則能大幅降低功耗。數字移相系統里所有的信號流都被數字化,因而數字波束成形具有快速波束管理和波束成形等優點,可以同時創建多個波束或在所有方向上進行搜索,并對障礙具有魯棒性。

圖4模擬和數字波束成形架構比較示意圖

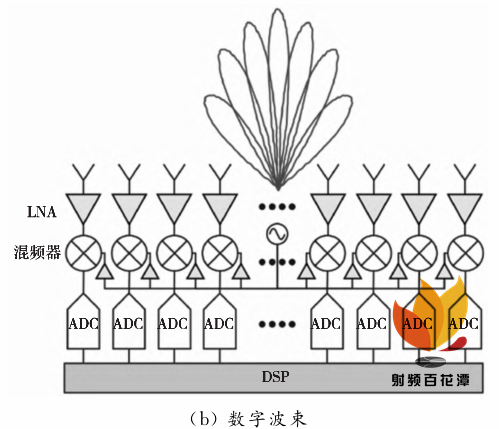

2.2 混合波束成形架構

混合波束成形( HBF )是模擬和數字波束成形技術的結合 ?,是兩者組合一個中間方案,如圖5所示,是權衡成本/硬件復雜性和系統性能的方案。方案之一是將陣列劃分為更小的子陣列,并在子陣列內執行模擬波束成形。每個子陣列可被認為是具有某種定向輻射圖形的超級元件。然后使用來自子陣列的信號執行數字波束成形,產生對應于陣列全孔徑的高增益窄波束。混合波束成形是目前5G 無線通信系統的主流方案。

圖 5 多個模擬波束的混合波束成形示意圖

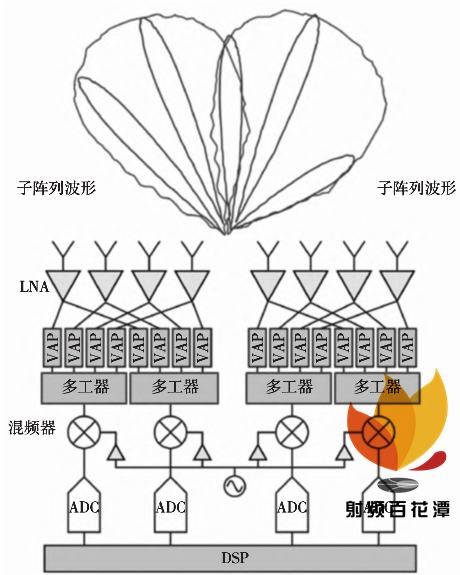

2.3 功能模塊和電子組件

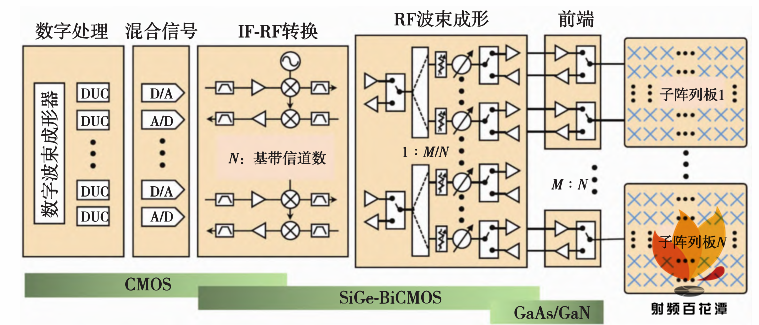

圖6所示為用于5G 的天線模塊配置和每個功能塊宜采用的半導體技術方案 ?。有各種構建相控陣的功能塊和半導體技術方案。最右邊的天線陣列接收到的信號由前端低噪聲放大器放大。然后,它們的信號位在射頻波束成形器內被調整和合成。合成的信號從射頻頻率轉換為中頻。再通過ADC轉換為數字信號,進行信號處理。另一方面,數字部分產生的信號通過 DAC 轉換為模擬信號,并轉換為無線電頻率。然后,它們被射頻波束成形器分割成相位調整信號,由前端的功率放大器放大后從陣列天線發射。

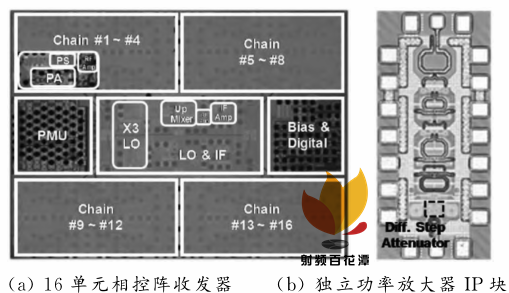

射頻集成電路( RFIC )是重要的一類組件。東京工業大學和 NEC公司開發了一種由4個發射/接收電 路 ( TRX )組 成 的 RFIC ,采 用 65nm 體 硅CMOS技術制作 ?。這種 RFIC 具有將信號從中頻 - 射頻轉換到前端的功能,并通過改變本振信號相位來修改射頻信號相位,使IC小型化。三星公司開發了一種 RFIC ,具有將信號從中頻 - 射頻轉換到射頻前端的 16 個 平行傳 輸信道,采用 28nm 體硅CMOS技術制作,如圖7所示 ?。IBM 和愛立信使用SiGe BiCMOS技術聯合開發了一種 RFIC ,具有如圖6所示的從中頻 - 射頻( IF - RF )轉換到前端的功能 ?。這個RFIC采用一個實時延遲電路作為移相器,它 有 32TRX 和 很 好 的 波 束 成 形 性 能。MixComm 開發了一種 8TRX RFIC ,采用 45nmPD - SOI技術,電路具有射頻波束成形器和前端功能 。通過垂直堆疊增加 SOI上功率放大器的輸出,以補償晶體管柵極尺寸微化造成的輸出功率下降。已經使用 GaAs 、GaN 材料開發用于5G 毫米波的具有良好高頻特性的 RFIC 。但只能用于研制功率放大器、低噪聲放大器等模擬電路。目前還無法用這些技術創建數字電路。

圖 6 使用混合波束成形的毫米波相控陣的簡化框圖

圖 7 16 信號鏈路 RFIC 芯片布局

3

毫米波半導體技術研究進展

通過半導體技術創新發展有效提升信息傳輸和處理效率的系統性解決方案,需要從材料、工藝、系統和電路設計、封裝與測試、軟件等方面著手開展協同研究。

3.1 材料技術

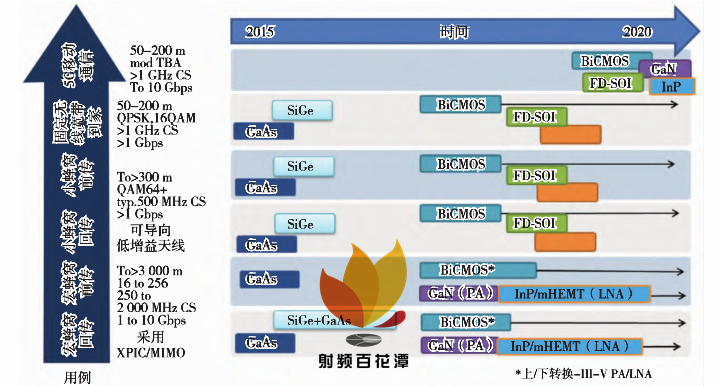

推動未來通信技術發展創新的半導體工藝平臺包括 RFSOI 、 FinFET 、基于 SOI / SiGe 的光電技術。材料技術處于半導體技術革新的中心。毫米波電路只有從基礎材料出發不斷創新,才能不斷提升工作頻率并滿足不同應用場景的要求,如圖8所示。主流模擬IC / RFIC半導體材料包括如下內容。

1 ) Ⅲ - Ⅴ 化 合 物。目 前 主 要 采 用 GaAspHEMT 和 InGaP HBT 制作電路。以 GaN 為代表的寬禁帶化合物材料正在崛起。GaN 的熱導率與Si 相當,但其擊穿電壓非常高,具有比 Si 更高的電子遷移率、更高的功率增益、更低的噪聲和更高的功率效率,非常適合于制作毫米波系統的功率放大器、低噪聲放大器、低相位噪聲振蕩器等前端電路。

圖8 主要的半導體材料和器件發展路線圖

2 )Si基材料。目前主要采用 CMOS和SiGe/BiCMOS ,易實現高集成度和高性價比,是制作小功率器件的優選材料。與 CMOS平面體硅工藝兼容的全耗盡SOI ( FDSOI )工藝是在低電壓下提供高頻工作的一種非常有前景的技術。文獻提出了一種基于FDSOI 器件的毫米波波束成形系統,在高整體功率效率下實現SOC集成。SiGe BiCMOS在單芯片中集成了高性能雙極晶體管和 CMOS 器件,達到 GaAs等更昂貴工藝才能實現的性能。

3 )多材料異構集成。Ⅲ - Ⅴ 與Si共集成技術出現了兩種不同的集成方法,即與CMOS兼容的 GaN工藝?和硅基 Ⅲ - Ⅴ 族晶圓級集成技術 ?,兩者都是在 200 毫 米 硅 晶 圓 上 進 行。前 者 利 用 現 有 的CMOS 基礎設施,使用 Ⅲ - Ⅴ 芯片和 Si 芯片混合封裝形成最終系統,而后者是采用與現有的 Si 代工工藝兼容的工藝,將 Ⅲ - Ⅴ 器件和 Si器件共同集成在一個芯片中。二者都是引人注目的研究方向?。

3.2 工藝技術

許多代工廠轉向比電子束光刻更具成本效益的光學光刻,開發出新的工藝技術來參與5G 芯片工藝競爭;或者將新功能集成到單個工藝節點中,降低成本,獲取價格優勢。圖 9 顯示了在 5G 中應用的Si 技術演變歷史。在 28GHz 和 39GHz 頻段的新興 5G 毫米波蜂窩應用中,有兩種引人注目的硅基技術——— 28nm RFCMOS 和 130nm /90nm SiGeBiCMOS 。多篇文獻詳細介紹了 28nm 節點 CMOS技術 以及該節點技術中器件的射頻特性? 。

這種平面技術采用了 gen - 4nFET應變結構和浸入式光刻 技 術。就 柵 極 處 理 工 藝 而 言,存 在 Poly/SiON 和高 k 金屬柵極 (HKMG )的處理方式,即HKMG工藝,該技術能提供更好的 I on 和 g m ,同時降低 柵 極 電 阻 R g。研 究 還 表 明,28nm 體 硅CMOS技術能夠實現用于802.11ac的高級SOC集成收發器和25Gbit/ s 60GHz寬帶數字功率放大器,并達到合理的射頻前端性能。

圖 9 在 5G 中應用的 Si 技術演變歷史

SiGe BiCMOS 應用于 WiFi 前端、遠程汽車雷達、光學IC 和5G 毫米波基站。在 BiCMOS技術下,通常將 SiGe HBT 添加到較大尺寸的 CMOS 節點中,并仔細優化技術的其他方面,如 HBT 、布線和襯底損耗,以最大化應用效益。例如,350nm SiGeBiCMOS 仍然足以滿足極具挑戰性的 WiFi 前端功率放大器( PA )需求 。SiGe BiCMOS 將作為未來在 100GHz 以上毫米波應用的重要基礎技術之一。

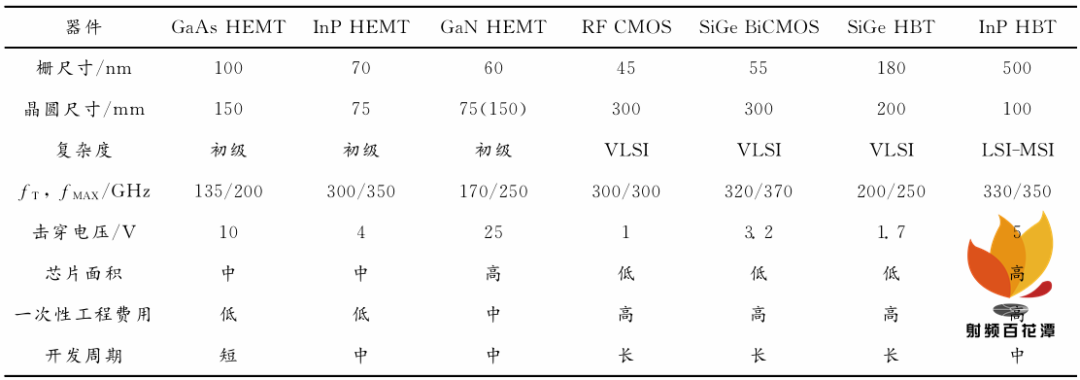

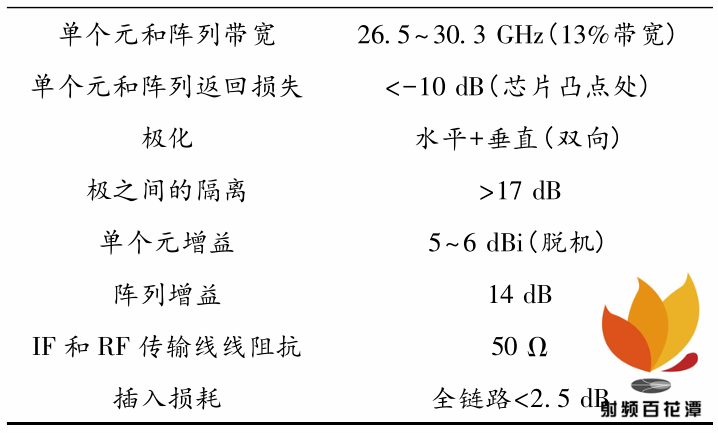

在商業應用中,每種半導體技術在性能和集成水平方面的潛力,必須與工藝的成熟度、芯片組在各種應用 市場規 模 背 景 下 被 開 發 的 潛 在 投 資 回 報( ROI )相平衡。出于這個原因,技術的選擇應在性能、系統復雜性和成本指標之間折中考慮,如表 1 所示。

表 1 毫米波半導體技術在性能、集成水平和開發成本方面的比較

3.3 IC 設計技術

隨著新工藝的推出,IC設計也在不斷演進。IC設計人員通過在單個工藝節點中提供新功能,將某些功能組合到一個產品中,或者從核心晶體管中開發比以前更高的性能。這些趨勢最終導致芯片的集成度提高,并且更易于部署,如圖10所示。毫米波相控陣系統設計的兩個關鍵挑戰是發射機的功率效率和整個系統的熱功率預算。若采用Si技術設計系統,則系統之間的差異將主要由功率放大器 工 作 點 的 最 大 功 率 輸 出 ( P sat )、功 率 效 率(PAE )以及天線和發射機/接收機之間的損耗造成。

圖 10 毫米波半導體系統主要電路示意圖

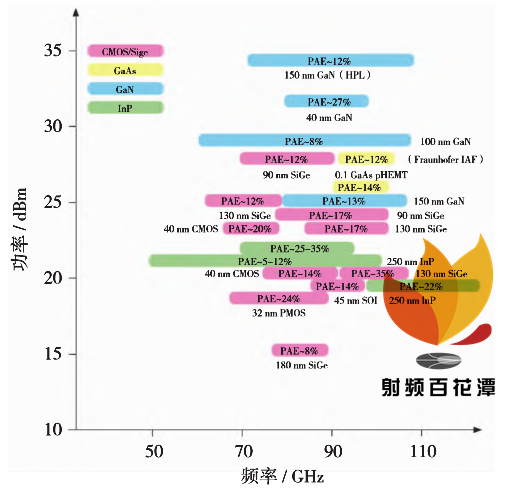

波束成形架構和芯片劃分將由等效全向輻射功率( EIRP )、頻帶和系統中消耗的直流功率決定。SOC的面積縮放與耗散的熱功率密度之間存在折中。在所有 PA 器件中, GaN 以最高的發射功率、最高的PAE (如圖 11 所示)、最寬的帶寬、最大的功率密度和最高的可靠性脫穎而出?。面臨的主要挑戰是晶格失配電荷在阱中的填充與釋放時間常數差異導致的矢量幅度退化( EVM )。此外,還未能證明這些器件是否能在 120GHz以上頻率工作。今后的研究將致力于將 GaN 器件和 PA 的工作頻率擴展到200GHz ,功率達 40dBm@30%PAE 。隨著向更高的毫米波頻段邁進,挑戰將更加嚴峻。

圖11在毫米波頻率下工作的幾種技術的附加功率效率比較

毫米波器件設計要重點考慮的關鍵半導體器件要素包括高頻技術、能優化片上射頻無源元件的低損耗后段工藝、考慮了布線相關性影響的先進建模和仿真能力,以及基于傳輸線的器件和交叉耦合。一般認為,取 f max 或者 f T 的 1 / 3 作為工作的頻率上限,可以容忍工藝、電壓和溫度的變化,同時還能保持足夠的增益。對于Si CMOS器件,由于柵極和互連電阻造成的各種限制,微縮到 20nm 以下對器件性能的改善收效甚微,f max 可能于20nm 左右達到450GHz的峰值?。CMOS電路適宜小信號射頻應用,已被證明能在100GHz范圍支持毫米波技術 。與CMOS相比,SiGe在高溫下具有更高的頻率、更高的擊穿電壓和更高的輸出功率。IHP已經演示了 DOT750器件?的 fmax 達到700GHz,器件性能遠高于 CMOS?。

3.4 封裝與測試

在過去幾年中,射頻應用推動先進電子封裝市場涵蓋了不同行業。隨著汽車雷達、高端智能手機、WiGig 器件等產品的出現,RF 封裝市場預計將在各個領域都有所增長。預計 2025 年射頻高級封裝市場將達到 340 億美元 ?。晶圓級封裝(WLP )、 3D硅通孔( TSV )、系統封裝(SiP )和電磁干擾( EMI)屏蔽是射頻器件要求小尺寸、高速運行和異構集成的關鍵因素。在毫米波頻段優化基于 SiP 的封裝技術是通信集成電路面臨的主要挑戰之一。需要研究新的管理散熱或電氣性能的封裝和制造技術。智能手對功耗、尺寸和集成度有著苛刻的要求,基站要求的嚴格程度則相對較小。成本效率也是至關重要的因素。

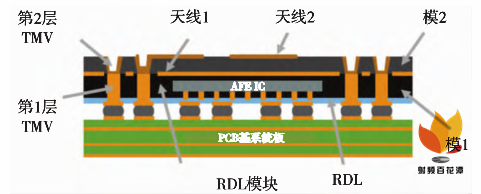

毫米波 5G 需要能夠實現用于大規模 MIMO的寬帶( >400MHz )陣列的高度小型化的大型天線新封裝技術。歐洲共同利益重要項目(IPCEI )正在為 毫 米 波 5G 基 站 應 用 開 發 出 晶 圓 級 封 裝(FOWLP )的天線封裝模塊。圖 12 所示為該封裝的示意圖?,顯示一種雙模堆疊的 FOWLP RDL( RDL即導線重新分布層)芯片后裝工藝。兩個銅層(天線2和天線1 )分別包括一個集成天線陣列和它的地平面,而兩個封裝層(模2和模1 )分別作為天線襯底和插板層。采用 Globalfoundries 22FDX技術制成的模擬前端 IC ( AFE IC )被集成到插板層,通過堆疊層的通孔與天線連接,并通過 RDL與系統板連接 。封裝尺寸為10mm×10mm ,集成天線陣列包括一個2×2的貼片天線。器件在28GHz和39GHz雙頻段運行,兩個頻段最小阻抗帶寬均為400MHz 。

圖 12 雙模 FOWLP 封裝結構圖

毫米波測試包括對系統、 RF 電路、數字電路、新材料(包括一些在最先進工藝節點上開發的材料)、新封裝方法、天線陣列、 SiP 、天線級封裝(AiP )以及毫米波獨有的空口( OTA )測試。毫米波測試才剛剛起步,電路復雜度高、工藝接入點多,測試、檢測和計量需要耗費更長時間。MIMO 的性能在真實環境或隔離環境中測量。測量真實的室內或室外環境中的傳播信道特性用于獲得每個特定MIMO信道的脈沖響應。它提供了有關被測系統的完整知識,但僅針對一個特定場景。第二種 MIMO 測量是在隔離環境中進行的,即 OTA 測試。OTA 測試是毫米波關鍵要素。文獻描述了不同的 OTA 方法,提出了 28GHz 和 39GHz 相控陣天線及其 IC的 OTA 測試解決方案。

4

軍用毫米波數字相控陣研究前沿

4.1 技術路線

軍事應用對毫米波技術有著強烈的需求。通信、雷達中的相控陣天線等毫米波關鍵技術首先在軍事領域得到發展,現在已經轉變為5G 通信的主流技術,二者相互促進,實現良性循環。軍用毫米波技術聚焦數字相控陣前沿技術研究,從應用層面大致有以下三個關聯方向。

1 )更遠距離寬帶傳輸。美國國防高級項目研究局( DARPA)的 MIDAS 計劃正在開發用于通信和遙感的 18~50GHz 高集成度單元級數字相控陣 ?。MIDAS最終目標是開發出能實現快速移動戰術平臺之間的安全通信網絡天線孔徑,以更快的速度和帶寬更遠地傳輸數據。諾格公司與 DARPA在“100Gbit / s射頻主干網絡”項目中驗證了在20公里距離上 100Gbit / s 的無線數據傳輸能力 ?。鏈路在毫米波頻率上(71~76GHz和81~86GHz )運行,帶寬達5GHz 。

2 )更高分辨率和小型化。公開資料顯示,國外戰機雷達多工作在 X 頻段(8GHz至12GHz ),部署和瞄準導彈的雷達系統通常在 Ka頻段(33GHz至37GHz )。更高分辨率和更小尺寸的天線有助于性能提升。94GHz頻段導彈正在開發。

3 )向高頻擴展頻率覆蓋范圍。傳統電子戰系統運行于2GHz 至 18GHz 之間,涵蓋 S 波段、C 波段、 X波段和 Ku波段。隨著探測距離的增加,偵聽電子 設 備 也 將 增 加。由 于 工 作 在 28 GHz 和 39GHz頻率的5G 設備可能與用于導彈制導的 Ka頻段重疊,為了減少信道沖突,電子戰系統提出了新的擴展頻率覆蓋范圍———從24GHz到44GHz 。帶寬增加和頻率提高將有利于開發更多的性能更高的軍用電子設備。

4.2 重點目標

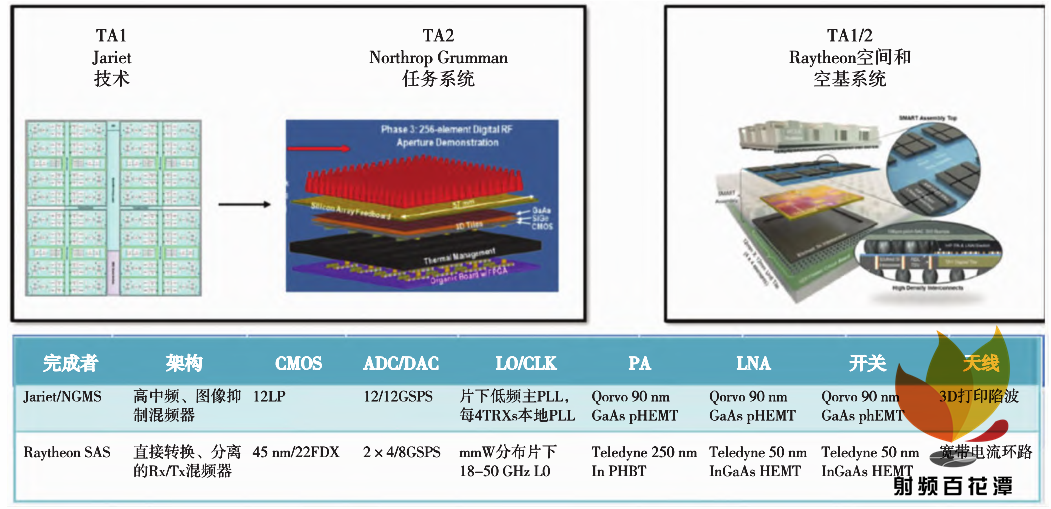

DARPA MIDAS 計劃目的是開發毫米波頻率的單元級數字波束成形陣列,實現頻率敏捷的多波束網絡,減少網絡發現時間,并提高網絡吞吐量。項目將把先進射頻和混合信號 CMOS ASIC 設計、化合物半導體器件和異構集成方面的研究進展結合在一起,研制用于航空航天和國防應用的薄型數字相控陣。技術領域 1 ( TA1 )(計劃研制時間 2018 年 ~2021 年):研 制 寬 帶 毫 米 波 數 字 “瓦 片”。除 了 在TA1 中開發這個核心構建模塊之外,還開發 T / R組件,包括低噪聲放大器( LNA )、 PA 、 T / R 開關和輻射元件,同時開發封裝和熱管理基礎設施、用于數字波束成形的計算資源。項目完成目標是多于 256個單元的樣機系統。技術領域 2 ( TA2 )(計劃研制時間 2018年 ~2022年):利用 TA1團隊開發的“瓦片”研制寬帶毫米波孔徑。技術領域3 ( TA3 )(計劃研制時間2018年 ~2021年):毫米波陣列基礎研究,解決數字和混合波束成形中的基礎技術創新。

4.3 研究進展

Northrop Grumman和Jariet技術公司合作開發 MIDAS項目中的18~50GHz可擴展數字相控陣,其 他 參 研 公 司 包 括 Qorvo 、 Micross 、 TowerSemiconductor和 Protolabs 。MIDAS參研公司分工圖如圖13所示。NorthropGrumman計劃用裸芯片3D 堆疊和 TSV 垂直互連實現異構集成。堆疊器件包括3D 打印的輻射器、兩個為輻射器創建平衡結構的硅饋電板、一個砷化鎵 T / R MMIC層、一個 SiGe RFIC 層和一個 CMOS 瓦片層。數據和電源從 硅 中 TSV 進 入 CMOS ,輸 出 信 號 則 進 入SiGe BiCMOS RFIC 。該 RFIC為 GaAs MMIC提供偏置分配、控制、測試和校準射頻分配。砷化鎵T / R MMIC層是8信道四分之一圓片,它通過倒裝芯片鍵合與 SiGe IC 互連, SiGe IC 是砷化鎵 T / RMMIC層和 CMOS瓦片之間的有源插接器。第二階段中,由 Jariet設 計 的 TA1 數 字 瓦 片 將 取 代CMOS瓦片,并與陣列的其他部分集成。還需要研究多種合金性質、鍵合和溫度特性,保證組裝過程穩定。

TA1混合信號 ASIC由Jariet公司開發,采用Global Foundries 公 司 12 nm FinFET ( 12LP )CMOS工藝,在數字和模擬/射頻性能之間取得了良好平衡,是一種極其省電和緊湊的混合信號和數字設計方案。高效的邏輯對于實現數字降頻/升頻器 ( DDC / DUC )模塊,以及數字波束成形功能十分重要。為了實現具有8個收發器通道的四分之一“測試瓦片”方案,采用了 6GHz 的高 - 中頻頻率范圍,且 ADC 在第二奈奎斯特區的采樣率為 8GS / s 。發送路徑采用 DAC ,使用回補( RTC )或混合模式波形,在第二奈奎斯特區將信號能量最大化。雖然第一階段目標是達到200MHz帶寬,但Jariet的數據轉換器設計實現了4GHz的奈奎斯特帶寬,從而減輕了實現第二階段目標的難度。

迄今為止,參研公司已經使用兩個不同的最先進CMOS工藝、3D 打印寬掃描和寬帶輻射器、 InPHBT / HEMT和 GaAs pHEMT低噪聲放大器和高功率放大器、低損耗 T / R 開關,開發了多信道收發器 ASIC 。Northrop Grumman為 TA2孔徑研究采用了凹槽天線陣列,它們是用立體光刻技術( SLA )3D打印的,然后進行銅金屬化。開發了使用芯片堆疊、銅柱、焊接凸點和分布層的先進封裝技術,將所有組件集成在管殼中。完成樣機將是一個可擴展的256 個天線單元的毫米波天線“瓦片”相控陣,達到在戰術防御平臺和低軌衛星中使用大型相控陣進行通信的目標。

圖 13 MIDAS 參研公司分工圖

5

總 結

建設下一代高速泛在、集成互聯、智能綠色、安全可靠的大容量通信網絡將依賴于半導體技術創新和突破的推動作用。毫米波無線通信是實現信息和通信技術長期可持續發展的重要技術,目前正在艱難地攻克前所未有的技術挑戰。這些挑戰在很大程度上源于半導體技術發展正在逼近其基本極限,這為信息處理、通信、存儲、傳感和驅動所賴以維系的能源效率的更新換代帶來了阻礙。我國毫米波技術發展應該形成在政府支持下的、以應用為導向的產學研各界共同努力的局面,充分利用多學科研究成果,開展包括基礎研究的各種研究,在系統、材料、架構、電路、器件和軟件領域協同開發,取得突破性進展,最終達到期望的發展目標。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論