引言

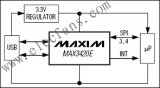

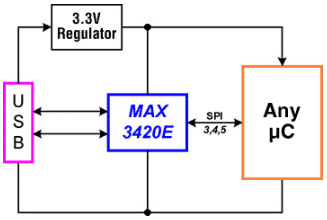

MAX3420E可與任何SPI主控制器相連,構成全速USB外設器件。盡管由MAX3420管理底層USB信令,但是需要處理USB事件時,SPI主控制器必須參與處理。MAX3420的INT引腳指示有中斷發生,SPI主控制器讀取14個中斷請求位,確定需要服務的中斷。主要由這些中斷請求(IRQ)位確定MAX3420E的工作過程。

注意:SPI主控制器可以是微控制器、DSP、ASIC或者任何具備SPI端口的器件,并能提供SCLK信號。本文檔使用的術語“SPI主控制器”和“微控制器”含義相同。

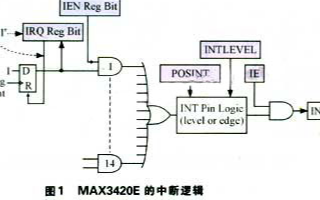

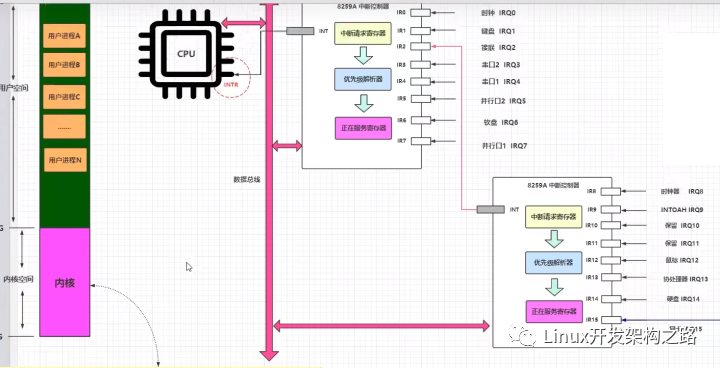

MAX3420E中斷邏輯

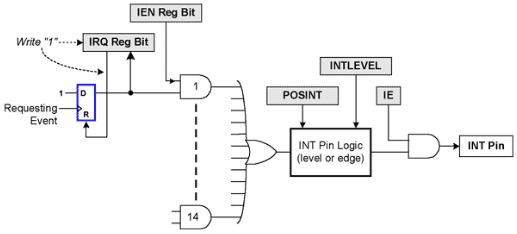

圖1. MAX3420E中斷邏輯。陰影部分為寄存器位。

圖1所示為MAX3420E中斷邏輯。陰影部分是可通過SPI訪問的寄存器位。

IRQ位

每一個中斷源都有一個用于鎖存服務請求的觸發器。觸發器的輸出即為IRQ,它出現在MAX3420E寄存器中。IRQ位提供兩種功能:

- 讀取一個IRQ位,將返回IRQ觸發器的狀態。

- 寫入一個“1”至IRQ位,將清除IRQ觸發器,寫入“0”至IRQ位,不改變觸發器狀態。

圖2. 清除通用寄存器位需要一次RMW操作

由于SPI主控制器通過寫1來清除一個MAX3420E IRQ位,而寫0不改變其他寄存器位,因此SPI主控制器可以直接寫入位屏蔽值來清除URESIRQ位。所以,圖2中的最后三條語句可以由圖3中的單條語句替代。

圖3. 用一次寄存器寫操作來清除MAX3420E IRQ位

IEN位

14個MAX3420E中斷的每一個都有相應的中斷使能(IEN)位。IEN位和IRQ觸發器輸出進行“與”操作,決定是否向INT引腳傳送中斷請求(圖1)。14個IRQ觸發器通過門控電路后,進行“或”操作,形成一個內部中斷請求信號,傳送至中斷引腳邏輯模塊。

注意,無論IEN位的狀態如何,IRQ位都指示中斷懸掛狀態。這樣,即使中斷不觸發INT引腳,固件仍可以檢查該懸掛中斷。如果您的程序需要檢查一個IRQ寄存器“是否懸掛中斷”,一個簡單的方法是讀取IRQ和IEN寄存器,對它們進行“與”操作,檢查現在指示“等待和被使能的IRQ”位。零值表示沒有使能的中斷處于懸掛狀態。

IE位

SPI主控制器通過IE位使能或者禁止INT引腳。由于該位影響到所有的中斷,因此通常稱之為全局中斷使能。不論IRQ或者IEN位的狀態如何,當IE = 0時,INT引腳無效。

中斷引腳邏輯

兩個寄存器位INTLEVEL (參考下面的討論)和POSINT控制INT引腳的工作方式。在設置IE = 1之前,應先設置這兩個配置位。

電平模式,INTLEVEL = 1

某些微控制器系統使用低電平有效中斷。采用這種配置時,MAX3420E采用一個開漏極晶體管驅動INT引腳至地。由于引腳只能驅動為低電平,因此,需要在INT引腳和邏輯電源之間接一個上拉電阻。該模式支持多個芯片的INT引腳輸出(每個均為開漏輸出)連接在一起,并使用單個上拉電阻。由于任何一個芯片輸出都可將該引腳拉低,因此這種邏輯有時也稱為“線或”。對于這種類型的系統,設置INTLEVEL = 1。

邊沿模式,INTLEVEL = 0 (缺省值)

MAX3420E INT引腳也可以驅動邊沿有效的中斷系統,此時微控制器在其中斷輸入引腳上檢查0-1或者1-0跳變。這是MAX3420E的缺省模式,INTLEVEL = 0。SPI主控制器通過第二個POSINT位設置邊沿極性。當POSINT = 1時,MAX3420E為懸掛中斷輸出一個0-1跳變。當POSINT = 0 (缺省值)時,MAX3420E為懸掛中斷輸出一個1-0跳變。

在圖1中,請注意以下幾方面:

- 如果一個IRQ位置位,而其對應的IEN位清零,則IRQ不會影響INT輸出引腳。但是,中斷仍處于懸掛狀態。永遠可以讀取IRQ位以獲得其狀態,可向對應的寄存器位寫1,將IRQ位清零。

- 懸掛中斷(IRQ位是1)的IEN位出現0-1跳變時將產生中斷

- INT引腳可連接至微控制器的中斷系統。此外,微控制器可以輪詢INT引腳,以確定MAX3420E是否有中斷處于懸掛狀態。最適合輪詢的模式是電平模式(INTLEVEL = 1),這是因為在邊沿模式中,INT引腳輸出的脈沖可能太窄,微控制器無法探測到(參考下面的討論)。請注意,電平模式需要在INT引腳和VL之間連接一個上拉電阻。

INT引腳波形

電平模式

圖4. 電平模式下MAX3420E INT引腳的變化(INTLEVEL = 1)

圖4所示為電平模式下的MAX3420E INT引腳波形。INT引腳靜態為高電平(上拉至VL)。假設圖中兩個中斷的IEN位置為1,全局IE位置為1,那么將出現以下事件。(下面標有字母的條目對應圖4中相同字母標出的事件。)

- 發生一個中斷請求,使MAX3420E INT引腳置低。

注意:盡管MAX3420E中斷輸出引腳被稱為INT引腳,它有時也是負極性(例如在電平模式下)。

- SPI主控制器完成中斷服務后,向IRQ位寫入1,將其清零。INT引腳返回至靜態高電平。(a)和(b)之間的間隔是中斷置位其IRQ位和SPI主控制器清除IRQ位之間的時間。

- 產生另一個中斷請求,將INT引腳拉低。

- 當第一個中斷請求處于懸掛狀態時,產生了第二個中斷請求。INT電平沒有變化,因為至少有一個中斷處于懸掛狀態。(實際上,此刻有兩個中斷處于懸掛狀態。)

- SPI主控制器完成一個中斷服務后,向IRQ位寫入1,將其清零。由于仍有一個中斷處于懸掛狀態,INT引腳保持低電平。

- SPI主控制器處理完剩下的中斷請求,向IRQ位寫入1,將其清零。沒有中斷處于懸掛狀態,因此INT引腳返回至靜態高電平。

注意:如果一個中斷的IRQ觸發器(圖1)置位,則認為該中斷處于懸掛狀態。

這種邏輯可以很好地處理INT引腳輪詢。如果MAX3420E的任何部分需要服務,并且其中斷已被使能,那么INT引腳變為低電平。在微控制器清除最后一個懸掛IRQ位之前,INT引腳一直保持低電平。

邊沿模式

圖5. 邊沿模式下MAX3420E INT引腳的變化(INTLEVEL = 0)。間隔(1)是SPI主控制器清除IRQ的時間,間隔(2)是10.67μs。

圖5所示為兩種極性邊沿模式下的MAX3420E INT引腳波形,極性由POSINT位控制。波形與電平模式的相似,但有兩處不同。在兩種條件下,INT引腳產生邊沿跳變:

- 一個IRQ位變為有效狀態(其IRQ觸發器產生0-1跳變)。

- 處理器清除一個IRQ位(向其寫入1),其他IRQ處于懸掛狀態。

除了產生邊沿跳變外,與電平模式一樣,INT引腳也具有有效和無效狀態。INT引腳的無效狀態取決于POSINT位設置的邊沿極性。在這點上,邊沿模式與電平模式相似,查看INT引腳的狀態就可以知道是否有中斷處于懸掛狀態:

- 在負極性邊沿模式下,如果沒有懸掛中斷,INT引腳為高電平;如果有懸掛中斷,則為低電平。

- 在正極性邊沿模式下,如果沒有懸掛中斷,INT引腳為低電平;如果有懸掛中斷,則為高電平。

- 產生一個中斷請求時,MAX3420E INT引腳出現一個邊沿跳變。邊沿的極性取決于POSINT位的設置。由于中斷仍處于懸掛狀態,INT引腳保持其有效狀態。

- SPI主控制器完成中斷服務后,向IRQ位寫入1,將其清零。MAX3420E INT引腳返回至無效狀態。圖中(a)和(b)之間的間隔(1)是產生中斷和SPI主控制器清除IRQ位之間的時間。

- 產生另一個中斷請求時,MAX3420E INT引腳產生一個邊沿跳變,并保持其有效狀態。

- 當第一個中斷請求處于懸掛狀態時,又產生了第二個中斷請求。MAX3420E INT引腳必須產生另一個邊沿跳變,因此該引腳在無效和有效狀態之間產生跳變脈沖,從而提供正確的邊沿極性。在MAX3420E中,該脈沖的寬度固定為10.67μs。由于還有中斷處于懸掛狀態,INT引腳保持在有效狀態。

- SPI主控制器完成一個懸掛中斷服務后,向其IRQ位寫入1,將其清除。與第(d)步一樣,INT引腳產生另一個邊沿跳變。

- SPI主控制器處理完剩下的中斷請求,向其IRQ位寫入1,將其清除。沒有中斷處于懸掛狀態,因此,INT引腳返回至無效狀態。

中斷寄存器

表1. 陰影部分的MAX3420E寄存器位控制中斷系統

MAX3420E具有兩類USB中斷,由表1中陰影部分的寄存器控制。中斷位分為兩類:位于EPIRQ (R11)和EPIEN (R12)寄存器的端點控制,以及位于USBIRQ (R13)和USBIEN (R14)寄存器的USB控制。全局IE位在CPUCTL寄存器中。

表2. 14個MAX3420E中斷源

| Bit Name | Default | Location | Set By | Cleared By |

| IN0BAVIRQ | 1 | EPIRQ.0 | EP0 FIFO is ready for μP loading | Load the EP0BC register |

| OUT0DAVIRQ | 0 | EPIRQ.1 | EP0-OUT FIFO has host data | Write EPIRQ = 0x02 |

| OUT1DAVIRQ | 0 | EPIRQ.2 | EP1-OUT FIFO has host data | Write EPIRQ = 0x04 |

| IN2BAVIRQ | 1 | EPIRQ.3 | EP2-IN FIFO is ready for μP loading | Load the EP2INBC register |

| IN3BAVIRQ | 1 | EPIRQ.4 | EP3-IN FIFO is ready for μP loading | Load the EP3INBC register |

| SUDAVIRQ | 0 | EPIRQ.5 | Setup Data is available in SUDFIFO | Write EPIRQ = 0x20 |

| OSCOKIRQ | 0 | USBIRQ.0 | MAX3420E Oscillator/PLL is stable | Write USBIRQ = 0x01 |

| RWUDNIRQ | 0 | USBIRQ.1 | SIE has finished signaling RWU | Write USBIRQ = 0x02 |

| BUSACTIRQ | 0 | USBIRQ.2 | Bus is active | Write USBIRQ = 0x04 |

| URESIRQ | 0 | USBIRQ.3 | Host started signaling bus reset | Write USBIRQ = 0x08 |

| SUSPIRQ | 0 | USBIRQ.4 | Host suspended the bus | Write USBIRQ = 0x10 |

| NOVBUSIRQ | 0 | USBIRQ.5 | VBUS comparator made 1-0 transition | Write USBIRQ = 0x20 |

| VBUSIRQ | 0 | USBIRQ.6 | VBUS comparator made 0-1 transition | Write USBIRQ = 0x40 |

| URESDNIRQ | 0 | USBIRQ.7 | Host finished signaling bus reset | Write USBIRQ = 0x80 |

表2說明了14個中斷控制位,MAXQ3420E內部邏輯何時對它們進行置位,以及SPI主控制器怎樣清除它們。

中斷請求位

BAV位三個緩沖區就緒(BAV) IRQ位指示SPI主控制器可以裝入一個IN端點FIFO。芯片復位或者IN數據由端點緩沖區成功地發送給主機后,MAX3420E置位這些IRQ位。該IRQ通知SPI主控制器緩沖區可以裝入新數據。

圖6. 主機向端點3發送一個IN請求的總線過程

圖6所示為IN傳輸的總線過程,主機從MAX3420E申請數據。在數據包7145到達前,SPI主控制器先將字節00 00 08裝入端點3-IN FIFO (EP3INFIFO)。然后,SPI主控制器將數值3寫入EP3INBC (端點3 IN字節計數)寄存器。寫入字節計數寄存器,可完成以下三項功能:

- 通知MAX3420E當IN請求到達時有多少字節要發送。

- 使端點為傳輸數據做好準備(而不是非應答)。

- 清除EP3INBAV IRQ位。

如果在SPI主控制器準備好端點之前到達IN數據包,MAX3420E會響應一個NAK握手信號(圖7)。NAK握手信號通知主機稍后重發IN請求。

圖7. 如果MAX3420E還沒有準備好發送數據,則發出一個NAK包。

如果在IN數據傳輸至主機過程中出現誤碼,當主機重發IN請求時,MAX3420E自動重發數據(以及相同的數據觸發DATA0/DATA1)。只有接收到來自主機的ACK握手信號后,MAX3420E才會置位端點的BAV IRQ位,指示緩沖區準備好接收新數據。

重要提示:與所有的MAX3420E IRQ位一樣,也可以通過寫入1來三個清除BAV IRQ位。千萬不要這樣做。相反,應采用上面列出的方法:通過寫入IN端點的字節計數寄存器來清除BAV IRQ位。這是因為MAX3420E使用一個IN端點的BAV中斷請求位作為鎖定機制。該機制確保SPI主控制器和MAX3420E的串行接口引擎(SIE)不會同時使用端點緩沖區。例如,如果清除BAV位,然后以兩條單獨指令裝入字節計數器,那么當您更新字節計數寄存器時,可能開始了數據包傳輸,從而導致數據出錯。

BAV IRQ缺省值

三個BAV IRQ位(見表2 Default列中的1)的缺省值為1。這表明,上電或者復位后SPI主控制器將讀取到EPIRQ = 0x19。如果任何一個對應的IEN位置位,INT引腳將指示中斷處于懸掛狀態。

雙緩沖端點EP2-IN

MAX3420E EP2-IN端點為雙緩沖結構。這表明它有兩組64字節FIFO和字節計數寄存器。雙緩沖提高了傳輸帶寬,這是因為在裝入另一個數據包之前,SPI主控制器不需要等待數據包傳輸至主機。采用雙緩沖結構,SPI主控制器可以在一個IN FIFO向主機傳輸其IN數據的同時裝入另一個IN FIFO。當您裝載EP2INBC寄存器時,兩個緩沖區“自動輪換”。這將另一個FIFO (第二組)和字節計數寄存器提供給SPI主控制器使用。這種雙緩沖機制對固件來說是透明的。

雙緩沖機制使我們能夠觀察到的唯一影響出現在初始化過程中。上電或者芯片復位時,IN2BAVIRQ位置位。一般情況下,初始化程序把數據裝入EP2IN FIFO,然后裝載EP2INBC寄存器,為傳輸做好準備,同時清除了IN2BAVIRQ位。這樣做時,您會很奇怪地發現MAX3420E立即重新置位IN2BAVIRQ位。這表明第二個緩沖區已經準備就緒,允許SPI主控制器裝入第二個數據包。

DAV中斷請求位

OUT端點的數據就緒(DAV) IRQ位指示已經從主機接收到了新數據。MAX3420E自動處理總線重試操作,只有當接收到的數據無誤碼時,才會產生中斷請求。當SPI主控制器收到DAV中斷請求時,它將讀取端點字節計數寄存器,確定有效數據的大小。然后SPI主控制器從端點的OUTFIFO讀取相應數目的字節。SPI主控制器以向OUTDAV IRQ位寫入1的正常方式對其清零。這樣,使端點再次準備好接收下一個OUT數據包。

在圖8中,主機發送一個OUT PID和四個字節的數據,MAX3420E將其傳送至EP1OUT FIFO。當MAX3420E驗證傳送無誤碼后,將更新其EP1OUTBC寄存器,指示四個字節,向主機發送ACK包,并置位EP1OUTDAV IRQ,通知SPI主控制器可以提取端點1 FIFO內已經準備好的數據。

圖8. 主機向端點1發送OUT包的總線過程

雙緩沖端點EP1-OUT

MAX3420E EP1-OUT端點為雙緩沖結構,這表明它具有兩組64字節FIFO和字節計數寄存器。雙緩沖意味著SPI主控制器對OUT1DAVIRQ清零后,如果有另一個主機數據包在等待,它可以立即重新置位。

SUDAV中斷請求位

當主機向MAX3420E發送一個CONTROL傳輸時,MAX3420E在一個8字節FIFO中存儲8個SETUP字節,SPI主控制器可從SUDFIFO寄存器中讀取該數據。由于外設總是從該緩沖區中接收主機數據,SUDAVIRQ的作用類似一個OUT端點FIFO,當主機來的新數據接收完畢后,MAX3420E置位其SUDAV IRQ。一個SETUP數據包總是包含8個字節,因此,SETUP數據不需要字節計數寄存器。

OSCOK中斷請求位

當MAX3420E上電、芯片復位完畢、或者退出關電狀態時,需要時間來啟動內部振蕩器和PLL,以達到穩定。振蕩器就緒(OSCOK) IRQ指示MAX3420E已經準備好工作。

圖9. 復位MAX3420E,在結束前等待OSCOK的實例代碼。

圖9所示為實例代碼,采用CHIPRES寄存器位復位MAX3420E。由于芯片復位將停止內部振蕩器工作,代碼設置CHIPRES=0清除復位信號后,在使用MAX3420E之前應該等待振蕩器穩定下來。

RWUDN中斷請求位

處于掛起狀態時,USB外設可以發出遠程喚醒(RWU)信號,通知主機恢復總線工作。USB規范定義了一個1ms至15ms K-state的遠程喚醒信號。SPI主控制器通過設置遠程喚醒信號(SIGRWU)位等于1,來觸發RWU信號。

當SPI主控制器置位SIGRWU位時,MAX3420E等待5ms,驅動K-state 10ms,然后置位遠程喚醒完成中斷請求(RWUDNIRQ)位。5ms延時保證符合另一USB要求:在外設發出恢復信號前,總線必須至少空閑(J-state) 5ms。

圖10. 發送遠程喚醒信號的實例代碼

圖10所示為發送遠程喚醒的實例代碼。注意,MAX3420E實現信號定時,完成后置位IRQ。MAX3420E對于所有的定時USB事件均這樣處理,完成時產生一個中斷,因此SPI主控制器不需要定時控制信號間隔。

圖10中的代碼置位SIGRWU位,然后循環等待RWUDNIRQ置位,以確定持續10ms信號時間。然后,SPI主控制器設置SIGRWU = 0,并清除IRQ位。一般地,在多任務SPI主控制器中,應響應RWUDNIRQ中斷請求,而不要浪費時間直接檢查IRQ位。

接收到RWUDNITQ中斷后的5ms內,SPI主控制器應關閉SIGRWU位。如果沒有這樣做,MAX3420E將啟動另一個10ms K-state,重復這一過程(等待5ms, 然后10ms K-state),直到SIGRWU = 0。在RWU信號處理過程中設置SIGRWU = 0,不會終止RWU信號。

如果SPI主控制器設置SIGRWU = 1時MAX3420E正處于關電狀態(PWRDOWN = 1),那么MAX3420E會自動重新啟動振蕩器,等待其達到穩定,然后開始發送RWU信號。在這種情況下,SPI主控制器不需要檢查OSCOK IRQ。

BUSACT中斷請求位

當MAX23420E探測到在USB數據包的開始位置有SYNC模式時,置位BUSACT IRQ位。USB總線復位過程不是總線活動狀態,因此不會觸發BUSACK中斷請求。

URES和URESDN中斷請求位

USB主機通過至少保持50ms的單端零(SE0)狀態(D+和D-同時驅動至低電平),來復位外設。探測到2.5μs的SE0狀態后,MAX3420E置位USB復位IRQ (URESIRQ)。然后,當主機完成復位后,MAX3420E置位USB復位完成IRQ (URESDNIRQ)。

由于SPI主控制器需要監視USB總線復位事件,在總線復位期間,MAX3420E不會清除URESIE、URESDNIE或IE中斷使能位。但在總線復位期間它會清除EPIEN和USBIEN寄存器中的所有其他中斷使能位。

SUSP中斷請求位

當MAX3420E探測到總線停止工作3ms (持續J-state)后,它產生掛起中斷請求(SUSPIRQ)。如果使用MAX3420E的外設是由總線供電的,它必須進入低功耗狀態,以最大程度降低從VBUS上吸收的電流。在這種情況下,SPI主控制器應關斷消耗功率的外設,然后設置PWRDOWN = 1,使MAX3420E進入低功耗模式。這樣一來,MAX3420E振蕩器停止工作,并進入最低功耗狀態。

需要注意下面兩條編程提示:

- 清除SUSPIRQ位不能阻止3ms后中斷重新產生。總線掛起時,為避免產生重復的掛起中斷,在總線恢復工作之前,應清除掛起IEN位。

- 內部掛起定時器邏輯由MAX3420E的內部振蕩器提供時鐘。因此,如果您將器件置為關斷模式(設置PWRDOWN = 1),然后試圖向SUSPIRQ位寫入1來清除該位,MAX3420E將不會清除該位。MAX3420E離不開現在已停止工作的內部時鐘。

一個自供電外設可以探測自己是否插入USB接口,利用這些中斷進行上電。內部VBUS比較器觸發這些中斷,它比較VBCOMP引腳電壓和內部基準電壓。它們均為邊沿觸發,當VBUS電壓(VBUSIRQ)進行供電或者停止供電(NOVBUSIRQ)時置位。

總線供電的外設不需要探測VBUS,因為它由VBUS供電。這樣,可以釋放VBCOMP引腳,用作通用輸入。在這種應用中,VBCOMP引腳沒有內部上拉電阻,因此,應在VBCOMP引腳和VL之間連接一個上拉電阻。

編程提示

清除IEN位芯片復位

芯片復位期間,所有IE位被清除。出現以下情況時,芯片復位:

- VL電源為MAX3420E供電(上電復位)。

- MAX3420E RES#引腳置低。

- SPI主控制器設置CHIPRES = 1。

當MAX3420E探測到一個USB總線復位(總線暫停3ms)后,除了三個IE位外,其他IE位全部清零。SPI主控制器可能需要處理總線復位中斷,以監視總線復位信號的狀態。因此,總線復位不會影響以下IE位:

- URESIE

- URESDNIE

- IE (全局中斷使能)

清除BAV和DAV IRQ位

請注意,DAV IRQ位以正常的寫1方式進行清除。BAV位(用于IN端點)的清除方式不同,采用的方法是寫入字節計數寄存器。

電子發燒友App

電子發燒友App

評論