資料介紹

數(shù)字信號(hào)處理器(DSP)做某些模擬工作比模擬電路要出色,因此得以生存。在某些情況下,由于成本或復(fù)雜性的原因,任務(wù)甚至不能考慮用模擬電路,DSP仍然是一種可行的選擇,在很多情況下可以輕松地完成那些任務(wù)。

這是因?yàn)镈SP進(jìn)行算術(shù)運(yùn)算既好又快,如加法和乘法。聰明的數(shù)學(xué)家和工程師利用了這一實(shí)際,通過創(chuàng)造算法來解決主要采用兩種數(shù)?運(yùn)算的復(fù)雜的信號(hào)處理任務(wù)。

如今的DSP芯片不僅僅只是一個(gè)優(yōu)秀的處理引擎。芯片上還集成了存儲(chǔ)子系統(tǒng)、高速接口、I/O等等。增加這些部件的目的是為了提高整體性能,降低功耗以及針對(duì)特殊的處理任務(wù)。

為了更好地理解各種DSP芯片的可用選項(xiàng)以及器件各部分是如何配合作為一個(gè)整體,分析當(dāng)今市場(chǎng)上幾種有代表性的DSP是有幫助的。我們將仔細(xì)研究單核、單核加微控制器以及多核DSP芯片的例子。

單核DSP芯片

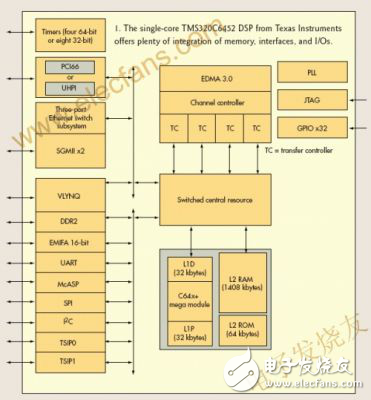

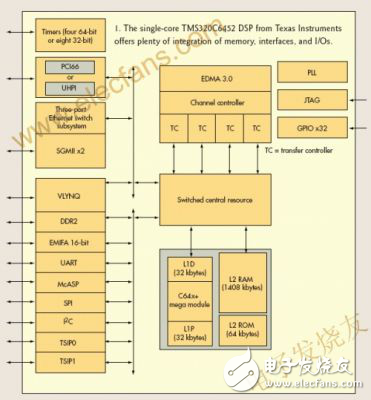

認(rèn)為DSP芯片有一個(gè)單DSP核是很自然的,例如,TI的TMS320C6?52(圖1)。此芯片是高性能固點(diǎn)DSP的TMS320C6?x+家族的一員,針對(duì)工藝密集的多通道電信基礎(chǔ)設(shè)施和醫(yī)用成像系統(tǒng)。DSP核只不過是芯片設(shè)計(jì)的一部分,芯片的其余部分還包括存儲(chǔ)器、I/O以及其他功能模塊。

C6?52 DSP集成了組織為兩級(jí)存儲(chǔ)子系統(tǒng)的片上存儲(chǔ)器。一級(jí)(L1)程序和數(shù)據(jù)存儲(chǔ)器每個(gè)都是32k字節(jié)。此存儲(chǔ)器可配置為映射RAM、高速緩存,或者兩者的某種組合。

當(dāng)配置為高速緩存時(shí),L1程序(L1P)是一個(gè)直接映射高速緩存,而L1數(shù)據(jù)(L1D)是一個(gè)雙向指令集結(jié)合高速緩存。二級(jí)(L2)存儲(chǔ)在程序與數(shù)據(jù)空間之間共享。L2存儲(chǔ)也能配置為映射RAM、高速緩存或者兩者的某種組合。設(shè)計(jì)師可使用片上存儲(chǔ)器為其項(xiàng)目增加特色。

C6?52還包括兩個(gè)串行吉比特媒體獨(dú)立接口(SGMII)以太媒體接入控制(MAC)口和一個(gè)吉比特開關(guān)。此開關(guān)通過自動(dòng)監(jiān)控?cái)?shù)據(jù)流以確保只有一個(gè)合適的TI將決策門加到所能的開關(guān)上,例如,用來辨別語(yǔ)音和數(shù)據(jù)通信,以提高多芯片設(shè)計(jì)的效率。如果DSP全部用于語(yǔ)音處理,就會(huì)阻止數(shù)據(jù)流進(jìn)入,這樣可更有效地使用其處理帶寬。此外,器件具有兩個(gè)電信串行接口端(TSIP),可無縫連接至常見電信串行數(shù)據(jù)流。

C6?52上的其他I/O有一個(gè)66MHz PCI接口或通用主機(jī)端接口(UHPI);一個(gè)到外部存儲(chǔ)器的雙數(shù)據(jù)率(DDR2)接口;TI開發(fā)的專利串行通信接口VLYNQ;一個(gè)16位外部存儲(chǔ)器接口(EMIFA);一個(gè)多通道通用音頻串行口(McASP);以及其他熟悉的接口。從此DSP的I/O判斷,可以肯定它是用于電信應(yīng)用。其他應(yīng)用用的是不同的I/O。

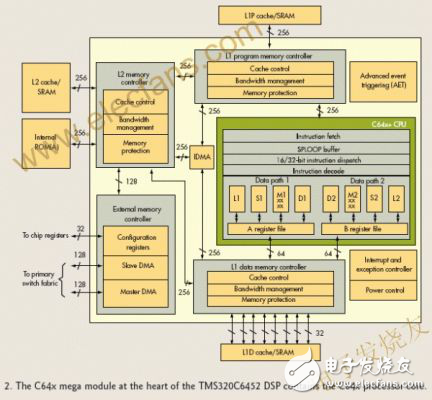

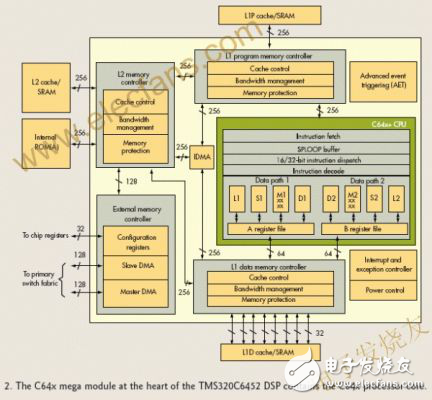

C6?52和TI其他幾款DSP的核心是C6?x mega模塊,其組成包括幾個(gè)元件:C6?x+處理器、L1程序和數(shù)據(jù)存儲(chǔ)控制器、L2存儲(chǔ)控制器、內(nèi)部DMA(IDMA)、中斷控制器、掉電控制器以及外部存儲(chǔ)控制器(圖2)。Mega模塊還支持對(duì)L1P、L1D和L2存儲(chǔ)器的存儲(chǔ)保護(hù)。此外還提供mega模塊資源的帶寬管理。

模塊上的C6?x+處理器是一非常快速的DSP,工作速率可達(dá)1.2GHz。它采用8個(gè)功能模塊、兩個(gè)寄存器文件以及兩個(gè)數(shù)據(jù)路徑。在這八個(gè)功能單元中,有兩個(gè)是乘法器或者M(jìn)單元。每個(gè)M單元在每個(gè)時(shí)鐘周期執(zhí)行四次16位×16位乘法-累加(MAC)。

因此,在C6?x+核上,每個(gè)周期可執(zhí)行8次16位×16位MAC。在1.2GHz時(shí)鐘速率下,每秒鐘可發(fā)生9600次16位MMAC。此外,C6?x+核的每個(gè)乘法器每個(gè)時(shí)鐘周期可計(jì)算一次32位×32位MAC或者四次8位×8位MAC。順便提一下,C6?52不是以900M的最快的速度工作。

C6?x+處理器的新特征有一個(gè)令人鐘愛的名字SPLOOP。這一小型指令緩沖器有助于創(chuàng)建軟件流水線操作環(huán)路,在這些環(huán)路中并行執(zhí)行環(huán)路的多次迭代。SPLOOP緩沖器減小了有關(guān)軟件流水線操作的代碼大小。

DSP+微控制器芯片

另一類DSP在芯片上附加微控制器核。有時(shí),為一個(gè)分離的核,如ARM處理器。有的情況下,處理器核同時(shí)包含DSP和MCU功能。這種情況就是眾所周知的模擬器件公司(ADI)的Blackfin DSP架構(gòu)。

Blackfin是基于具有混合16/32型指令集架構(gòu)的10級(jí)RISC MCU/DSP流水線,包括雙16位MAC DSP指令和一個(gè)32位類似于RISC的指令集。這種組合提供信號(hào)處理功能,具有與通用處理器有關(guān)的使用方便的特點(diǎn)。Blackfin處理器架構(gòu)完全兼容SIMD(單指令多數(shù)據(jù))并包括視頻與圖像處理加速指令。

這種處理屬性組合使Blackfin處理器與其同類產(chǎn)品不同。他們被設(shè)計(jì)為在信號(hào)處理和控制處理應(yīng)用方面工作都非常好,在很多情況下,設(shè)計(jì)中無需獨(dú)立的異類處理器。Blackfin處理器在單核產(chǎn)品中速率高達(dá)756MHz。

除本地支持8位數(shù)據(jù)外,8位數(shù)據(jù)字長(zhǎng)是很多像素處理算法常用的,Blackfin架構(gòu)包括專門定義的指令,用于在視頻處理應(yīng)用中增強(qiáng)性能。例如,“SUM ABSOLUTE DIFFERENCE”指令支持用于視頻壓縮算法(如MPEG2、MPEG4和JPEG)的運(yùn)動(dòng)估算算法。

這種架構(gòu)處理多長(zhǎng)度指令編碼。非常常用的控制型指令被編碼為緊湊的16位字,更多算術(shù)密集的信號(hào)處理指令編碼為32位值。處理器將16位控制指令與32位信號(hào)處理指令混合并連接成6?位組,以使存儲(chǔ)器容量最大化。緩沖和取指令時(shí),內(nèi)核完全自動(dòng)挑選總線長(zhǎng)度,因?yàn)閮?nèi)核沒有調(diào)整約束。

所有Blackfin處理器,如ADSP-BF523,都包含獨(dú)立的DMA控制器,支持自動(dòng)數(shù)據(jù)傳輸,而對(duì)處理器內(nèi)核的操作壓力很小(圖3)。DMA傳輸可發(fā)生在內(nèi)部存儲(chǔ)器與許多具備可直接存儲(chǔ)器存取(DMA)功能外設(shè)的任何部分之間。傳輸也能發(fā)生在外設(shè)和接至外部存儲(chǔ)器接口的外部器件之間,包括SDRAM控制器和異步存儲(chǔ)控制器。

存儲(chǔ)器架構(gòu)包括L1和L2存儲(chǔ)器塊。L1存儲(chǔ)器直接連接到處理器內(nèi)核,以全系統(tǒng)時(shí)鐘速度運(yùn)行,為時(shí)間關(guān)鍵的算法部分提供最佳系統(tǒng)性能。此外,L1存儲(chǔ)器也可配置為SRAM、高速緩沖存儲(chǔ)器或者兩者的組合。

通過同時(shí)支持SRAM和高速緩沖存儲(chǔ)器編程模型,系統(tǒng)設(shè)計(jì)師可分配關(guān)鍵的要求高帶寬和到SRAM低存取的實(shí)時(shí)信號(hào)處理數(shù)據(jù)集合,同時(shí)在高速緩存中存儲(chǔ)“軟”實(shí)時(shí)控制和操作系統(tǒng)(OS)任務(wù)。L2存儲(chǔ)器是一更大的大容量存儲(chǔ)器存貯區(qū),性能稍有降低,但仍快于片外存儲(chǔ)器。

這是因?yàn)镈SP進(jìn)行算術(shù)運(yùn)算既好又快,如加法和乘法。聰明的數(shù)學(xué)家和工程師利用了這一實(shí)際,通過創(chuàng)造算法來解決主要采用兩種數(shù)?運(yùn)算的復(fù)雜的信號(hào)處理任務(wù)。

如今的DSP芯片不僅僅只是一個(gè)優(yōu)秀的處理引擎。芯片上還集成了存儲(chǔ)子系統(tǒng)、高速接口、I/O等等。增加這些部件的目的是為了提高整體性能,降低功耗以及針對(duì)特殊的處理任務(wù)。

為了更好地理解各種DSP芯片的可用選項(xiàng)以及器件各部分是如何配合作為一個(gè)整體,分析當(dāng)今市場(chǎng)上幾種有代表性的DSP是有幫助的。我們將仔細(xì)研究單核、單核加微控制器以及多核DSP芯片的例子。

單核DSP芯片

認(rèn)為DSP芯片有一個(gè)單DSP核是很自然的,例如,TI的TMS320C6?52(圖1)。此芯片是高性能固點(diǎn)DSP的TMS320C6?x+家族的一員,針對(duì)工藝密集的多通道電信基礎(chǔ)設(shè)施和醫(yī)用成像系統(tǒng)。DSP核只不過是芯片設(shè)計(jì)的一部分,芯片的其余部分還包括存儲(chǔ)器、I/O以及其他功能模塊。

C6?52 DSP集成了組織為兩級(jí)存儲(chǔ)子系統(tǒng)的片上存儲(chǔ)器。一級(jí)(L1)程序和數(shù)據(jù)存儲(chǔ)器每個(gè)都是32k字節(jié)。此存儲(chǔ)器可配置為映射RAM、高速緩存,或者兩者的某種組合。

當(dāng)配置為高速緩存時(shí),L1程序(L1P)是一個(gè)直接映射高速緩存,而L1數(shù)據(jù)(L1D)是一個(gè)雙向指令集結(jié)合高速緩存。二級(jí)(L2)存儲(chǔ)在程序與數(shù)據(jù)空間之間共享。L2存儲(chǔ)也能配置為映射RAM、高速緩存或者兩者的某種組合。設(shè)計(jì)師可使用片上存儲(chǔ)器為其項(xiàng)目增加特色。

C6?52還包括兩個(gè)串行吉比特媒體獨(dú)立接口(SGMII)以太媒體接入控制(MAC)口和一個(gè)吉比特開關(guān)。此開關(guān)通過自動(dòng)監(jiān)控?cái)?shù)據(jù)流以確保只有一個(gè)合適的TI將決策門加到所能的開關(guān)上,例如,用來辨別語(yǔ)音和數(shù)據(jù)通信,以提高多芯片設(shè)計(jì)的效率。如果DSP全部用于語(yǔ)音處理,就會(huì)阻止數(shù)據(jù)流進(jìn)入,這樣可更有效地使用其處理帶寬。此外,器件具有兩個(gè)電信串行接口端(TSIP),可無縫連接至常見電信串行數(shù)據(jù)流。

C6?52上的其他I/O有一個(gè)66MHz PCI接口或通用主機(jī)端接口(UHPI);一個(gè)到外部存儲(chǔ)器的雙數(shù)據(jù)率(DDR2)接口;TI開發(fā)的專利串行通信接口VLYNQ;一個(gè)16位外部存儲(chǔ)器接口(EMIFA);一個(gè)多通道通用音頻串行口(McASP);以及其他熟悉的接口。從此DSP的I/O判斷,可以肯定它是用于電信應(yīng)用。其他應(yīng)用用的是不同的I/O。

C6?52和TI其他幾款DSP的核心是C6?x mega模塊,其組成包括幾個(gè)元件:C6?x+處理器、L1程序和數(shù)據(jù)存儲(chǔ)控制器、L2存儲(chǔ)控制器、內(nèi)部DMA(IDMA)、中斷控制器、掉電控制器以及外部存儲(chǔ)控制器(圖2)。Mega模塊還支持對(duì)L1P、L1D和L2存儲(chǔ)器的存儲(chǔ)保護(hù)。此外還提供mega模塊資源的帶寬管理。

模塊上的C6?x+處理器是一非常快速的DSP,工作速率可達(dá)1.2GHz。它采用8個(gè)功能模塊、兩個(gè)寄存器文件以及兩個(gè)數(shù)據(jù)路徑。在這八個(gè)功能單元中,有兩個(gè)是乘法器或者M(jìn)單元。每個(gè)M單元在每個(gè)時(shí)鐘周期執(zhí)行四次16位×16位乘法-累加(MAC)。

因此,在C6?x+核上,每個(gè)周期可執(zhí)行8次16位×16位MAC。在1.2GHz時(shí)鐘速率下,每秒鐘可發(fā)生9600次16位MMAC。此外,C6?x+核的每個(gè)乘法器每個(gè)時(shí)鐘周期可計(jì)算一次32位×32位MAC或者四次8位×8位MAC。順便提一下,C6?52不是以900M的最快的速度工作。

C6?x+處理器的新特征有一個(gè)令人鐘愛的名字SPLOOP。這一小型指令緩沖器有助于創(chuàng)建軟件流水線操作環(huán)路,在這些環(huán)路中并行執(zhí)行環(huán)路的多次迭代。SPLOOP緩沖器減小了有關(guān)軟件流水線操作的代碼大小。

DSP+微控制器芯片

另一類DSP在芯片上附加微控制器核。有時(shí),為一個(gè)分離的核,如ARM處理器。有的情況下,處理器核同時(shí)包含DSP和MCU功能。這種情況就是眾所周知的模擬器件公司(ADI)的Blackfin DSP架構(gòu)。

Blackfin是基于具有混合16/32型指令集架構(gòu)的10級(jí)RISC MCU/DSP流水線,包括雙16位MAC DSP指令和一個(gè)32位類似于RISC的指令集。這種組合提供信號(hào)處理功能,具有與通用處理器有關(guān)的使用方便的特點(diǎn)。Blackfin處理器架構(gòu)完全兼容SIMD(單指令多數(shù)據(jù))并包括視頻與圖像處理加速指令。

這種處理屬性組合使Blackfin處理器與其同類產(chǎn)品不同。他們被設(shè)計(jì)為在信號(hào)處理和控制處理應(yīng)用方面工作都非常好,在很多情況下,設(shè)計(jì)中無需獨(dú)立的異類處理器。Blackfin處理器在單核產(chǎn)品中速率高達(dá)756MHz。

除本地支持8位數(shù)據(jù)外,8位數(shù)據(jù)字長(zhǎng)是很多像素處理算法常用的,Blackfin架構(gòu)包括專門定義的指令,用于在視頻處理應(yīng)用中增強(qiáng)性能。例如,“SUM ABSOLUTE DIFFERENCE”指令支持用于視頻壓縮算法(如MPEG2、MPEG4和JPEG)的運(yùn)動(dòng)估算算法。

這種架構(gòu)處理多長(zhǎng)度指令編碼。非常常用的控制型指令被編碼為緊湊的16位字,更多算術(shù)密集的信號(hào)處理指令編碼為32位值。處理器將16位控制指令與32位信號(hào)處理指令混合并連接成6?位組,以使存儲(chǔ)器容量最大化。緩沖和取指令時(shí),內(nèi)核完全自動(dòng)挑選總線長(zhǎng)度,因?yàn)閮?nèi)核沒有調(diào)整約束。

所有Blackfin處理器,如ADSP-BF523,都包含獨(dú)立的DMA控制器,支持自動(dòng)數(shù)據(jù)傳輸,而對(duì)處理器內(nèi)核的操作壓力很小(圖3)。DMA傳輸可發(fā)生在內(nèi)部存儲(chǔ)器與許多具備可直接存儲(chǔ)器存取(DMA)功能外設(shè)的任何部分之間。傳輸也能發(fā)生在外設(shè)和接至外部存儲(chǔ)器接口的外部器件之間,包括SDRAM控制器和異步存儲(chǔ)控制器。

存儲(chǔ)器架構(gòu)包括L1和L2存儲(chǔ)器塊。L1存儲(chǔ)器直接連接到處理器內(nèi)核,以全系統(tǒng)時(shí)鐘速度運(yùn)行,為時(shí)間關(guān)鍵的算法部分提供最佳系統(tǒng)性能。此外,L1存儲(chǔ)器也可配置為SRAM、高速緩沖存儲(chǔ)器或者兩者的組合。

通過同時(shí)支持SRAM和高速緩沖存儲(chǔ)器編程模型,系統(tǒng)設(shè)計(jì)師可分配關(guān)鍵的要求高帶寬和到SRAM低存取的實(shí)時(shí)信號(hào)處理數(shù)據(jù)集合,同時(shí)在高速緩存中存儲(chǔ)“軟”實(shí)時(shí)控制和操作系統(tǒng)(OS)任務(wù)。L2存儲(chǔ)器是一更大的大容量存儲(chǔ)器存貯區(qū),性能稍有降低,但仍快于片外存儲(chǔ)器。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 內(nèi)置DSP的噪音抑制全雙工通話芯片ATH8809 39次下載

- 山景DSP芯片AP8264A2數(shù)據(jù)手冊(cè)

- 山景DSP芯片AP8248B數(shù)據(jù)手冊(cè)

- 山景DSP芯片AP8248A2數(shù)據(jù)手冊(cè)

- 基于DSP的DS1302芯片使用的程序資料 9次下載

- 16位DSP語(yǔ)音芯片WT588F02A-16S產(chǎn)品手冊(cè) 9次下載

- 基于在線服務(wù)功能擴(kuò)展的服務(wù)功能鏈部署方法 3次下載

- 基于DSP芯片的足球機(jī)器人實(shí)現(xiàn)與設(shè)計(jì) 26次下載

- 基于DSP芯片的永磁同步電機(jī)控制系統(tǒng) 39次下載

- 如何在系統(tǒng)中選擇合適的DSP芯片 31次下載

- 使用擴(kuò)展芯片實(shí)現(xiàn)端口擴(kuò)展的實(shí)例資料合集免費(fèi)下載

- spartan-6 FPGA DSP48A1芯片的詳細(xì)資料介紹 31次下載

- 最佳FPGA和專用DSP解析 0次下載

- 現(xiàn)代DSP芯片功能的擴(kuò)展概述 1次下載

- DSP芯片的基本結(jié)構(gòu)和特征

- dsp是什么意思 dsp功放對(duì)音質(zhì)到底有沒有提升 1.5w次閱讀

- dsp芯片和arm芯片區(qū)別 dsp的應(yīng)用領(lǐng)域 4649次閱讀

- dsp怎么調(diào)音質(zhì)最好 dsp芯片和單片機(jī)的區(qū)別 1352次閱讀

- DSP芯片的特點(diǎn)與分類 2185次閱讀

- 解析OPPO超級(jí)防抖功能 5618次閱讀

- HPI接口的工作模式以及與上位主機(jī)的連接方式解析 7553次閱讀

- 基于DSP芯片PC機(jī)之間的USB接口設(shè)計(jì) 2038次閱讀

- dsp芯片可分為哪幾個(gè)存儲(chǔ)區(qū) 7304次閱讀

- 一文了解FPGA與DSP的區(qū)別、特點(diǎn)及用途 2.9w次閱讀

- DSP芯片選型須知 1.9w次閱讀

- DSP芯片主流廠商分析與常用芯片 8.4w次閱讀

- DSP芯片的特點(diǎn)與分類 1.1w次閱讀

- 基于EMIF接口的DSP控制系統(tǒng)設(shè)計(jì) 5799次閱讀

- 基于以太網(wǎng)的DSP遠(yuǎn)程加載技術(shù)研究 1399次閱讀

- 用插值查找表實(shí)現(xiàn)FPGA的DSP功能 1954次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1489次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費(fèi)

- 6基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

- 7基于單片機(jī)和 SG3525的程控開關(guān)電源設(shè)計(jì)

- 0.23 MB | 3次下載 | 免費(fèi)

- 8基于單片機(jī)的紅外風(fēng)扇遙控

- 0.23 MB | 3次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537791次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論