資料介紹

隨著數(shù)字信號(hào)處理芯片性價(jià)比的不斷提高,數(shù)字信號(hào)處理的應(yīng)用領(lǐng)域飛速發(fā)展,同時(shí)Pentium高速CPU的出現(xiàn),要求有極高的數(shù)據(jù)通量予以支持,而低速的ISA總線在解決這些問(wèn)題方面逐漸無(wú)能為力,取而代之的是高速的PCI總線。PCI總線可將高速外圍設(shè)備直接掛在CPU總線上,33MHz/32位時(shí)數(shù)據(jù)傳輸速率可達(dá)132MB/s,66MHz/64位時(shí)更是性能加倍,打破了數(shù)據(jù)傳輸速率的瓶頸,使得CPU的性能得到充分發(fā)揮。如果采用美國(guó)TI公司生產(chǎn)的高速高性能數(shù)字信號(hào)處理器DSP取代原來(lái)的單片機(jī)作為板載CPU,可以充分利用PCI總線的優(yōu)點(diǎn)直接將采集的數(shù)據(jù)傳到微機(jī)內(nèi)存,有效地解決了數(shù)據(jù)的實(shí)時(shí)傳輸和存儲(chǔ)問(wèn)題。

測(cè)控系統(tǒng)的硬件組成

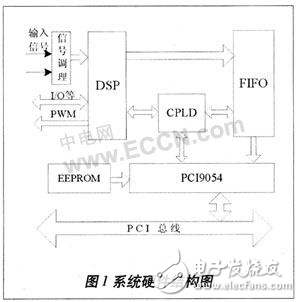

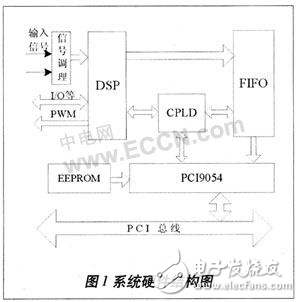

系統(tǒng)基本硬件結(jié)構(gòu)如圖1所示。整個(gè)高速測(cè)控系統(tǒng)主要由信號(hào)調(diào)理電路、DSP模塊、FIFC)存儲(chǔ)器、CPLD控制電路、PC19054接口芯片等組成。系統(tǒng)采用主從結(jié)構(gòu),PC機(jī)作為上位機(jī),用于完成對(duì)系統(tǒng)的控制(如AD轉(zhuǎn)換的開(kāi)始、DSP復(fù)位、中斷響應(yīng)、數(shù)據(jù)接收與處理等)。DSP作為下位機(jī),用于完成數(shù)據(jù)的采集與處理、PWM波以及其他外圍信號(hào)的控制等。

DSP測(cè)控模塊介紹

系統(tǒng)采用的DSP芯片為TI公司的TMS320LF2407。電路設(shè)計(jì)時(shí),利用的DSP內(nèi)部的16通道A/D轉(zhuǎn)換實(shí)現(xiàn)數(shù)據(jù)采集,DSP與FIFO的電路接口電壓都為3.3V,可實(shí)現(xiàn)無(wú)縫連接,DSP的數(shù)據(jù)總線直接與FIFO的數(shù)據(jù)輸入端口相連,DSP與FIFO的時(shí)鐘頻率應(yīng)設(shè)為相同。這樣,無(wú)需插入等待周期,控制信號(hào)經(jīng)CPLD直接轉(zhuǎn)換為FIFO的讀寫(xiě)信號(hào),實(shí)現(xiàn)數(shù)據(jù)的高速存儲(chǔ)。

先進(jìn)先出存儲(chǔ)器

在DMA傳輸方式下,由于PCI9054內(nèi)部的FIFO只有32級(jí)深度,實(shí)時(shí)傳送高速數(shù)據(jù)時(shí),PCI9054內(nèi)部的FIFO會(huì)很快存滿,而DSP內(nèi)的數(shù)據(jù)仍會(huì)源源不斷的傳送過(guò)來(lái),易造成數(shù)據(jù)的丟失,因此必須要擴(kuò)展外部FIFO。

本系統(tǒng)采用I D T公司高速CMOS同步FIFO芯片IDT72V3660,它的容量為4096×36bit;有高達(dá)100MHz的讀寫(xiě)速度;可以兼容3.3V和5V兩種接口電壓。該FIFO具有標(biāo)準(zhǔn)的“滿”(FF#)、“半滿”(HF#)、“空”(EF#)等標(biāo)志。系統(tǒng)可以根據(jù)這些標(biāo)志信號(hào)控制對(duì)FIFO的讀寫(xiě)操作。在CPLD的邏輯控制下,當(dāng)WEN#有效時(shí),在WCLK的每一個(gè)上升沿,F(xiàn)IFO會(huì)把輸人數(shù)據(jù)線上的數(shù)據(jù)存入內(nèi)部存儲(chǔ)器。當(dāng)REN#有效且輸出允許(OE#有效)時(shí),在RCLK的每一個(gè)上升沿,F(xiàn)IFO會(huì)把內(nèi)部存儲(chǔ)器中的數(shù)據(jù)發(fā)送到輸出數(shù)據(jù)總線上(低電平用“#”表示)。

控制邏輯芯片CPLD

本系統(tǒng)采用Altera公司的EPM7 128來(lái)實(shí)現(xiàn)系統(tǒng)的邏輯控制,主要包括DSP控制邏輯、FIFO控制邏輯、PCI9054接口控制邏輯三個(gè)部分,其中,對(duì)PC219054的邏輯控制是設(shè)計(jì)的重點(diǎn)。設(shè)計(jì)中利用MaxPlusⅡ軟件進(jìn)行VHDL語(yǔ)言編程、仿真和調(diào)試。

PCI9054及外部接口分析

PCI與板載CPU的橋接有兩種設(shè)計(jì)方案,一種是采用FPGA,通過(guò)軟件編程實(shí)現(xiàn)硬件功能。另一種是利用專用PCI橋接芯片,適合快速開(kāi)發(fā)的場(chǎng)合。

本系統(tǒng)采用PLX公司的PCI總線專用接口控制芯片PC19054。它符合PCIV2.1和PCIV2_2規(guī)范;可同時(shí)支持3.3V和5V兩種信號(hào)環(huán)境;提供了兩個(gè)獨(dú)立的可編程DMA控制器;內(nèi)部有6種可編程FIFO,以實(shí)現(xiàn)零等待突發(fā)傳輸及局部總線和PCI總線之間的異步操作;在PCI總線端支持33MHz/32位,傳輸速率最高可達(dá)132MB/s;在局部端可編程實(shí)現(xiàn)8/16/32位的數(shù)據(jù)寬度,支持復(fù)用/非復(fù)用的32位地址/數(shù)據(jù),時(shí)鐘最高可達(dá)50MHz。

PCI9054局部總線可工作在M、J、C三種模式,M模式是專門為Motorola公司的 MPC850和MPC860提供直接非復(fù)用的接口;J模式地址/數(shù)據(jù)線復(fù)用;C模式與J模式差別不大,但地址/數(shù)據(jù)線非復(fù)用,更符合連接習(xí)慣。本設(shè)計(jì)采用C模式。

PCI9054的數(shù)據(jù)傳輸模式可分為主模式、從模式、DMA模式。模式的選擇主要根據(jù)硬件設(shè)計(jì)者對(duì)硬件的設(shè)計(jì)需要而定。本系統(tǒng)采用DMA模式,在DMA傳輸模式下,PCI9054既是PCI端的主控方,又是局部端的主控方。

PCI9054集成了兩個(gè)互相獨(dú)立的DMA通道,每個(gè)通道都支持Block DMA和Scatter/(3ather DMA,其中通道0還支持請(qǐng)求(Demand)DMA傳輸方式。當(dāng)有通道進(jìn)行DMA傳輸時(shí),DMA控制器將發(fā)起對(duì)局部總線和PCI總線操作,其傳輸過(guò)程如圖2所示。

PC219054提供了三個(gè)物理總線接口:PCI總線接口、EEPROM接口、局部總線接口。PCI總線接口依照PCI擴(kuò)展板上定義的引腳分配情況將彼此對(duì)應(yīng)的信號(hào)連接在一起即可。本系統(tǒng)采用的EEPROM為4K、3.3V串行的93LC66B,通過(guò)對(duì)PCI時(shí)鐘分頻來(lái)產(chǎn)生EEPROM時(shí)鐘,內(nèi)部存放PCI9054的配置信息,系統(tǒng)加電時(shí)PCI9054自動(dòng)加載EEPROM中的配置信息,并由BIOS通過(guò)PCI總線對(duì)配置寄存器讀寫(xiě),來(lái)完成各種控制功能。接口電路如圖3所示。

測(cè)控系統(tǒng)的硬件組成

系統(tǒng)基本硬件結(jié)構(gòu)如圖1所示。整個(gè)高速測(cè)控系統(tǒng)主要由信號(hào)調(diào)理電路、DSP模塊、FIFC)存儲(chǔ)器、CPLD控制電路、PC19054接口芯片等組成。系統(tǒng)采用主從結(jié)構(gòu),PC機(jī)作為上位機(jī),用于完成對(duì)系統(tǒng)的控制(如AD轉(zhuǎn)換的開(kāi)始、DSP復(fù)位、中斷響應(yīng)、數(shù)據(jù)接收與處理等)。DSP作為下位機(jī),用于完成數(shù)據(jù)的采集與處理、PWM波以及其他外圍信號(hào)的控制等。

DSP測(cè)控模塊介紹

系統(tǒng)采用的DSP芯片為TI公司的TMS320LF2407。電路設(shè)計(jì)時(shí),利用的DSP內(nèi)部的16通道A/D轉(zhuǎn)換實(shí)現(xiàn)數(shù)據(jù)采集,DSP與FIFO的電路接口電壓都為3.3V,可實(shí)現(xiàn)無(wú)縫連接,DSP的數(shù)據(jù)總線直接與FIFO的數(shù)據(jù)輸入端口相連,DSP與FIFO的時(shí)鐘頻率應(yīng)設(shè)為相同。這樣,無(wú)需插入等待周期,控制信號(hào)經(jīng)CPLD直接轉(zhuǎn)換為FIFO的讀寫(xiě)信號(hào),實(shí)現(xiàn)數(shù)據(jù)的高速存儲(chǔ)。

先進(jìn)先出存儲(chǔ)器

在DMA傳輸方式下,由于PCI9054內(nèi)部的FIFO只有32級(jí)深度,實(shí)時(shí)傳送高速數(shù)據(jù)時(shí),PCI9054內(nèi)部的FIFO會(huì)很快存滿,而DSP內(nèi)的數(shù)據(jù)仍會(huì)源源不斷的傳送過(guò)來(lái),易造成數(shù)據(jù)的丟失,因此必須要擴(kuò)展外部FIFO。

本系統(tǒng)采用I D T公司高速CMOS同步FIFO芯片IDT72V3660,它的容量為4096×36bit;有高達(dá)100MHz的讀寫(xiě)速度;可以兼容3.3V和5V兩種接口電壓。該FIFO具有標(biāo)準(zhǔn)的“滿”(FF#)、“半滿”(HF#)、“空”(EF#)等標(biāo)志。系統(tǒng)可以根據(jù)這些標(biāo)志信號(hào)控制對(duì)FIFO的讀寫(xiě)操作。在CPLD的邏輯控制下,當(dāng)WEN#有效時(shí),在WCLK的每一個(gè)上升沿,F(xiàn)IFO會(huì)把輸人數(shù)據(jù)線上的數(shù)據(jù)存入內(nèi)部存儲(chǔ)器。當(dāng)REN#有效且輸出允許(OE#有效)時(shí),在RCLK的每一個(gè)上升沿,F(xiàn)IFO會(huì)把內(nèi)部存儲(chǔ)器中的數(shù)據(jù)發(fā)送到輸出數(shù)據(jù)總線上(低電平用“#”表示)。

控制邏輯芯片CPLD

本系統(tǒng)采用Altera公司的EPM7 128來(lái)實(shí)現(xiàn)系統(tǒng)的邏輯控制,主要包括DSP控制邏輯、FIFO控制邏輯、PCI9054接口控制邏輯三個(gè)部分,其中,對(duì)PC219054的邏輯控制是設(shè)計(jì)的重點(diǎn)。設(shè)計(jì)中利用MaxPlusⅡ軟件進(jìn)行VHDL語(yǔ)言編程、仿真和調(diào)試。

PCI9054及外部接口分析

PCI與板載CPU的橋接有兩種設(shè)計(jì)方案,一種是采用FPGA,通過(guò)軟件編程實(shí)現(xiàn)硬件功能。另一種是利用專用PCI橋接芯片,適合快速開(kāi)發(fā)的場(chǎng)合。

本系統(tǒng)采用PLX公司的PCI總線專用接口控制芯片PC19054。它符合PCIV2.1和PCIV2_2規(guī)范;可同時(shí)支持3.3V和5V兩種信號(hào)環(huán)境;提供了兩個(gè)獨(dú)立的可編程DMA控制器;內(nèi)部有6種可編程FIFO,以實(shí)現(xiàn)零等待突發(fā)傳輸及局部總線和PCI總線之間的異步操作;在PCI總線端支持33MHz/32位,傳輸速率最高可達(dá)132MB/s;在局部端可編程實(shí)現(xiàn)8/16/32位的數(shù)據(jù)寬度,支持復(fù)用/非復(fù)用的32位地址/數(shù)據(jù),時(shí)鐘最高可達(dá)50MHz。

PCI9054局部總線可工作在M、J、C三種模式,M模式是專門為Motorola公司的 MPC850和MPC860提供直接非復(fù)用的接口;J模式地址/數(shù)據(jù)線復(fù)用;C模式與J模式差別不大,但地址/數(shù)據(jù)線非復(fù)用,更符合連接習(xí)慣。本設(shè)計(jì)采用C模式。

PCI9054的數(shù)據(jù)傳輸模式可分為主模式、從模式、DMA模式。模式的選擇主要根據(jù)硬件設(shè)計(jì)者對(duì)硬件的設(shè)計(jì)需要而定。本系統(tǒng)采用DMA模式,在DMA傳輸模式下,PCI9054既是PCI端的主控方,又是局部端的主控方。

PCI9054集成了兩個(gè)互相獨(dú)立的DMA通道,每個(gè)通道都支持Block DMA和Scatter/(3ather DMA,其中通道0還支持請(qǐng)求(Demand)DMA傳輸方式。當(dāng)有通道進(jìn)行DMA傳輸時(shí),DMA控制器將發(fā)起對(duì)局部總線和PCI總線操作,其傳輸過(guò)程如圖2所示。

PC219054提供了三個(gè)物理總線接口:PCI總線接口、EEPROM接口、局部總線接口。PCI總線接口依照PCI擴(kuò)展板上定義的引腳分配情況將彼此對(duì)應(yīng)的信號(hào)連接在一起即可。本系統(tǒng)采用的EEPROM為4K、3.3V串行的93LC66B,通過(guò)對(duì)PCI時(shí)鐘分頻來(lái)產(chǎn)生EEPROM時(shí)鐘,內(nèi)部存放PCI9054的配置信息,系統(tǒng)加電時(shí)PCI9054自動(dòng)加載EEPROM中的配置信息,并由BIOS通過(guò)PCI總線對(duì)配置寄存器讀寫(xiě),來(lái)完成各種控制功能。接口電路如圖3所示。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 電子煙的結(jié)構(gòu)原理與系統(tǒng)設(shè)計(jì)方案下載 152次下載

- 基于NVM和DRAN的混合內(nèi)存系統(tǒng)設(shè)計(jì)方案 12次下載

- 簡(jiǎn)易病房呼叫系統(tǒng)設(shè)計(jì)方案 15次下載

- 如何使用PCI總線DSP進(jìn)行數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)資料說(shuō)明 4次下載

- 基于PCI總線DSP圖像處理試驗(yàn)平臺(tái)的研究 28次下載

- 適于測(cè)控系統(tǒng)的文件存儲(chǔ)結(jié)構(gòu)研究 9次下載

- 基于PCI的雙向高速傳輸系統(tǒng) 34次下載

- 基于DSP+PCI結(jié)構(gòu)的噪聲信號(hào)采集處理系統(tǒng) 43次下載

- 基于DSP的PCI總線數(shù)據(jù)采集系統(tǒng)的研究 119次下載

- 基于PCI Express總線高速數(shù)據(jù)采集卡的設(shè)計(jì)與實(shí)現(xiàn)

- 基于PCI總線的高速數(shù)據(jù)采集卡的設(shè)計(jì)

- 基于PCI-1716的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

- 基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

- 基于PCI-1714的高速數(shù)據(jù)采集系統(tǒng)方案設(shè)計(jì)

- 真空釬焊爐溫度監(jiān)測(cè)控制系統(tǒng)優(yōu)化設(shè)計(jì)研究

- UPS系統(tǒng)設(shè)計(jì)方案解讀 873次閱讀

- 不同應(yīng)用場(chǎng)景設(shè)計(jì)相應(yīng)拓?fù)?b class="flag-6" style="color: red">結(jié)構(gòu)方案的方法 2166次閱讀

- 基于STM32的室內(nèi)空氣凈化監(jiān)測(cè)系統(tǒng)設(shè)計(jì)方案 2460次閱讀

- 基于三叉樹(shù)鏈表的編譯器中間結(jié)構(gòu)的設(shè)計(jì)方案研究 3570次閱讀

- 基于Acex1K系列芯片和PCI總線實(shí)現(xiàn)測(cè)控系統(tǒng)的設(shè)計(jì) 1314次閱讀

- 基于FPGA+PCI數(shù)據(jù)采集存儲(chǔ)硬件設(shè)計(jì)方案詳解 2638次閱讀

- PCI5565反射內(nèi)存網(wǎng)技術(shù)的應(yīng)用研究 3239次閱讀

- pci總線結(jié)構(gòu)及分類 1.8w次閱讀

- 一種高速圖像數(shù)據(jù)采集板的設(shè)計(jì)方案 2195次閱讀

- 一種高速實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案 4875次閱讀

- 一種采用PCI軟核的軸角數(shù)據(jù)采集系統(tǒng) 2569次閱讀

- 基于PCI總線的微弱信號(hào)采集模塊的設(shè)計(jì)方案 1883次閱讀

- 基于RC測(cè)量系統(tǒng)的設(shè)計(jì)方案 3789次閱讀

- 基于SVPWM算法的變頻調(diào)速系統(tǒng)設(shè)計(jì)方案 5144次閱讀

- LED大屏幕控制電路設(shè)計(jì)方案研究 2628次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1489次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說(shuō)明

- 4.28 MB | 18次下載 | 4 積分

- 5開(kāi)關(guān)電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費(fèi)

- 6基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

- 7基于單片機(jī)和 SG3525的程控開(kāi)關(guān)電源設(shè)計(jì)

- 0.23 MB | 3次下載 | 免費(fèi)

- 8基于單片機(jī)的紅外風(fēng)扇遙控

- 0.23 MB | 3次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開(kāi)關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537791次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論