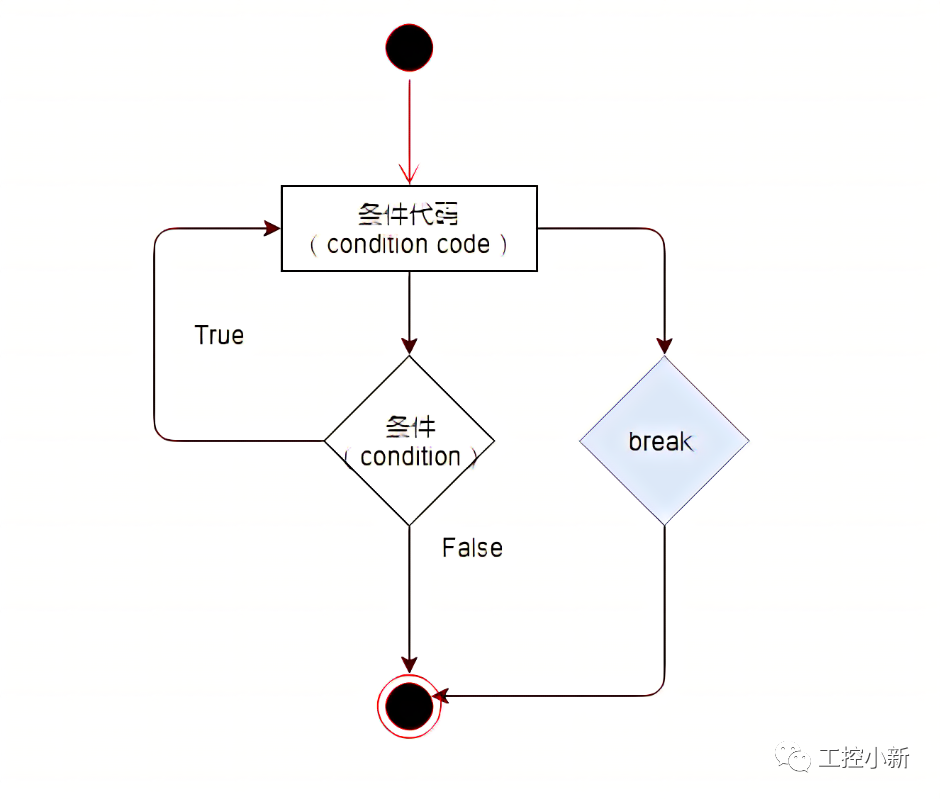

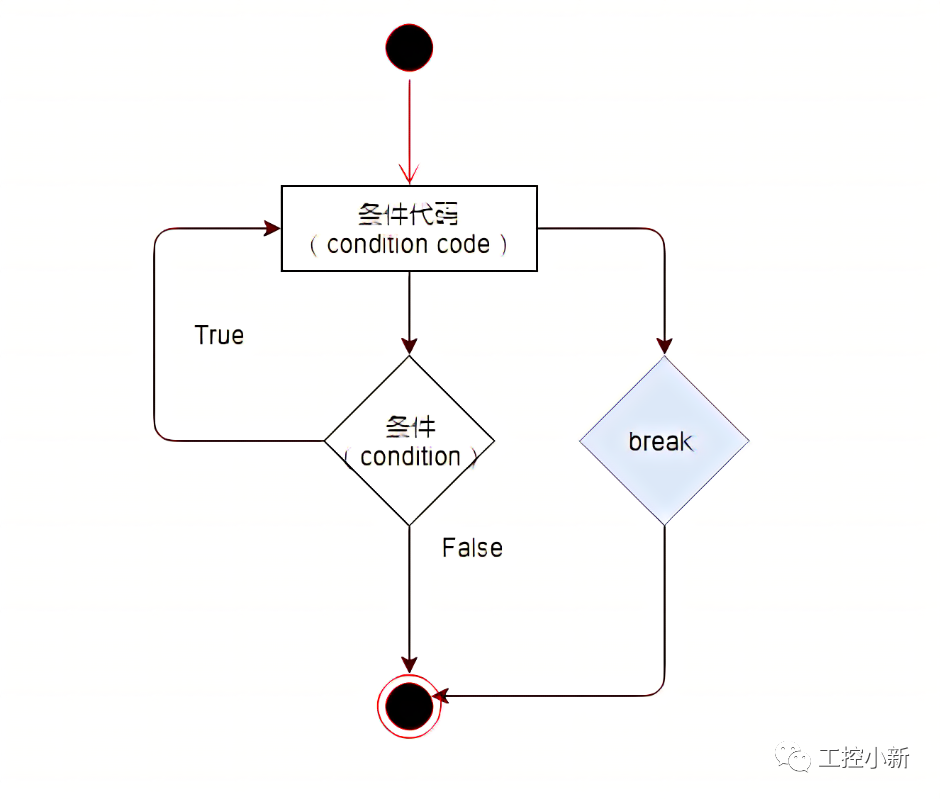

在C語言中,break語句是一種控制流語句,它用于終止當前所在的循環結構(for、while、do-while)或者switch語句,從而跳出循環或者結束switch語句的執行。

2023-08-17 15:35:46 917

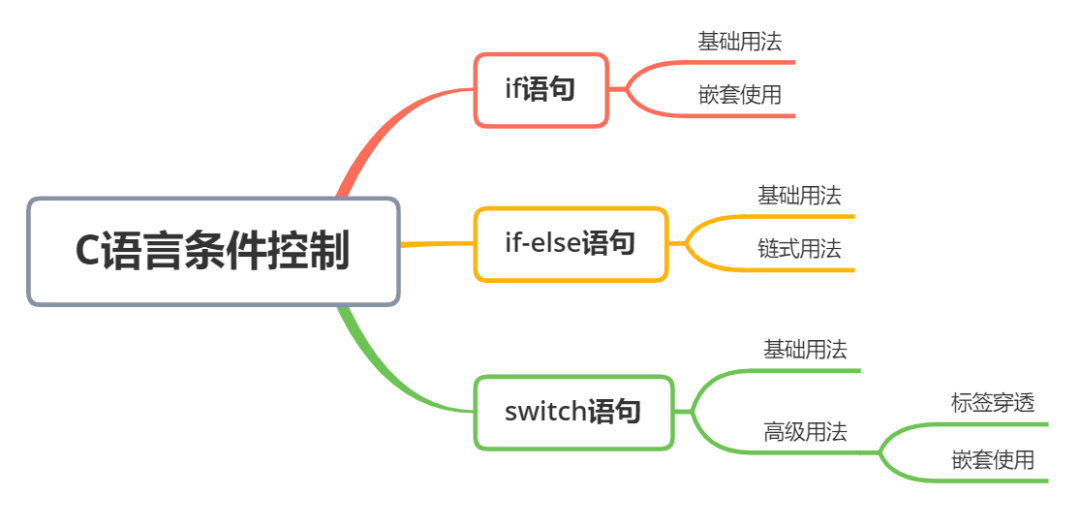

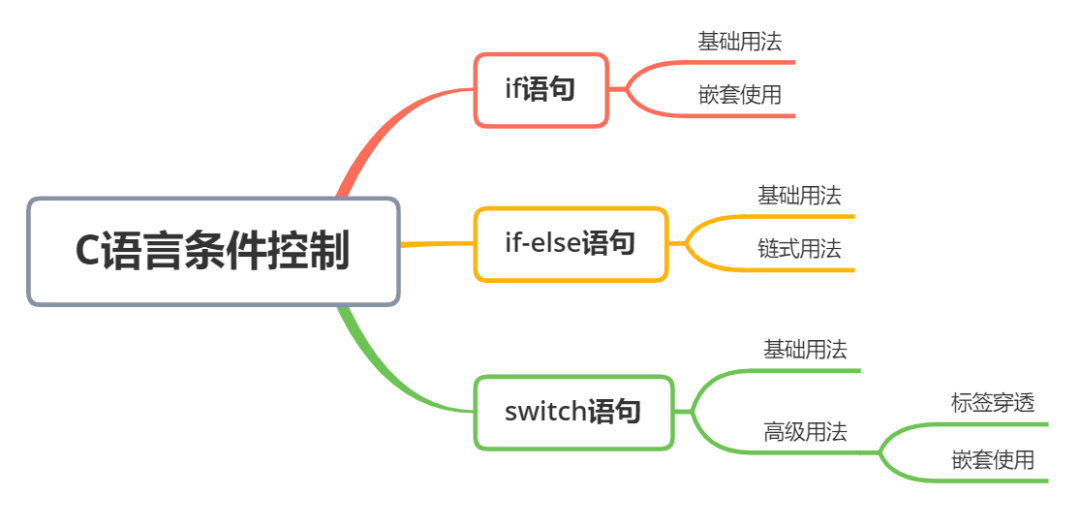

917 在C語言中,有三種條件判斷結構:if語句、if-else語句和switch語句。

2023-08-18 16:36:49 886

886

Rust 是一門現代化的系統編程語言,它擁有高性能、內存安全和并發性等特點。Rust 的語法設計非常優秀,其中 match 語句是一種非常強大的語言特性。match 語句可以讓我們根據不同的匹配模式

2023-09-19 17:08:06 626

626 C語言的break轉移語句是一種用于跳出循環或者switch語句的控制結構。它的作用是提前結束循環或者switch語句,從而避免不必要的計算或者執行。

2023-11-22 15:34:35 272

272

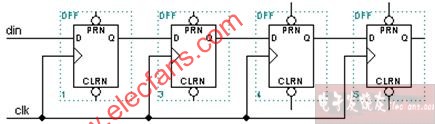

VHDL并行語句.ppt

2017-01-21 19:56:00

,較難入門,代碼也比較冗長,且無法直接用于集成電路底層建模,但具有很好的行為級描述能力和較好的系統級描述能力,較適用于大型項目。本文只介紹VHDL,重點講述VHDL的語句執行特性VHDL英文全稱

2014-01-04 11:35:34

的定義與應用。[理論內容]一、并行語句所謂的并行語句指采用這些語法生成的硬件電路在時間上可以并行(或并發)的執行(運行)。這是VHDL語法必須具備的能力,也符合硬件電路的特性。這一點不同于軟件,因為軟件

2009-03-19 16:45:14

大家好,有人使用 vhdl 編程嗎,vhdl語言中過程 procedure 語句 可以 沒有參數嗎,過程語句的 書寫格式 是:procedure 過程名 (參數表)這個參數 可以 不寫嗎,謝謝

2013-08-19 15:49:49

語句6.1 進程語句6.2 快語句6.3 并行信號賦值語句6.3.1 簡單信號賦值語句6.3.2 條件信號賦值語句6.3.3 選擇信號賦值語句6.4 并行過程調用語句6.5 元件例化語句6.6 生成語句

2008-06-04 10:31:29

嗨,我在我的頂層模塊中有三個生成語句,我對所有三個使用相同的變量“i”,e因為i在0到x中生成所以,其中x在3種情況下是不同的。這會導致實施問題嗎?我可以用嗎?謝謝,Koyel以上來自于谷歌翻譯以下

2018-10-25 15:22:00

條件為 true 時,該語句才會執行代碼。語法if (condition){ 當條件為 true 時執行的代碼}請使用小寫的 if。使用大寫字母(IF)會生成 JavaScript 錯誤!實例當時間小于 20:00 時,生成問候 "Good day":if (time

2021-07-17 10:36:50

廣泛,且參與錄入題目的人有多位,因此容易出現錄入重復題目的情況。所以需要實現語句相似度分析功能,從而篩選出重復的題目并人工處理之。下面介紹如何使用Java實現上述想法,完成語句相似度分析:1

2019-02-23 10:27:38

Labview&SQLSever自動生成查詢語句,VI的輸入端為表格的列名,輸出為查詢語句以及語句是否合法的布爾值,支持時間段查詢,條件查詢,時間段與條件組合查詢,Labview版本為18版本。

2021-09-29 16:17:59

SQL語句生成器SQL數據庫語句生成及分析器(支持表結構、索引、所有記錄到SQL腳本)可用于數據數的備份和恢復!功能不用多說,試試就知道了

2009-06-12 16:15:05

的執行時間為5d。 (2)fork……join,用來組合需要并行執行的語句,被稱為并行塊。例如:parameter d = 50; reg[7:0] r; fork //由一系列延遲產生的波形 # d r

2016-06-02 21:31:00

generate為verilog中的生成語句,當對矢量中的多個位進行重復操作時,或者當進行多個模塊的實例引用的重復操作時,或者根據參數的定義來確定程序中是否應該包含某段Verilog代碼的時候

2020-12-23 16:59:15

使用 VHDL 進行數字電路描述時候,如果按照執行順序對 VHDL 的程序進行分類,可以分為順序(sequential)描述語句和并行(concurrent)描述語句。順序語句描述的程序總是按照程序

2018-09-13 09:39:31

VHDL 不僅僅提供了一系列的順序語句,同樣也提供了很多并行語句。在 VHDL 中,并行語句主要包括以下幾種:? 進程(PROCESS)語句;? 塊(BLOCK)語句;? 并發信號賦值;? 條件信號

2018-09-13 10:14:51

Verilog HDL 在執行語句時分為順序和并行兩種方式。在順序語句塊中,語句按給定次序順序執行;在并行語句塊中,語句并行執行。順序語句塊的語法和實例如下:begin[:block_id

2018-09-25 09:22:19

1個Verilog HDL語言,有很多個always語句,這些always語句是并行一起執行,還是按照先后順序執行?

2012-06-29 10:01:24

用CASE WHEN 語句編寫四選一的VHDL程序

2012-06-23 15:24:50

用IF語句編寫四選一的VHDL程序

2012-06-23 15:23:34

用選擇賦值語句編寫四選一的VHDL程序

2012-06-23 15:31:11

摘要:介紹了PLC梯形圖可視化編輯器的設計及由PLC梯形圖自動生成語句的算法,詳細描述了實現主要數據結構及梯形圖向語句表轉換的具體算法。關鍵 詞:可編程控制器(PLC) 梯形圖語句表有向圖原文地址

2021-07-02 06:22:41

的時候,使用生成語句能夠大大簡化程序的編寫過程。生成語句可以控制變量的聲明、任務或函數的調用,還能對實力引用進行全面的控制。編寫代碼時必須在模塊中說明生成塊的實例范圍,關鍵字 generate

2015-04-07 17:43:05

[學習要求] 掌握VHDL硬件描述語言的基本描述語句。并可以利用這些語句進行簡單電路的設計。[重點與難點]重點:常用的并行語句與順序語句的語法。難點:部件(Component

2009-03-18 22:03:32 100

100 在一定的語言環境中漢語詞語之間存在著優先組合搭配關系,據此,在本文中利用互信息、數理統計和人腦聯想記憶的相關理論,設計了一個漢語句子聯想生成器,使用該生成器

2009-09-26 14:25:12 20

20 matlab基本語句

簡述matlab基本語句。

2010-04-23 09:09:57 57

57 switch/case開關語句是一種多分支選擇語句,是用來實現多方向條件分支的語句。雖然從理論上講采用條件語句也可以實現多方向條件分支,但是當分支較多時會使條件語句的嵌套層

2010-07-15 14:26:00 18

18 實驗六、VHDL的基本描述語句設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的基本描述語句的使用方法。二? 實驗設備

2009-03-13 19:23:57 1998

1998 if語句和while循環

C語言中,if語句和while循環都會用到布爾表達式。下面是一個使用if語句的簡單例子:

#include

2009-07-29 10:48:32 8304

8304 單片機C語言教程-基礎語句

C語言入門之基礎語句 從程序流程的角度來看,程序可以分為三種基本結構,即順序結構、分支

2010-03-27 17:15:46 3059

3059 電子發燒友為您提供了數據庫SQL語句電子教程,幫助您了解數據庫 SQL語句 ,學習讀懂數據庫SQL語句,達到會寫數據庫SQL語句,通過具體的分析進行了數據庫SQL語句教學。

2011-07-14 17:09:09 0

0 Proteus之if語句的應用,很好的Proteus資料,快來學習吧。

2016-04-18 14:49:30 0

0 Proteus之switch語句的應用,很好的Proteus資料,快來學習吧。

2016-04-18 14:49:30 0

0 這是vhdl并行語句的使用規則,介紹的pdf文件

2016-06-08 14:10:53 0

0 該函數通過for語句控制蜂鳴器的鳴響次數來說明for語句的功能。

2016-10-09 15:06:48 8

8 VHDL并行語句

2016-12-11 23:38:39 0

0 mysql基本語句詳細教程

2016-12-15 22:15:42 0

0 若干條語句形成功能塊,能用做數組的下標等,而在 C 中括號的分 工較為明顯,{}號是用于將若干條語句組合在一起形成一種功能塊,這種由若干條語句組合 而成的語句就叫復合語句。復合語句之間用{}分隔,而它內部的各條語句還是需要以分號“;” 結束。復合語句

2017-11-22 12:44:14 404

404 來輔助輸入查詢語句,以及綜合使用查找相似對象(Find Similar Objects)和PCB Filter面板這兩種功能來自動生成查詢語句表達式,并自動應用于規則設置。

2018-06-19 10:17:00 2406

2406 本文檔的主要內容詳細介紹的是C++語言程序設計時如何控制語句?內容包括了1 C++語句概述2 if語句實現選擇結構3 switch語句實現多分支4 循環結構

2018-09-20 14:51:48 2

2 本文檔的主要內容詳細介紹的是VHDL程序的順序語句如何應用詳細實驗資料說明。一、 實驗目的1. 鞏固編譯、仿真VHDL文件的方法2. 掌握VHDL程序順序語句的應用

2018-10-17 08:00:00 6

6 本文檔的主要內容詳細介紹的是VHDL程序的并行語句如何應用詳細實驗資料說明。一、 實驗目的1. 鞏固編譯、仿真VHDL文件的方法2. 掌握VHDL程序并行語句的應用

2018-10-17 08:00:00 23

23 本文檔的主要內容詳細介紹的是EDA教程之VHDL數據IF語句使用示例的詳細資料說明。

2018-10-17 08:00:00 0

0 VHDL中并行語句(concurrent statements)有多種語句結構,各種并行語句在結構體中的執行是同步進行的;并行語句間在執行順序的地位上是平等的,其執行順序與書寫順序無關。

2018-10-17 08:00:00 0

0 同C語言或其他語言相同,Java語言的復合語句是以整個塊區為單位的語句,所以又稱塊語句。復合語句由開括號“{”開始,閉括號“}”結束。

2019-03-22 08:00:00 2

2 本文檔的主要內容詳細介紹的是Java的循環語句的詳細資料說明包括了:1、while循環語句,2、do…while循環語句,3、for循環語句

2019-03-22 08:00:00 0

0 if條件語句是一個重要的編程語句,它用于告訴程序在某個條件成立的情況下執行某段程序,而在另一種情況下執行另外的語句。

2019-03-22 08:00:00 0

0 C語言用語句來向計算機發出操作指令。一個C語句經編譯后,可以生成若干條機器指令,它是構成函數的基礎。C語言的語句可以分為控制語句、函數調用語句、復合語句、表達式語句以及空語句等多種。以下我們主要介紹的是C語言的控制語句,這種語句具有相對固定的格式,用來實現某種特定的功能。

2019-06-10 17:48:00 0

0 生成語句(GENERATE)是一種可以建立重復結構或者是在多個模塊的表示形式之間進行選擇的語句。由于生成語句可以用來產生多個相同的結構,因此使用生成語句就可以避免多段相同結構的VHDL程序的重復書寫。 生成語句有兩種形式:FOR- GENERATE模式和IF- GENERATE模式。

2019-11-21 07:08:00 5312

5312 Verilog中提供了四種循環語句,可用于控制語句的執行次數,分別為:for,while,repeat,forever。其中,for,while,repeat是可綜合的,但循環的次數需要在編譯之前就確定,動態改變循環次數的語句是不可綜合的。forever語句是不可綜合的,主要用于產生各種仿真激勵。

2019-10-13 12:23:00 18103

18103 本文檔的主要內容詳細介紹的是SQL的語句練習程序實例免費下載。

2019-10-29 15:16:40 4

4 下列語句部分是Mssql語句,不可以在access中使用。

2019-10-31 15:09:25 7

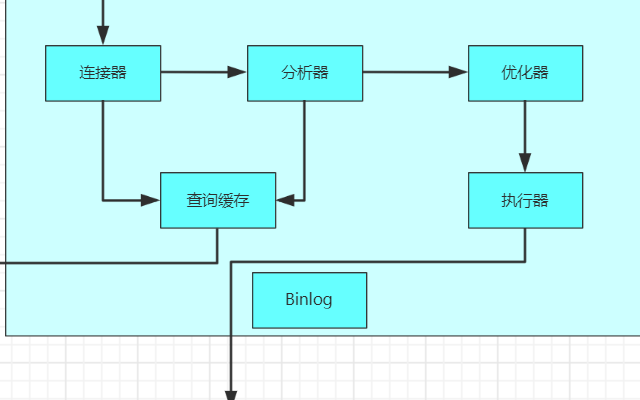

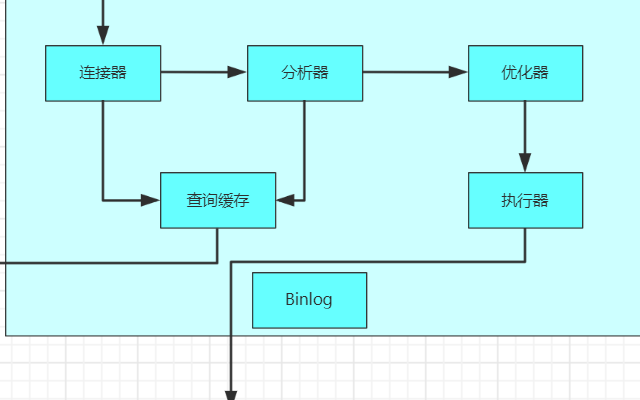

7 最近有粉絲面試互聯網公司被問到:你知道select語句和update語句分別是怎么執行的嗎?,要我寫一篇這兩者執行SQL語句的區別,這不就來了。 總的來說,select和update執行的邏輯大體

2020-11-03 09:41:38 3192

3192

的并行描述語句

VHDL的子程序結構

VHDL庫、程序包和配置

VHDL的預定義屬性

VHDL的重載

VHDL結構體的描述方式

2021-01-22 17:52:14 16

16 CONTIUNE語句 CONTIUNE語句用來終止循環語句(FOR, WHILE或REPEAT)的當前重復的執行。 語法(Syntax) CONTINUE語句依據下列規則執行: 此語句立即終止循環體

2021-04-16 11:19:54 1947

1947

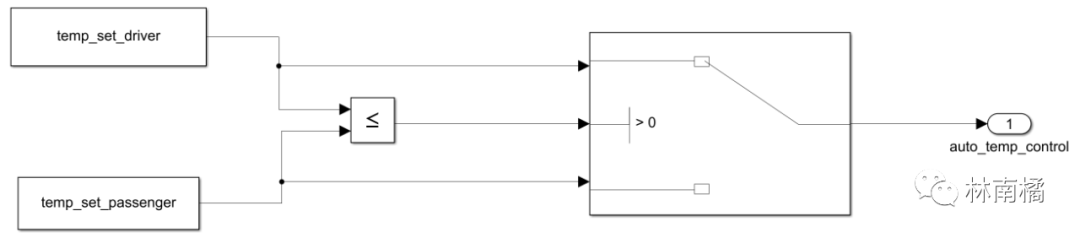

條件語句的可綜合性 HDL語言的條件語句與算法語言的條件語句,最大的差異在于: 1.不管條件:當前輸入條件沒有對應的描述,則該條件為不管條件(Don’t?Care)。對應不管條件的信號稱為不管信號

2021-05-12 09:12:22 1558

1558

解釋verilog HDL中的initial語句的用法。

2021-05-31 09:11:33 0

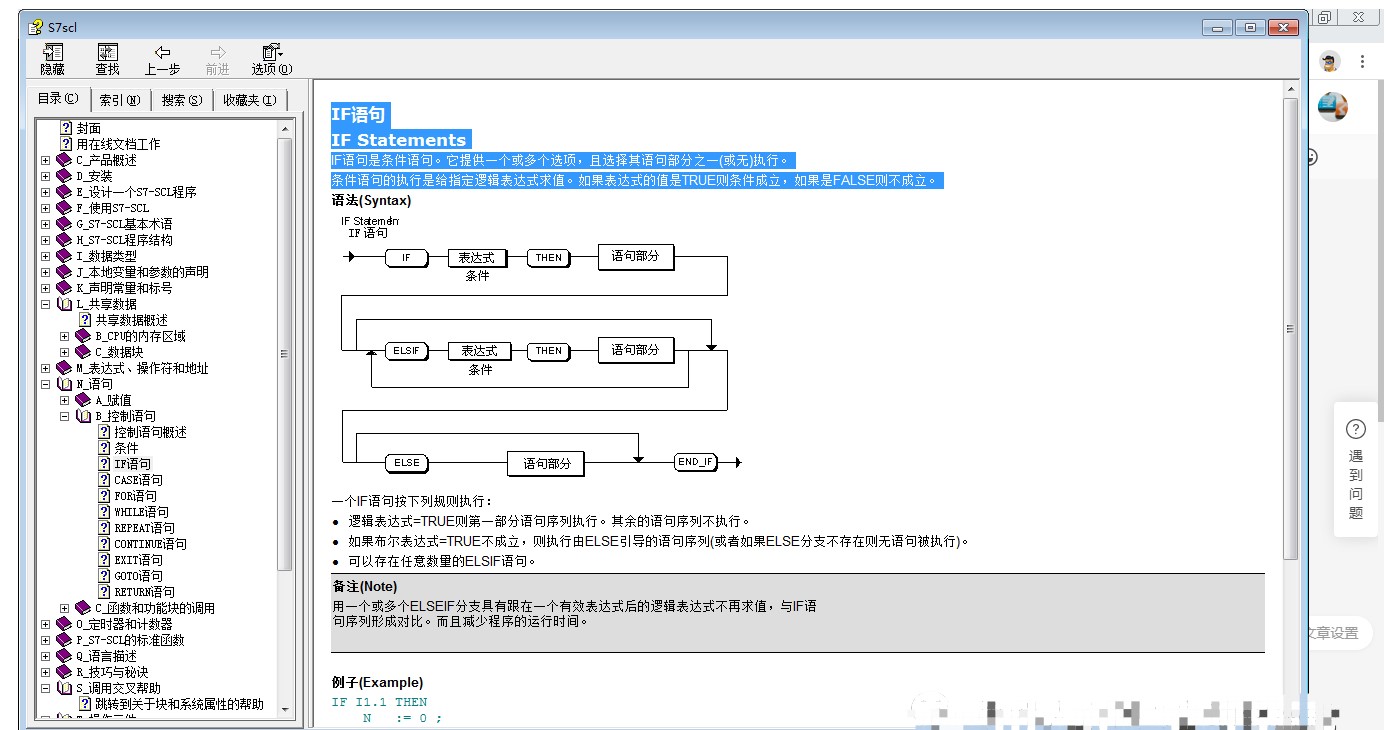

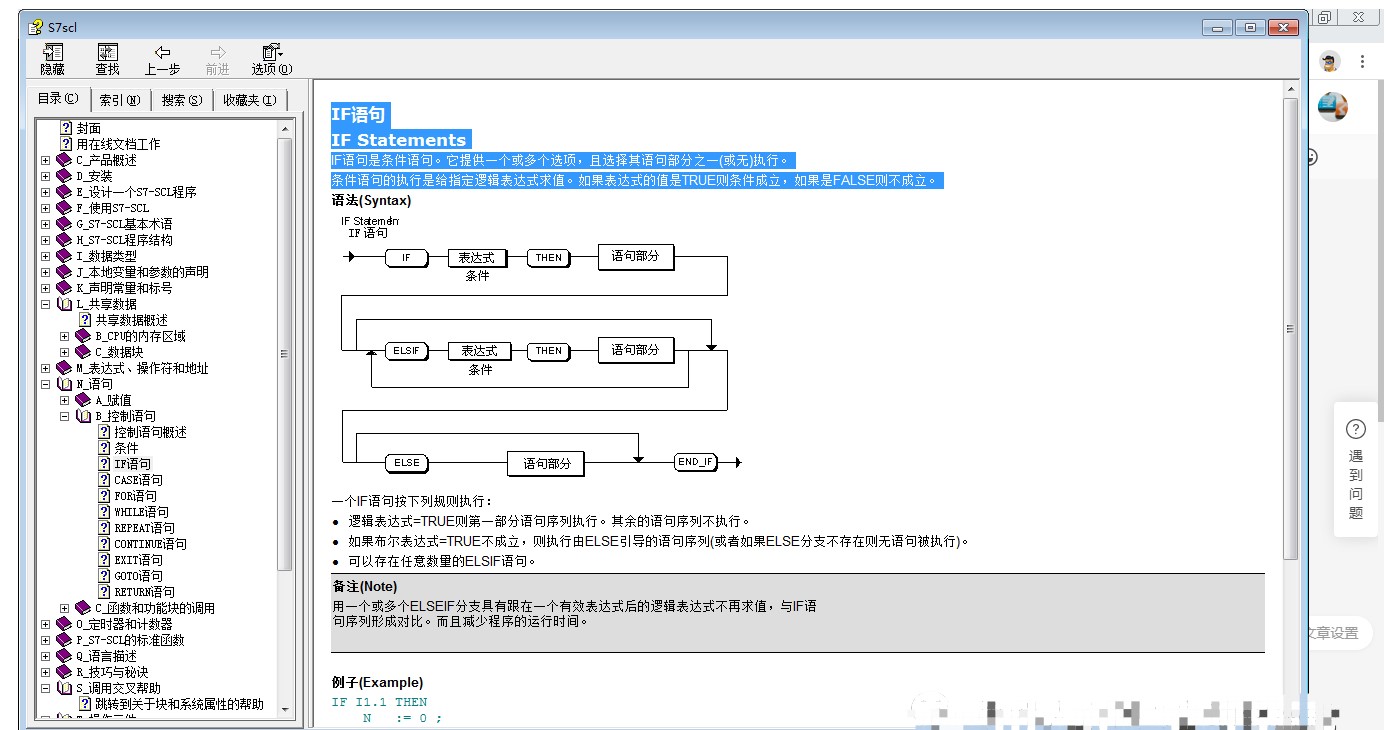

0 IF語句:IF語句讓你根據條件是TRUE或FALSE來支配兩個分支之一的程序運行。

2021-06-15 10:15:50 8186

8186

1. 塊語句有兩種,一種是 begin-end 語句, 通常用來標志()執行的語句;一種是 fork-join 語句,通常用來標志()執行的語句。 答案:順序,并行 解析: (1)begin_end

2021-06-18 15:16:49 2741

2741 Labview&SQLSever如何自動生成查詢語句

2021-09-29 18:17:43 7

7 為了區分SQL語句與主語言語句,所有SQL 語句必須加前綴EXEC SQL處理過程:含嵌入式SQL語句的主語言程序預編譯程序轉換嵌入式SQL語句為函數調用轉換后的主語言程序(形式上消除了SQL)主語

2021-10-21 11:51:00 4

4 ? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設計和仿真非常重要。 Verilog語言中講的阻塞賦值

2021-12-02 18:24:36 5005

5005

IO方向寄存器語句生成器,非常方便寄存器版本操作哦

2022-02-15 14:04:27 2

2 初學者階段編程時,編寫基本語句可能會有隱含錯誤的方式,基本語句主要針對if、for、while、goto、switch等,它們看似簡單,但使用時隱患比較多,本文歸納了使用語句的一些規則和建議,希望能對大家有所幫助。

2022-04-27 12:53:16 1329

1329 begin_end順序塊,用于將多條語句組成順序塊,語句按順序一條一條執行(除了帶有內嵌延遲控制的非阻塞賦值語句),每條語句的延遲時間是相對于由上一條語句的仿真時間而言;

2022-05-18 10:29:25 1085

1085 當前文章復盤C語言的: 位運算運算符、基本運算符、數據類型、變量、for語句、while語句、goto語句、switch語句、運算符優先級強制轉換等。

2022-08-14 09:39:03 721

721 總結C語言語句的幾個基本練習題,計算素數、排序、求偶數和、可逆素數、水仙花數、交換大小寫、交換變量的值、位運算、語法特性等知識點。

2022-08-14 09:46:53 703

703 IF語句:IF語句讓你根據條件是TRUE或FALSE來支配兩個分支之一的程序運行。

2022-08-17 10:02:03 648

648 在上面的代碼中,初始化語句是int s = check()。s的生命周期是整個if語句,這里也包含else語句。

2022-10-14 10:50:37 976

976 決策語句(Decision statements)允許程序塊的執行流程根據設計中信號的當前值分支到特定語句。

2022-10-21 08:58:27 2185

2185 SystemVerilog case語句與C switch語句類似,但有重要區別。SystemVerilog不能使用break語句(C使用break從switch語句的分支退出)。case語句在執行分支后自動退出(使用break退出case語句是非法的。),不能執行break語句。

2022-10-27 08:57:28 622

622 跳轉語句允許程序代碼跳過一個或多個編程語句,SystemVerilog的jump語句是continue、break和disable。

2022-11-09 09:23:52 1053

1053 迭代語句主要用于重復執行的程序,在 CoDeSys 中,常見的迭代語句有 FOR,REPEAT 及WHILE 語句。

2023-01-30 17:45:29 1695

1695 決策語句(Decision statements)允許程序塊的執行流程根據設計中信號的當前值分支到特定語句。SystemVerilog有兩個主要的決策語句:if…else語句和case語句,使用關鍵字case、case…inside,casex和casez。

2023-02-09 14:15:27 625

625

條件判斷語句,作為任何編程語言都不可缺少的內容,在C語言中也不例外。條件判斷語句可以讓程序的功能更加復雜,從而實現各種各樣的功能。

2023-02-21 15:24:38 2290

2290

在循環的過程中如果要退出循環,我們可以用break語句和continue語句。

2023-02-23 11:17:43 1853

1853 在Java學習中我們見過很多有意思的語句if語句、for語句、while語句和switch語句等。今天我們介紹的是switch語句,經過我個人的理解我覺得switch語句是一種可以判斷的語句,但前提是變量需要和case后面的數是一樣的他才會進入執行。

2023-03-08 11:03:13 765

765

語句1和語句2可以是一個簡單的語句,也可以是一個復合語句,還可以是另一個if語句。

* 方括號內的部分(即else子句)為可選的,既可以有,也可以沒有

2023-03-09 11:05:46 1147

1147 除了可以用while語句和do...while語句實現循環外,C語言還提供for語句實現循環,而且for語句更為靈活,不僅可以用于循環次數已經確定的情況,還可以用于循環次數不確定而只給出循環結束條件的情況,它完成可以代替while語句。

2023-03-09 11:14:19 750

750 在 Python 中,if...else 是一種條件語句,可以根據給定的條件執行不同的操作。這個語句通常用于控制程序的流程。

2023-04-19 15:39:51 505

505 我們在上一篇文章中已經看到了如何使用程序塊(例如 always 塊來編寫按順序執行的 verilog 代碼。

我們還可以在程序塊中使用許多語句來控制在我們的verilog設計中信號賦值的方式

2023-05-11 15:37:36 2835

2835

哈嘍大家好,我是知道。今天帶大家了解下Python的循環語句 定義循環語句允許我們執行一個語句或語句組多次 類型Python提供了兩種不同類型的循環 for循環:重復執行語句 #打印1-10for

2023-05-11 17:39:33 595

595 本文主要介紹verilog常用的循環語句,循環語句的用途,主要是可以多次執行相同的代碼或邏輯。

2023-05-12 18:26:43 1140

1140 條件語句和循環語句是計算機編程中常用的兩種控制結構

2023-07-21 16:48:09 5583

5583

條件判斷 語句塊 什么是語句塊呢? 語句塊是在條件為真(條件語句)時執行或者執行多次(循環語句)的一組語句。在代碼前放置空格來縮進語句即可創建語句塊。 關于縮進: 使用tab鍵也可以縮進語句

2023-09-12 16:41:56 548

548 if語句 對于if語句,若條件判定為真,那么后面的語句塊就會被執行。若條件判定為假,語句塊就會被跳過,不會執行。 1 #if語句 2 age = 20 3 if age >= 18

2023-09-12 16:45:28 326

326 SELECT語句是SQL(Structured Query Language,結構化查詢語言)中的一種查詢語句,用于從數據庫中檢索數據。它是數據庫操作中最常用和基本的語句之一。在本文中,我將為您詳盡

2023-11-17 16:23:19 550

550 在Python中,可以使用多個條件來編寫if語句。這些條件可以使用邏輯運算符進行組合,包括and、or和not。 當if語句中有多個條件時,可以使用邏輯運算符將這些條件組合在一起。and運算符表示

2023-11-21 16:45:04 643

643 Oracle數據庫是一種常用的關系型數據庫管理系統,具有強大的SQL查詢功能。Oracle執行SQL查詢語句的步驟包括編寫SQL語句、解析SQL語句、生成執行計劃、執行SQL語句、返回結果等多個階段

2023-12-06 10:49:29 331

331 單片機中的for語句是一種常見的循環控制結構,用于重復執行一段代碼塊,可以簡化程序的編寫和減少代碼量。本文將詳細介紹單片機中for語句的運用。 一、for語句的基本結構和功能 for語句是一種迭代

2024-01-05 14:02:03 351

351 單片機中的if語句是一種條件語句,用于根據不同的條件執行不同的代碼塊。在程序執行過程中,條件語句用來決定是否執行特定的代碼段。在單片機編程中,if語句是最常見和最基礎的一種條件語句。 if語句通常

2024-01-05 14:04:12 242

242 Assign語句和Always語句是在硬件描述語言(HDL)中常用的兩種語句,用于對數字電路建模和設計。Assign語句用于連續賦值,而Always語句用于時序邏輯建模。本文將詳細探討這兩種語句

2024-02-22 16:24:35 245

245

電子發燒友App

電子發燒友App

評論