Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

2023-11-14 17:49:43 736

736

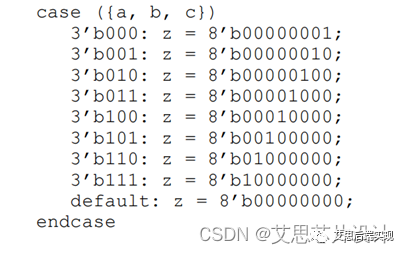

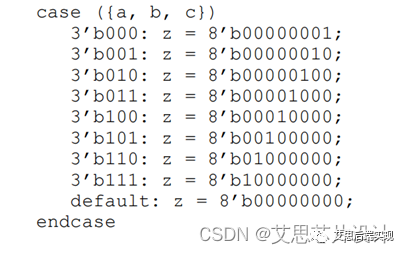

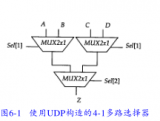

對于前端設計人員,經常會需要一個MUX來對工作模式,數據路徑進行明確(explicit)的聲明,這個對于中后端工程師下約束也很重要。這里介紹一種巧用的RTL原語,實現MUX的方法。

2023-12-14 16:26:33 424

424

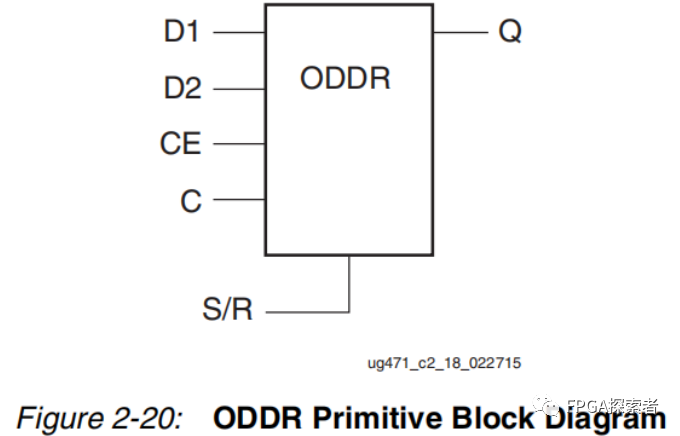

今天用了PLL的IP核,但是提示要用ODDR2才能把輸出的時鐘信號輸出到FPGA的普通IO口上,求大神指導,什么是ODDR2,怎么使用,還有就是怎么在ISE上查看它的接口?

2016-12-14 11:22:23

嗨,我附上了一個非常簡單的ISE項目。我有一個2位自由運行計數器(cnt)指望clk的上升沿。 cnt輸出定向到兩個ODDR2實例的D0輸入。 ODDR2的D1輸入設置為“0”,C0設置為clk

2019-07-08 07:02:01

嗨,我復制在頂級模塊中粘貼下面的ODDR代碼,但它顯示了一些錯誤。我可以知道我還應該做些什么嗎?謝謝最好的祝福

2020-05-07 08:45:00

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

`Xilinx FPGA入門連載40:SRAM讀寫測試之設計概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示,本

2015-12-18 12:57:01

Xilinx FPGA入門連載43:FPGA片內ROM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-06 12:22:53

Xilinx FPGA入門連載47:FPGA片內RAM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-20 12:28:28

Xilinx FPGA入門連載51:FPGA片內FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-02-26 10:26:05

指南 -- Modelsim仿真驗證Lesson13 特權Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之功能概述Lesson14 特權Xilinx FPGA SF-SP6入門指南

2015-07-22 11:49:20

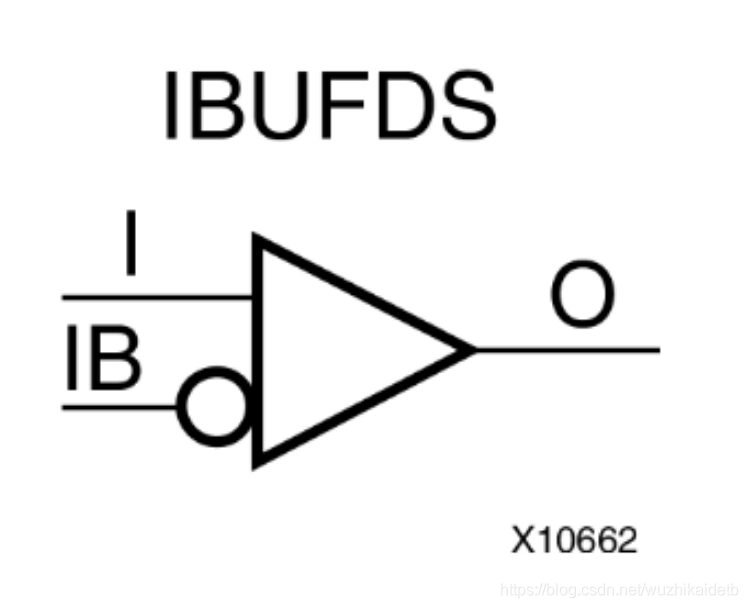

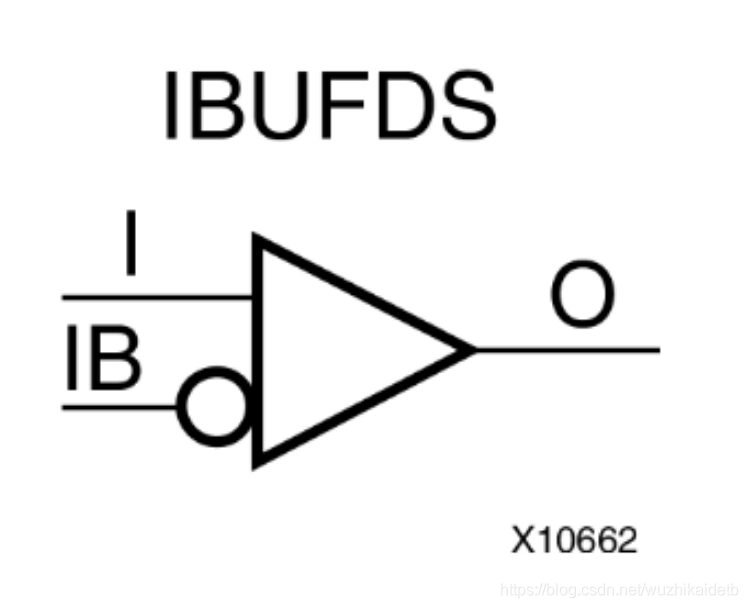

。 2實現 Xilinx 7系列的差分信號的實現主要通過IBUFDS、OBUFDS、IOBUFDS等原語的調用,在程序中直接進行原語的例化,以IBUFDS和OBUFDS為例: 2.1IBUFDS

2020-12-23 17:17:47

Xilinx原語使用方法

2021-02-22 06:55:53

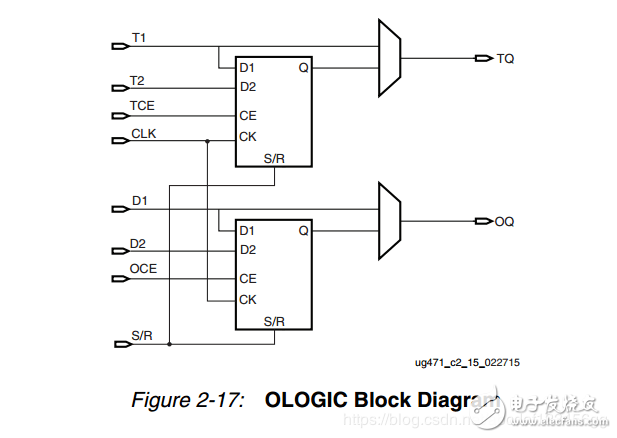

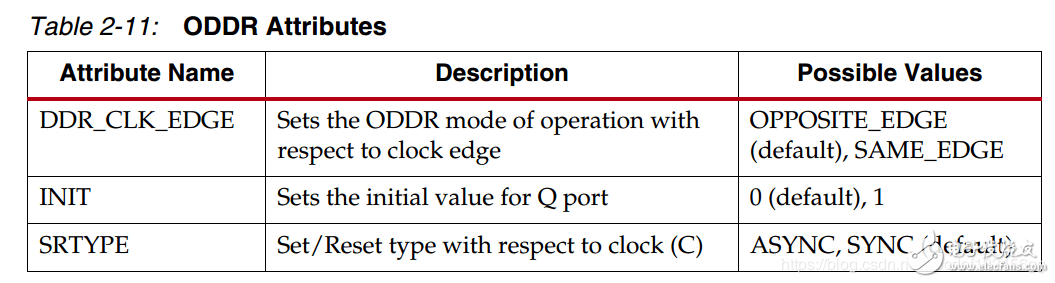

個MUX。利用這種2+1的組合可以產生DDR操作,Xilinx稱之為ODDR2。每個存儲單元都有6個接口信號:時鐘+時鐘時能,數據輸入+輸出,置位復位+翻轉輸入除了這些信號,存儲單元還有一些屬性設置

2012-08-02 22:48:10

我看到別人寫的項目 程序中用了很多原語,比如輸入時鐘要設置一個IBUFG,有一些輸出信號接一個OBUFG,那么原語的好處是什么?如何知道什么時候要使用原語!

2017-07-13 19:59:37

器件結構及描述3.1 概述3.2 Spartan-ⅡE系列FPGA3.3 Spartan-3系列FPGA3.4 本章小結第4章 ISE 6.x設計工具簡介和使用4.1 概述4.2 Xilinx設計流程

2012-02-27 14:43:30

Xilinx工具:vivado在該圖中,TX_CLK_i連接到pll_x1模塊的輸入時鐘。然后,pll_x1的輸出時鐘連接到ODDR。接下來,ODDR的輸出引腳將連接到I / O引腳

2020-05-04 08:04:41

找到任何關于算法類型和基元類型的約束。如果有,我將使用更少的BRAM資源。Xilinx是否具有用于推斷RAM的算法類型和原語類型?我使用的是Vivado 2014.4和Kintex-7設備。 謝謝大家。

2020-03-31 07:45:01

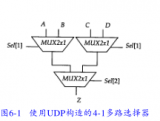

`[tr=transparent]BUFMUX原語是2輸入1選擇1輸出,現在我想改成2位位寬的s選擇信號,達到一個四輸入的BUFMUX,請問有什么辦法可以實現,如果級聯?圖片最下面這個控制信號是2位的[/tr]`

2018-03-23 15:18:46

`BUFMUX原語是2輸入1選擇1輸出,現在我想改成2位位寬的s選擇信號,達到一個四輸入的BUFMUX,請問有什么辦法可以實現,如果級聯?圖片最下面這個控制信號是2位的`

2018-03-23 15:12:31

使用xilinx spartan6,在工程中使用原語生成DDR控制器mig文件,DDR數據管腳定義發生改變,需要重新分配管腳,求告知,這個管腳分配要怎么弄

2016-07-19 09:54:37

CANOpen系列教程07_CANOpen協議概述

2020-12-31 06:10:32

用于xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA如何將xilinx LUT作為移位寄存器?什么是xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA的CLB結構。這個FPGA上有哪些額外的原語?

2020-06-16 16:48:59

Gowin FPGA原語使用指南

2022-09-30 06:59:55

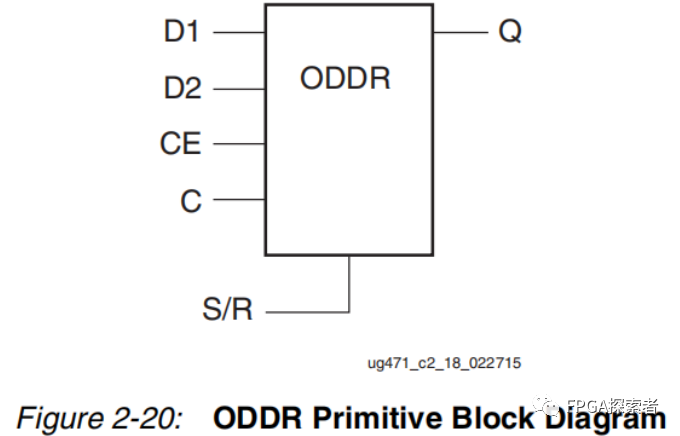

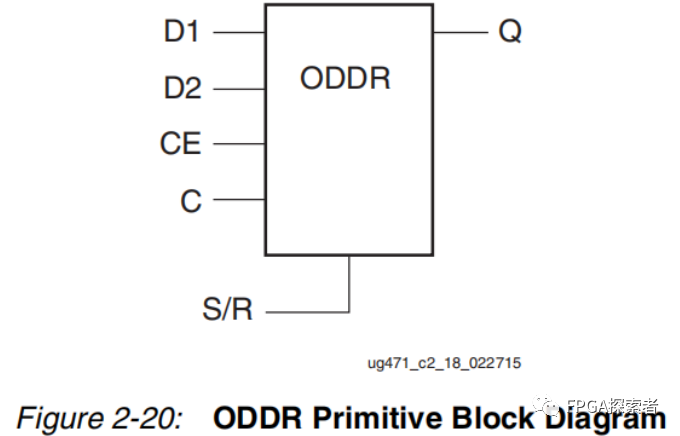

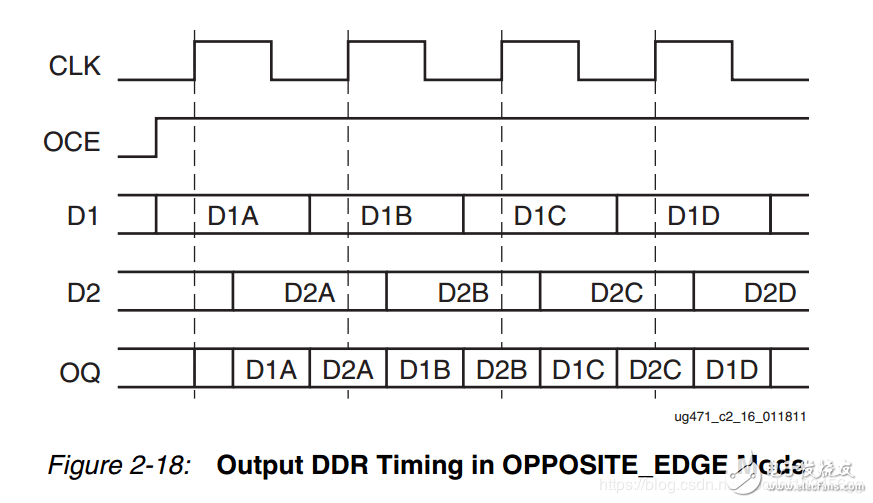

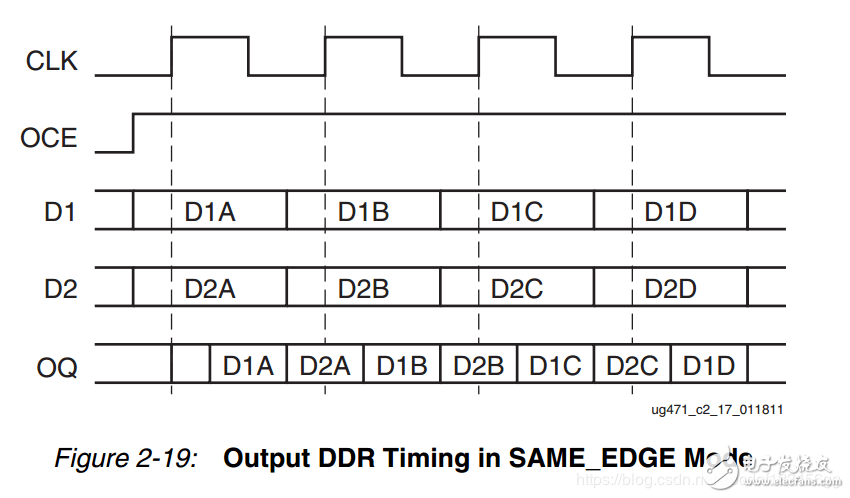

IDDR與ODDR的簡述RGMII時序簡述千兆網輸入與輸出模塊的設計測試模塊的設計仿真測試結果總結

2021-01-22 06:09:37

SelectIO接口使用IDDR原語執行4x異步過采樣。時鐘由MMCM或PLL原語生成,并通過BUFG時鐘網絡路由,并可使用器件內任何選定的輸入對單端或差分信號進行操作。XAPP523是由MMCM

2020-08-11 10:59:59

我正在使用ODDR2生成外部時鐘(ISE = 13.1,Planahead = 13.1):clk5m_inst:ODDR2通用映射(DDR_ALIGNMENT =>“NONE”, - 將輸出

2019-06-17 14:43:06

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

如圖,在書上看到的一個小例程,然后用quartusii V14.1對其進行綜合,顯示Verilog不能合成MOS開關門原語。這段代碼是在康華光的第五版的數電上看到的啊,為什么不能綜合?

2017-06-03 15:54:37

程序里,tx_data_oddr_s[l_inst]經OBUFDS輸出兩個正交的量,一路作為I(tx_data_out_p),一路作為Q(tx_data_out_n)進入AD9361輸入引腳。應該是

2016-01-15 17:51:39

://www.xilinx.com/support/answers/35032.htm解決方案是使用ODDR2實例化(時鐘轉發技術),其中時鐘信號不直接驅動負載引腳,而是充當ODDR2的輸入,然后ODDR2的輸出

2018-10-17 14:28:54

時鐘編譯報錯,好好的東西在QUARTUS里面也沒有報錯啊,經過各種分析發現,XILINX的時鐘處理很麻煩,時鐘不能直接輸出到IO,需要加ODDR,然后才能接到IO中,這個ODDR我是添加了,但是一直

2017-08-17 23:37:42

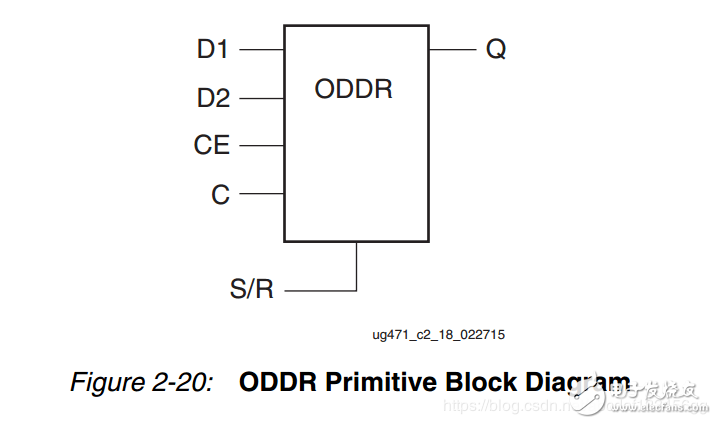

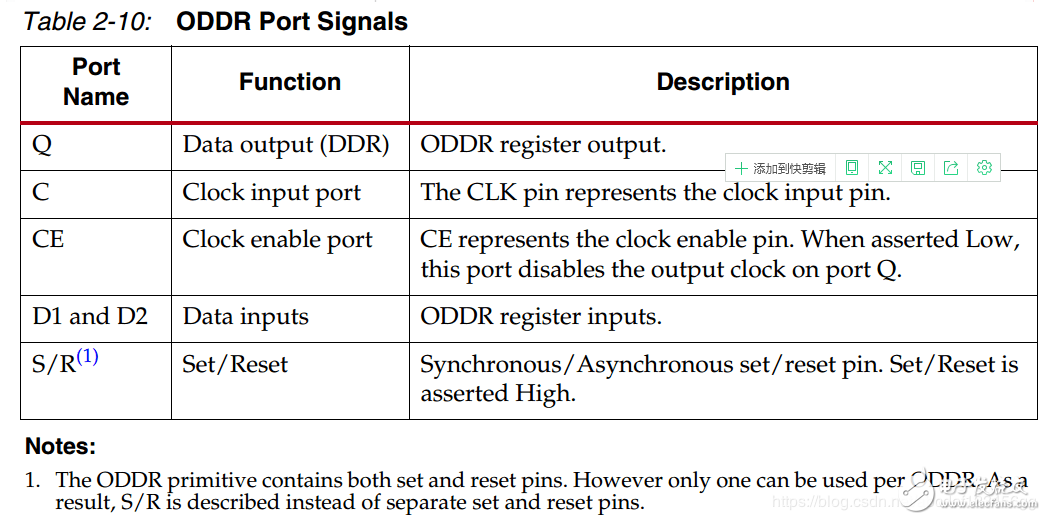

。 IDDR與ODDR的簡述 這里的表述,我們主要依靠技術手冊來給大家進行講解。 簡單的框圖顯示如下: 其中IDDR的原語如下: IDDR #( .DDR_CLK_EDGE

2021-01-15 16:41:12

你好我將virtex5 LX50與具有應根據standardEIA / TIA-644 LVDS規范終止的輸出數據的設備連接起來我在用著IBUFDS用于將輸入LVDS轉換為LVTTL,OBUFDS用于輸出信號和時鐘這是這樣做的正確方法為此目的使用ODDR原語的重要性是什么?問候uzmeed

2020-06-17 14:59:44

問候,兩個與ODDR相關的問題:1)如果我想將由同一個BUFG驅動的同一時鐘轉發到多個外部設備,我是否必須實例化幾個ODDR?或者,如果我只是實例化一個ODDR并將輸出驅動到指向外部設備的多個

2018-11-02 11:28:55

嗨,在post place and route genererated .vhd文件中有一個組件實例化X_FF。我已經搜索到了描述X_FF的等效xilinx原語(觸發器),但發現了很多。我想xilinx原始X_FF描述IN VIRTEX 7 BO ??謝謝Manasa Thoonoli

2020-04-06 17:34:42

嗨,我正在使用Planahead 14.6 - 來自Xilinx的人可以在OVERSAMPLE模式下確認Kintex-7中ISERDES原語的實際位順序輸出是什么嗎?我問的原因是,由于大多數這種

2020-08-14 08:00:57

IamusingtheSpartan7inmydesign。我發現我可以直接將MMCM的輸出連接到FPGA端口。我想知道在不使用ODDR的情況下轉發時鐘有什么意義嗎?

2020-08-25 15:55:37

親愛的大家,Virtex中的許多原語在Spartan 6中找不到,例如BUFIO,BUFR,IDELAY,IDDR。如何使用Spartan原語實現類似的功能?非常感謝你!箱子以上來自于谷歌翻譯以下

2019-06-03 10:31:21

嗨,我正在使用斯巴達-6和12.3 ISE。我必須從FPGA輸出60 MHz到ADC的時鐘。對于這個部分,我從時鐘發生器IP內核獲得60 MHz并將其饋送到ODDR2的一個輸入,并將反相時鐘饋送

2019-07-30 09:47:00

我有一個從Core Generator生成的模塊,它使用來自100Mhz輸入時鐘的PLL_base原語生成時鐘。現在由于一些錯誤,我不得不在原語的輸出中添加一個非門和一個ODDR2,我通過編輯由核心

2019-05-31 06:56:29

你好,我最近正在進行FPGA測試工作,我碰巧使用xilinx文檔中描述的回讀捕獲UG191.i可以使用回讀驗證功能回讀配置存儲器數據,但我無法使用CAPTURE_VIRTEX5原語讀回FF

2020-06-11 08:37:48

你好!我想在Kintex 7(XC7K410T)設計中實現PLLE2_BASE原語,但實例化原語時不會突出顯示。此外,我收到不支持CLKFBOUT_MULT屬性的警告。誰能告訴我我做錯了什么?這是

2020-07-18 18:21:08

大家好,我無法找到IODRP2_MCB原語的任何文檔。Xilinx文檔中唯一提到它的地方是用于HDL設計的Spartan-6庫指南(UG615-v12.1,第138頁),其中包含指向其他文檔的鏈接

2019-05-24 13:06:19

有什么方法可以使用SEM和CAPTURE原語嗎?我是否激活了CAPTURE,SEM可以重新計算ECC的幀數變化了嗎?或將永遠失去?謝謝中號

2020-06-16 16:41:14

嗨!我想知道BUFIO2 + BUFG和ODDR2的解決方案是否用于時鐘路由在時鐘源上可以避免使用Spartan 6(使用直接賦值)已經從外部緩沖了。我的意思是,而不是 bufio2_axi_clk

2018-10-23 10:24:05

嗨,有沒有辦法在7系列FPGA中讀取18位串行LVDS輸入,尤其是Artix-7?如果我理解正確,ISERDESE2原語僅支持最多14位輸入。數據速率約為400 Mbps,采用2線DDR傳輸模式。先謝謝你,

2020-04-24 09:33:25

嗨, 我想得到一些關于k7原語的詳細信息(更具體的oserdes和iserdes)。我發現了一個關于v6 hdl原語的UG。 k7有類似的UG嗎?我沒找到它。謝謝。

2020-08-24 09:48:20

美好的一天,我對IOB中的ODDR2觸發器有疑問。現在我實例化以下內容:ODDR2_1:ODDR2通用映射(DDR_ALIGNMENT =>“NONE”, - 將輸出對齊設置為“NONE

2019-07-23 10:24:11

大家好,我是使用Xilinx ISE和編程FPGA的新手。我開發了一個程序來模擬DDR SDRAM用于測量目的。我使用了許多原語,如Blockram(IP CORE gen工具),DCM,ODDR

2019-05-08 13:07:02

器件定義

軟件工具概述

選擇配置模式

編程/配置選項

XILINX的通用配置/編程的裝置

2010-06-22 16:24:01 78

78 本書系統地論述了Xilinx FPGA開發方法、開發工具、實際案例及開發技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發基礎與進階、Xilinx FPGA電路原理與系統設計

2012-07-31 16:20:42 11268

11268

Xilinx FPGA工程例子源碼:PCI Express標準概述白皮書

2016-06-07 14:13:43 13

13 xilinx原語的使用,建議有一定經驗的參考。

2016-12-17 11:58:56 13

13 當ISE調用ModelSim進行仿真的時候,如果在FPGA設計中使用了Xilinx提供的的IP core或者其他的原語語句,ModelSim不添加Xilinx相應的庫文件的話,是無法仿真的。

2017-02-11 15:22:37 1274

1274

IBUFGDS輸入全局時鐘及DCM分頻使用

2017-02-11 16:16:11 4629

4629 xilinx 原語使用方法

2017-10-17 08:57:42 11

11 xilinx原語使用方法

2017-10-19 08:50:39 15

15 基于SRL16的分布式RAM不再支持V5、S6和V6等器件,但是SRL16是所有XIlinx器件都支持的,并且在設計中應用非常頻繁,因此可通過調用原語的方法來調用SRL16E甚至SRL32E來實現原來ISE分布式RAM IP核的設計。

2018-05-05 10:38:00 7011

7011 了解如何使用Xilinx SDK調試u-boot代碼。

概述了技術以獲得重定位偏移量,以便可以在SDK中應用它。

2018-11-27 06:36:00 3722

3722 了解Xilinx SDK如何為您提供在Zynq全可編程器件上創建,開發,調試和部署嵌入式軟件應用所需的所有工具。

該視頻為您提供了Xilinx SDK的全面高級概述。

2018-11-26 07:12:00 5721

5721 了解Xilinx FSBL如何操作以啟動Zynq器件。

包括程序執行概述,調試技巧以及有關特定引導設備的信息。

還包括FSBL角度的啟動安全性簡要概述。

2018-11-23 06:32:00 4237

4237 項目中主要用到的原語與IO端口有關,所以基本在Input/Output Functions 和IO兩類中。下面著重介紹實際中所用到的幾個原語,芯片A7系列。

2019-01-06 11:23:11 15706

15706

UltraRAM 原語(也稱為 URAM)可在 Xilinx UltraScale +? 架構中使用,而且可用來高效地實現大容量深存儲器。

2019-07-13 11:08:09 6669

6669

首先,什么是XPM?可能很多人沒聽過也沒用過,它的全稱是Xilinx Parameterized Macros,也就是Xilinx的參數化的宏,跟原語的例化和使用方式一樣。

2020-03-08 16:46:00 6952

6952 在7系列設備的ILOGIC block中有專屬的registers來實現input double-data-rate(DDR) registers。這些特性可以通過實例化IDDR 原語實現。

2020-12-28 17:13:13 13

13 注意:ODDR與IDDR工作有一個復位時間,大概110-120ns之間

IDDR是上升沿采一次數據,下降沿采一次數據,形成的雙路數據在下一個時鐘沿輸出。

2020-12-30 16:27:49 16

16 高速串行信號,經過傳輸媒體(光纜或銅線),最后在接收端高速串行信號重新轉換成低速并行信號。這種點對點的串行通信技術充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,提升信號的傳輸速度,從而大大降低通信成本。xilinx 7系列通過原語調用serdes接口,就可

2020-12-31 17:30:59 15

15 Xilinx公司的原語按照功能分為10類,包括:計算組件、I/O端口組件、寄存器和鎖存器、時鐘組件、處理器組件、移位寄存器、配置和檢測組件、RAM/ROM組件、Slice/CLB組件以及G比特收發器組件。下面分別對其進行詳細介紹。

2022-02-08 14:01:49 1092

1092

只能發生在FPGA的IOB上面,這里有特定的硬件結構可以實驗上面單沿變雙沿的方法,也就是使用原語進行一些列的操作。

2021-01-25 07:07:04 12

12 用戶定義的原語 在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。 U D P的實例語句與基本門的實例語句完全相同

2021-03-05 15:30:36 1426

1426

1 IDDR ? 1.1 介紹 該設計元素是專用的輸入寄存器,旨在將外部雙數據速率(DDR)信號接收到Xilinx FPGA中。IDDR可用的模式可以在捕獲數據的時間和時鐘沿或在相同的時鐘

2021-03-05 18:11:20 8577

8577

Xilinx公司的原語按照功能分為10類,包括:計算組件、I/O端口組件、寄存器和鎖存器、時鐘組件、處理器組件、移位寄存器、配置和檢測組件、RAM/ROM組件、Slice/CLB組件以及G比特收發器組件。下面分別對其進行詳細介紹。

2021-03-24 06:14:29 3

3 (29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 IBUFDS、和OBUFDS都是差分信號緩沖器,用于不同電平接口之間的緩沖和轉換。IBUFDS 用于差分輸入,OBUFDS用于差分輸出。

2022-02-16 16:21:27 3157

3157

Xilinx SelectI IP是一個VHDL/Veilog封裝文件,根據用戶配置生成實例化的I/O邏輯,滿足了輸入SERDES、輸出SERDES和延遲模塊的應用要求。另外,它也可以例化生成所需的I/O時鐘原語,將它連接到I/O引腳。

2022-06-06 09:46:43 1557

1557 在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。

2022-08-08 11:46:46 733

733 電子發燒友網站提供《Gowin原語用戶指南.pdf》資料免費下載

2022-09-15 11:57:38 1

1 在SDR接口中,ODDR轉發時鐘(仍在時鐘樹內),輸出端要直連到輸出port,不可加邏輯,連接方式:輸出時鐘連接ODDR的C引腳,D1固定值1'b1, D2固定值1'b0,CE固定值1’b1,ODDR的輸出Q連接到OBUF;

2023-06-21 14:11:06 829

829

在SDR接口中,ODDR轉發時鐘(仍在時鐘樹內),輸出端要直連到輸出port,不可加邏輯

2023-06-27 10:21:18 4303

4303

電子發燒友App

電子發燒友App

評論