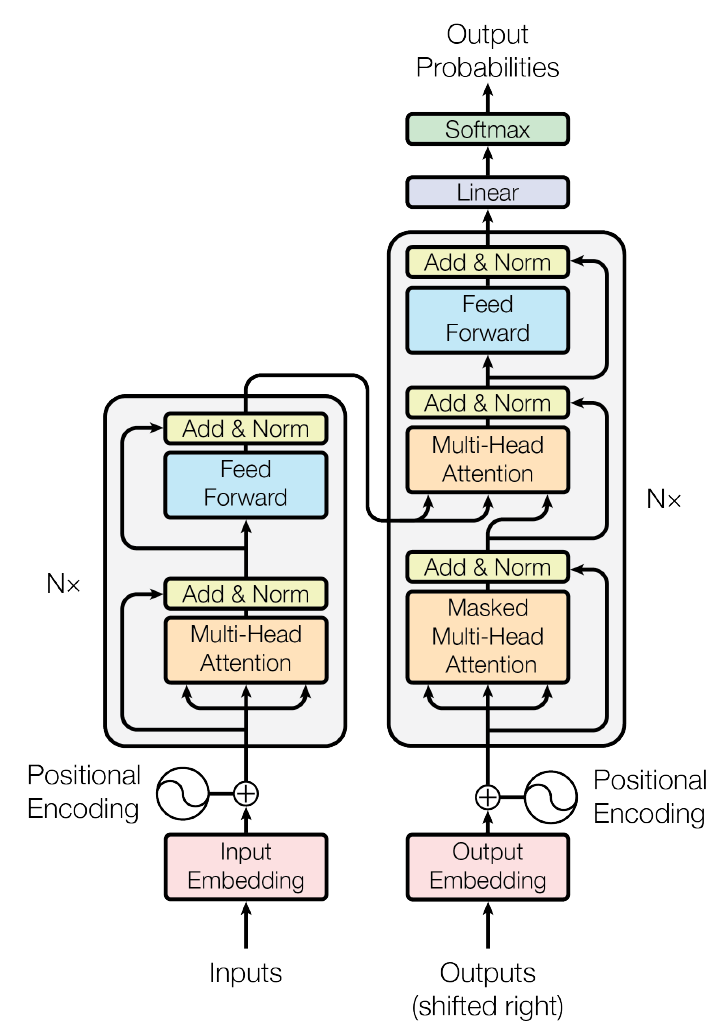

前言 AI芯片(這里只談FPGA芯片用于神經網絡加速)的優化主要有三個方面:算法優化,編譯器優化以及硬件優化。算法優化減少的是神經網絡的算力,它確定了神經網絡部署實現效率的上限。編譯器優化和硬件優化

2020-09-29 11:36:09 4383

4383

我是大數據方向的研究僧,導師讓加速一個基因組學的算法,需要用到FPGA,但因為實驗室并不是主攻這個方向的,所以不打算買開發板。請問各路大神,有沒有相關模擬器或仿真器可以讓我不買開發板就能跑程序的?

2018-05-29 15:31:04

我用C寫了一個17維的平方根容積卡爾曼濾波程序,結果迭代一次速度為0.26s,加了-o3為0.052s,但現在還不滿足要求,算法中基本都是for循環。想請問一下,該如何優化程序,怎么充分發揮DSP的硬件優勢?要不要配置定點/浮點,還有為什么沒有乘法的浮點庫?

2019-09-02 11:11:13

采集數據中的量化噪聲,在進行數據壓縮前采用濾波的預處理技術。介紹LZW算法和滑動濾波算法的基本理論,詳細闡述用單片FPGA實現兩種算法的方法。最終測試結果表明,該設計方案能夠有效濾除數據中的高頻噪聲

2010-04-24 09:05:21

速度換面積 速度優勢可以換取面積的節約。面積越小,就意味著可以用更低的成本來實現產品的功能。速度換面積的原則在一些較復雜的算法設計中常常會用到。在這些算法設計中,流水線設計常常是必須用到的技術。在

2016-09-28 16:14:51

性,流水線設計正是利用了并發性,大大提高了硬件處理性能,但是流水線設計,對算法的前后依賴關系有一定要求,不同流水線的算法處理要解耦才能保證并發的最大效率。為了發揮FPGA硬件實現的速度優勢,算法進行優化

2018-08-01 09:55:53

換面積速度優勢可以換取面積的節約。面積越小,就意味著可以用更低的成本來實現產品的功能。速度換面積的原則在一些較復雜的算法設計中常常會用到。在這些算法設計中,流水線設計常常是必須用到的技術。在流水線

2015-12-03 16:41:21

換面積 速度優勢可以換取面積的節約。面積越小,就意味著可以用更低的成本來實現產品的功能。速度換面積的原則在一些較復雜的算法設計中常常會用到。在這些算法設計中,流水線設計常常是必須用到的技術。在流水線

2017-06-01 10:31:59

了一系列優化算法,但是用戶仍有必要遵循一定的編碼風格去引導 綜合工具在特定 FPGA 架構上達到最優結果。 設計規劃用于指導用戶把設計更好地適配到所選用的 FPGA上并合理地 平衡面積和速度的要求,目的

2022-09-29 06:12:02

計算機時發明的。這是一種設計用于計算數學函數、三角函數和雙曲函數的簡單算法。這種算法的真正優勢在于只需要采用極小型的 FPGA封裝就可以實現它。CORDIC 只需要一個小型查找表,加上用于執行移位和加

2019-09-19 09:07:16

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

本人學生,在實驗室打算做EMD算法的硬件實現,看了一些論文,感覺主要是單獨用FPGA實現,或者用DSP+FPGA實現(DSP做EMD算法,FPGA做數據流控制),請問大家用哪種架構做硬件實現EMD算法比較好?

2018-04-25 21:04:33

請問我要做工程中的實時控制,實現一些控制算法,比如模型預測控制、模糊控制、自適應控制、神經網絡控制等,用哪種型號的開發板最合適。剛接觸硬件,要對一個對象進行控制,需要哪些硬件?

2020-07-16 16:57:37

是借助于EDA開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜用目標器件來實現。 FPGA器件采用邏輯單元陣列(LCA

2008-06-26 16:16:11

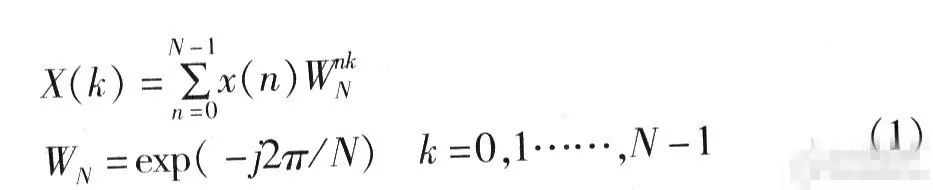

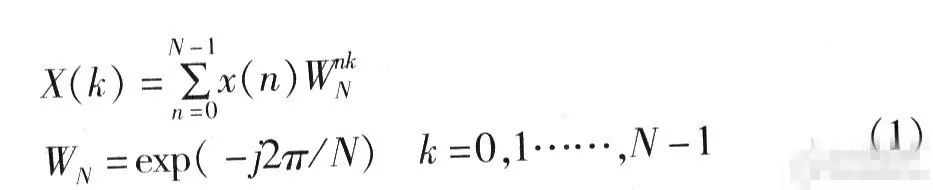

FPGA實現的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數據吞吐量。中間數據緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統的性能。傳統的實現方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

,使用HDL編碼器自動生成HDL代碼具有眾多明顯優勢。工程師可以快速地評估能否在硬件中實施當前算法;迅速評估不同的算法實現,選擇最佳方案;并在FPGA上更快地建立算法原型。 對于DDC案例研究而言

2018-09-04 09:26:53

因子參數a k 、b k 和u k 進行全局優化,充分發揮模糊控制器的魯棒性。仿真結果表明,采用PSO算法進行PID 參數優化的數控機床交流伺服系統的運動控制具有很強的魯棒性和動態性能,是一種切實可行

2009-05-17 11:38:44

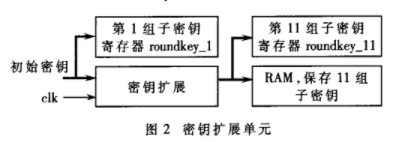

,它的局限性也逐漸暴露出來.在很多計算機信息安全系統中,硬件加密手段被應用到設備中來提高密碼運算速度和系統的安全性. 給出了一種RC4加密算法的FPGA實現方案,相比用軟件實現,該方案速度更快,安全性更高

2012-08-11 11:48:18

一個設計缺陷,你可以立即對其進行重新編程設計。FPGA還允許你實現硬件運算功能,而這在以前的實現成本是很高的。CPU流水線與FPGA邏輯之間緊密結合,這樣就可以創建高性能軟件加速器。圖1的模塊框圖顯示

2015-02-02 14:18:19

項目名稱:圖像目標識別FPGA硬件加速試用計劃:申請理由 本人供職于一家AI公司,現在在使用FPGA硬件加速相關目標檢測算法的端側實現(鑒黃/司機行為識別),公司已經有非常成熟的軟件算法以及GPU

2019-01-09 14:51:09

FPGA算法工程師職責:1. 基于FPGA的圖像處理算法設計實現;2. 與團隊配合,對FPGA實現算法進一步優化;3. 根據整體工程分配子任務,進行詳細方案設計并寫入文檔;4. 根據詳細方案進行

2017-06-08 15:36:18

中,數字信號處理系統經常要進行高速、高精度的FFF運算。現場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數字信號處理算法的物理結構。用FPGA實現FFT處理器具有硬件系統簡單、功耗低的優點

2019-07-03 07:56:53

并行計算。在進行FFT 這類并行運算為主的算法時,采用FPGA的優勢不言而喻。用FPGA實現FFT算法進行諧波檢測成為了一大熱點。 以往FPGA的設計主要依靠硬件描述語言來完成。Xilinx公司推出了專門

2019-06-21 06:25:23

什么是AES算法?如何對AES算法進行優化?怎樣快速實現AES算法?

2021-04-28 06:51:19

,優化這些算法的執行,這些產品通常是大批量生產。終端用戶產品必須能以合理的成本對處理算法進行升級。 硬件/軟件的權衡 最佳算法實現的基本經驗是,硬件是為了實現更高的性能,軟件是為了實現靈活性

2008-09-27 11:42:55

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開始科創,老師給了我們一個題基于FPGA的FFT算法硬件實現。但是什么都不會,想找些論文看看,求相關的論文

2012-05-24 22:14:40

` 本帖最后由 ninghechuan 于 2017-8-30 08:20 編輯

我們為了實現動態圖像的濾波算法,用串口發送圖像數據到FPGA開發板,經FPGA進行圖像處理算法后,動態顯示到

2017-08-28 11:34:10

上的損失。代碼實現部分如下。下面是官方給的RGB888 to YCbCr的算法公式,我們可以直接把算法移植到FPGA上,但是我們都知道FPGA無法進行浮點運算,所以我們采取將整個式子右端先都擴大256

2017-10-28 08:48:57

硬件是用DSP來實現的;FPGA技術近兩年才達到可以實現大點數FFT的水平,并且體積、速度、靈活性等各種性能都優于DSP,但開發難度大,研制費用高。本文將討論基于FPGA的大點數超高速FFT算法。

2009-06-14 00:19:55

轉帖摘要: 針對嵌入式軟件無法滿足數字圖像實時處理速度問題,提出用硬件加速器的思想,通過FPGA實現Sobel邊緣檢測算法。通過乒乓操作、并行處理數據和流水線設計,大大提高算法的處理速度。采用模塊

2017-11-29 08:57:04

,一般情況下,速度指標是首要的,在滿足速度要求的前提下,盡可能實現面積優化。因此,本文結合在設計超聲探傷數據采集卡過程中的CPLD編程經驗,提出串行設計、防止不必要鎖存器的產生、使用狀態機簡化電路描述、資源共享,利用E2PROM芯片節省片內資源等方法對VHDL電路進行優化。

2019-06-18 07:45:03

本文介紹基于TMS320VC5509A DSP的JPEG視頻壓縮系統的設計和實現方案,該系統硬件設計采用DSP+FPGA的方案,充分發揮了各自優勢;而軟件設計針對C55x的結構進行程序結構和算法優化,經過驗證達到較好的實時效果。

2021-06-02 06:25:48

耗費了FFT運算中大量的乘法器資源。CORDIC算法只需簡單的移位與加減運算就能實現向量旋轉,具有使用資源少、硬件規模小等優勢。因此在FFT蝶形運算中用其代替傳統FFT運算中的復數乘法器,可以獲得更好

2011-07-11 21:32:29

如何優化算法,也根據不同的處理器自帶的協處理器或者硬件指令進行調整。引言??電機控制應用設計傳統上采用微控制器(MCU)或數字信號處理器(DSP)來運行電機控制算法。在研究永磁同步電機(PMSM)...

2021-08-30 07:57:28

=64 點的基-4DIT信號流其輸入數據序列是按自然順序排列的,輸出結果需經過整序。64點數據只需進行3次迭代運算,每次迭代運算含有N/4=16個蝶形單元。2 FFT算法的硬件實現2.1 流水線方式

2019-06-17 09:01:35

便攜式設備的存儲器要求是什么?如何在便攜式應用中充分發揮FPGA的優勢?

2021-05-06 08:10:01

如何對CCSDS圖像壓縮算法編碼進行優化?

2021-06-02 06:03:46

TDSDM642是TI公司推出的定點DSP芯片,具有性價比高、運算速度快的優點,但是定點DSP對于浮點運算比較困難,因此在系統實現時需要對算法進行浮點到定點的移植。同時,為了使DSP上的代碼獲得

2012-04-18 10:54:27

下面會對 FPGA與ASIC/GPU NN實現進行定性的比較。通常在不同的硬件之間進行同等的比較比較困難,因為最終表現的性能不僅取決于算法實現方法,還取決于所使用的特定設備。此外,GPU和FPGA技術

2023-02-08 15:26:46

設計,這是否與我們的初衷背道而馳呢?上面都是一些基本概念的介紹,下面我就來通俗介紹一下,在DSP里,你是一個軟件設計者,硬件已經完全固化,你所要做的,就是在這個固定的硬件平臺實現其功能的最優化,一般TI

2018-10-10 18:02:03

.。在這種超載情況下,使任務集內各任務滿足各自的時限,嵌入式操作系統必須保證在確定的時間內對事件進行處理,因此必須要有一個良好的任務調度算法。周期任務和非周期任務是實時嵌入式系統中的常見任務類型,系統實時任...

2021-12-21 06:24:18

程序實現的功能一致;(2)有效原則:優化后要比優化前運行速度快或占用存儲空間小,或二者兼有;(3)經濟原則:優化程序要付出較小的代價,取得較好的結果。二、算法優化方法1.系統優化(1)編譯器優化等級配置(-O0/-O1/-O2/-O3)(2)流水線多線程結構(pipeline)2.算法優化(需要

2021-12-21 06:54:14

處理,并行計算的優勢不能發揮出來。 相比較而言,運行深度學習算法實現同樣的性能,GPU所需功耗遠大于FPGA,通常情況下,GPU只能達到FPGA能效比的一半或更低。目前來看,深度學習算法還未完全成熟

2021-09-17 17:08:32

本帖最后由 eehome 于 2013-1-5 10:04 編輯

指紋識別算法的研究及基于FPGA的硬件實現

2012-05-23 20:14:46

果蠅優化算法MATLAB實現發布時間:2018-10-12 23:28,瀏覽次數:1183, 標簽:MATLAB果蠅優化算法--Matlab實現1果蠅優化算法原理介紹果蠅是一種廣泛存在于溫帶

2021-08-17 07:28:11

果蠅優化算法MATLAB實現過程是怎樣的?

2021-11-22 07:48:19

用FPGA硬件實現。 現在我沒有FPGA硬件實現的經驗,不知道如何用FPGA硬件實現小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

用FPGA實現優化的指紋識別預處理算法在選取較優化的指紋識別預處理算法的基礎上,根據算法的結構選取具有并行處理、低功耗、速度快等特點的FPGA作為實現算法的基本器件。由于用FPGA實現復雜算法較傳統

2009-09-19 09:38:11

computation)。源于對鳥群捕食的行為研究。粒子群優化算法的基本思想:是通過群體中個體之間的協作和信息共享來尋找最優解.PSO的優勢:在于簡單容易實現并且沒有許多參數的調節。目前已被廣泛應用于函數優化

2021-07-07 06:04:36

請問在用ARM neon指令優化程序時,在一個for循環下,分別用int32x2_t和int32x4_t類型的指令,后者的速度并沒有按照理論上的速度更快,反而比前者慢是怎么回事呢?必須要對生成的匯編指令進行優化嗎?

2022-10-18 11:23:27

請問在用arm neon指令優化程序時,在一個for循環下,分別用int32x2_t和int32x4_t類型的指令,后者的速度并沒有按照理論上的速度更快,反而比前者慢是怎么回事呢?必須要對生成的匯編指令進行優化嗎?謝謝指教。

2022-09-01 15:47:53

請問一下怎樣才能充分發揮FPGA浮點IP內核的優勢?

2021-04-30 06:49:20

什么是Viterbi算法?目標處理器是什么?如何實現并優化算法編程?

2021-04-27 06:58:19

使得控制系統的實時性低,CPU的利用率不高。由于DSP采用串行的數據處理機制,在對數據量大、速度要求高,高實時性和高可靠性的底層信號進行處理時并無優勢可言,而這恰恰是FPGA的強相。由于FPGA采用數據并發

2022-01-20 09:34:26

的優化給出了對幀內預測哈達馬變換以及運動估計算法的改進# 通過簡化運算復雜效率不高的模塊以及減少模塊間數據相關性等#對硬件進行優化通過對各種測試序列的仿真證明改進是有效的關鍵詞幀內 預測 運動 估計 運動 預測 因子

2008-06-25 11:35:14

。 這本書把多年推廣到諸多公司和工程師團隊的經驗以及由專門的白皮書和應用要點匯集的許多知識進行濃縮,可以用來完善工程師的知識,幫助他們成為高級的fpga設計者。...高級FPGA設計 結構、實現和優化

2012-03-01 14:59:23

經典FPGA算法教材:UMeyer-Baese - Digital Signal Processing with FPGA - Springer

此書是關于各種DSP的FPGA實現的書包括DSP算法原理算法優化以及FPGA的硬件實現包括完整的VHDLVerilog HDL代碼

2009-06-08 18:15:59 655

655 提出用FPGA 來實現指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現, 提高了運算速度。同時具體說明了指紋識別系統的基本原理、系統總體結構、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

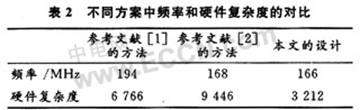

0 分別從整體和局部的角度,提出Camellia 算法幾種基于硬件編程實現的優化方法。在整體角度,以輪循環和模塊復用方式實現緊湊型結構,而以流水線方式實現高速型結構;在局

2010-01-15 15:49:14 13

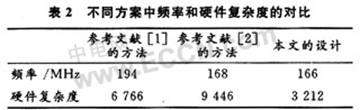

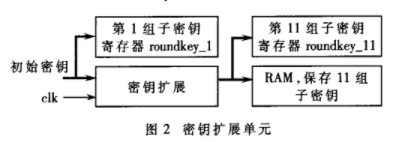

13 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 44

44 介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

25 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

20 AES算法中S-box和列混合單元的優化及FPGA技術實現

由于其較高的保密級別,AES算法被用來替代DES和3-DES,以適應更為嚴苛的數

2010-04-23 09:34:22 2692

2692

提出了二維模糊CMAC網絡的一種基于FPGA的硬件實現方法。首先,分析了模糊CMAC網絡的結構與算法,并以Matlab仿真為依據,得到模糊CMAC網絡的FPGA實現所需的參數;在此基礎上,對模糊CMAC網絡進行硬件模塊劃分,基于VHDL實現了各硬件模塊的功能描述,并對模塊

2011-03-15 17:19:56 29

29 介紹了一種適于TUD 系統的SHA256算法和HMAC算法! 給出了在FPGA上實現SHA256算法和HMAC 算法的一種電路設計方案!并對算法的硬件實現部分進行了優化設計! 給出了FPGA的實現結果

2011-05-16 16:50:45 141

141 LMS(最小均方)算法因其收斂速度快及算法實現簡單等特點在自適應濾波器、自適應天線陣技術等領域得到了十分廣泛的應用。為了發揮算法的最佳性能,必須采用具有大動態范圍及運算精

2011-09-19 17:24:02 1491

1491

基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 4

4 SVPWM算法優化及其FPGA_CPLD實現

2016-04-13 15:42:35 18

18 利用FPGA實現信號處理算法是一個難度頗高的應用,不僅涉及到對信號處理算法、FPGA芯片和開發工具的學習,還意味著要改變傳統利用軟件在DSP上實現算法的習慣,從面向硬件實現的算法設計、硬件實現、結構優化和算法驗證等多個方面進行深入學習。

2016-12-26 17:26:41 12

12 算法進行深入研究,面向Xilinx K7 410T FPGA 芯片設計SHA-1算法實現結構,完成SHA-1算法編程,進行測試和后續應用。該算法在FPGA 上實現,可以實現3.2G bit/s的吞吐

2017-10-30 16:25:54 4

4 根據AES算法的特點,從3方面對算法硬件實現進行改進:列混合部分使用查找表代替矩陣變換,降低算法實現的運算復雜度,采用流水線結構優化關鍵路徑一密鑰拓展,提升加密速度,利用FPGA定制RAM

2017-11-02 10:59:59 0

0 摘要: 介紹了3DES加密算法的原理并詳盡描述了該算法的FPGA設計實現。采用了狀態機和流水線技術,使得在面積和速度上達到最佳優化;添加了輸入和輸出接口的設計以增強該算法應用的靈活性。各模塊均用硬件

2017-11-06 11:10:09 4

4 本文選擇了一種新穎的圖像縮放算法進行FPGA硬件實現。該算法基于奇偶分解的思想,具有復雜度低、硬件需求小和縮放效果良好等突出優點。首先利用MATLAB對該算法進行了功能驗證,然后用縮放耗時、PSNR

2017-11-17 07:46:01 2121

2121

MQ編碼是一種無損數據壓縮技術,已被JPEG2000標準采用,其高復雜度成為JPEG2000系統實現的速度瓶頸。本文在分析MQ編碼算法軟件流程的基礎上提出了一種優化的基于流水線處理的MQ編碼算法;并利用Xilinx FPGA的可編程特性詳細地將此算法模塊化,最后實現仿真驗證。

2017-11-17 17:09:01 2964

2964 。在進行FFT這類并行運算為主的算法時,采用FPGA的優勢不言而喻。用FPGA實現FFT算法進行諧波檢測成為了一大熱點。

2018-07-16 18:22:00 3391

3391

本文選擇了一種新穎的圖像縮放算法進行FPGA硬件實現。該算法基于奇偶分解的思想,具有復雜度低、硬件需求小和縮放效果良好等突出優點。首先利用MATLAB對該算法進行了功能驗證,然后用縮放耗時、PSNR

2017-12-12 14:07:38 2

2 AES算法作為DES算法的替代者應用非常廣泛,其硬件實現方法已有不少討論,主要是通過提高算法頻率來提高吞吐量。但是在實際運行中,為了保證整個加密系統的穩定性,通常全局時鐘頻率較低,不可能達到算法的仿真頻率,如PCI接口電路時鐘頻率只有33MHz,因此實際數據吞吐量仍然較低。

2019-04-18 08:15:00 3057

3057

在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法,采用Verilog HDI 語言描述

2020-09-14 17:49:56 9

9 主要介紹了坐標旋轉數字計算(CORDIC)算法在US,g,鑒別器中的應用,包括碼跟蹤環、鎖頻環和鎖相環鑒別器,并進行了FPGA實現。在設計中,采用統一cORDIc算法優化方法減少硬件開銷,用非流水

2021-01-22 16:12:00 8

8 由于AES算法的硬件實現較為復雜,在此提出一種優化算法中S—box和列混合單元的方法。其中S—box通過組合和有限域映射的方法進行優化,列混合單元使用算式重組的方法進行優化。這些優化設計通過組合邏輯

2021-01-25 14:27:14 19

19 在選取較優化的指紋識別預處理算法的基礎上,根據算法的結構選取具有并行處理、低功耗、速度快等特點的FPGA作為實現算法的基本器件。由于用FPGA實現復雜算法較傳統器件從思考角度和實現方向上都有很大區別,所以本次設計從新的方向來完成傳統的指紋處理的設計。實際結果表明FPGA基本達到了設計的最初要求。

2021-02-03 15:53:00 11

11 ,給出了硬件整體構架以及算法邏輯,并針對FPGA速度與面積優化的問題,完成了控制邏輯的流水線設計。最后采用Verilog HDL對設計進行了描述,利用Ncverilog對模塊進行了仿真,給出了基于Synplify Pro 8.2.1的實現方案。結果表明,該設計較好地實

2021-02-05 17:00:02 22

22 功能.文中將軟硬件實現的順序形態圖像處理圖片在處理效果和速度兩個方面作了比較.算法在FPGA芯片上的高速實現特征使數學形態學在圖像實時處理領域的應用成為可能。

2021-04-01 11:21:46 8

8 為了調整圖像數據灰度,介紹了一種圖像灰度級拉伸算法的FPGA實現方法,并針對FPGA的特點對算法的實現方法進行了研究,從而解決了其在導引系統應用中的實時性問題。仿真驗證結果表明:基于FPGA的圖像拉伸算法具有運算速度快,可靠性高,功耗低等特點,非常適合成像系統使用.

2021-04-01 14:14:49 10

10 為了調整圖像數據灰度,介紹了一種圖像灰度級拉伸算法的FPGA實現方法,并針對FPGA的特點對算法的實現方法進行了研究,從而解決了其在導引系統應用中的實時性問題。仿真驗證結果表明:基于FPGA的圖像拉伸算法具有運算速度快,可靠性高,功耗低等特點,非常適合成像系統使用.

2021-04-01 14:14:49 1

1 設計了一種基于FPGA的正交匹配追蹤(Orthogonal Matching Pursuit,OMP)算法的硬件優化結構,對OMP算法進行了改進,大大減

2021-04-08 13:28:52 1917

1917

差,成本昂貴。隨著FPGA發展,其資源豐富,易于組織流水和并行結構,將FFT實時性要求與FPGA器件設計的靈活性相結合,實現并行算法與硬件結構的優化配置,不僅可以提高處理速度,并且具有靈活性高。開發費

2023-05-11 15:31:41 1649

1649

FPGA算法是指在FPGA(現場可編程門陣列)上實現的算法。FPGA是一種可重構的硬件設備,可以通過配置和編程實現各種不同的功能和算法,而不需要進行硬件電路的修改。

FPGA算法可以包括

2023-08-16 14:31:23 1604

1604

引言 LMS(最小均方)算法因其收斂速度快及算法實現簡單等特點在自適應濾波器、自適應天線陣技術等領域得到了十分廣泛的應用。為了發揮算法的最佳性能,必須采用具有大動態范圍及運算精度的浮點運算,而浮點

2023-12-21 16:40:01 228

228 FPGA算法的優點在于它們可以提供高度的定制化和靈活性,使得算法可以根據實際需求進行優化和調整。此外,FPGA還可以實現硬件加速,提供比傳統處理器更高的計算性能和吞吐量。因此,FPGA算法在許多領域中被廣泛應用,包括嵌入式系統、高性能計算和實時信號處理等。

2024-01-15 16:03:24 434

434

電子發燒友App

電子發燒友App

評論