信息安全是計算機科學技術的熱點研究領域,數據加密則是信息安全的重要手段。隨著可編程技術的飛速發展及高速集成電路的不斷出現,采用FPGA實現加密算法已受到越來越廣泛的關注和重視。與傳統的軟件加密方法相比,硬件加密的優點是:(1)安全性好,不易被攻擊;(2)計算速度快,效率高;(3)成本低,性能可靠。加密系統中體現數據傳輸速度的一個重要性能指標是數據吞吐量,計算公式為:(數據長度M/時鐘個數N)×時鐘頻率F。提高數據吞吐量是改善加密系統性能的關鍵,也是加密算法硬件實現技術的重要內容。

AES算法作為DES算法的替代者應用非常廣泛,其硬件實現方法已有不少討論,主要是通過提高算法頻率來提高吞吐量。但是在實際運行中,為了保證整個加密系統的穩定性,通常全局時鐘頻率較低,不可能達到算法的仿真頻率,如PCI接口電路時鐘頻率只有33MHz,因此實際數據吞吐量仍然較低。本文根據AES算法的結構特點及硬件系統的特點,提出一種快速的AES算法IP核設計方法。該方法采用優化設計輪函數和流水線技術,在較低的系統時鐘頻率下,通過減少分組運算時鐘數目來獲得更高的吞吐量和更快的傳輸速度。

1 AES算法

AES是美國國家標準與技術研究所(NIST)提出的高級加密標準。2000年10月,NIST宣布將比利時人Joan Daemen和Vicent Rijinen提交的Rijndael算法作為高級加密標準(AES)。該算法設計簡單,與公鑰密碼算法不同,沒有復雜的乘法運算,易于實現,靈活性強,輪函數良好的并行特性有利于硬件設計與實現。AES算法是一種迭代型分組密碼,其分組長度和密鑰長度均可變,各自可以獨立指定為128bit、192bit、256bit。本文主要討論分組長度和密鑰長度為128bit的情況。

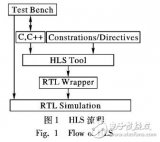

AES算法是將輸入的明文(或密文)分成16個字節,在第一個Add Round Keys變換后進入10輪迭代。前9輪完全相同,依次經過字節代替(Substitute Bytes)、行移位(Shift Rows)、列混合(Mix Columns)、輪密鑰加(Add Round Keys),最后一輪則跳過了Mix Column。解密過程與加密過程類似,但執行順序與描述內容有所不同,因此AES算法的加解密過程需要分別實現。圖1給出了AES算法的加解密過程。

2 AES算法優化設計

2.1 硬件選擇

Cyclone器件是Altera公司推出的成本最低的SRAM工藝FPGA,容量為2 910~20 060個邏輯單元(LE)和多達288kbit的M4K memory block。每個LE都有一個四輸入的LUT查找表、可編程寄存器和具有進位選擇能力的進位鏈,可實現任何四輸入變量的函數,能夠進行大量邏輯運算,非常適合作為加密算法的硬件載體。設計中所使用的開發工具是QuartusII4.2,FPGA芯片選擇Cyclone器件的EP1C12Q240C8,基于Verilog HDL語言實現。

2.2 密鑰擴展單元優化設計

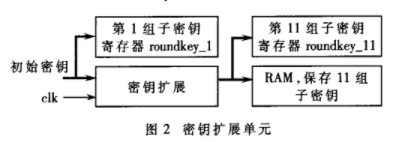

密鑰擴展是將初始密鑰作為種子密鑰,經過字節代換、字節移位、輪常數計算、字異或等過程,計算產生10輪迭代子密鑰。有文獻提出計算密鑰時密鑰擴展和加密過程同步執行,這樣做會節約FPGA的存儲器資源。但筆者認為在算法運行過程中,擴展密鑰進程始終運行會增加FPGA芯片的動態功耗。另外,AES算法解密運算是從最后一輪子密鑰開始,只有擴展出所有子密鑰才能啟動解密運算,因此制約了解密過程的實現。通常情況下初始密鑰不會頻繁改變,加/解密多包數據時可共享密鑰擴展結果,同時由于Cyclone器件存儲器資源豐富,為存放子密鑰提供了足夠的空間。因此本文采用更普遍的做法,將所有子密鑰擴展后保存在RAM中,使用時依次從RAM中讀取。這種方式不受加解密實現過程的限制,靈活性強,非常適合于加密算法的FPGA實現。

從RAM中讀取子密鑰需要時間,為了避免算法第一個Add Round Key過程帶來的延時,可以將第一組子密鑰(初始密鑰)和最后一組子密鑰(解密過程第一組子密鑰)在寫入RAM的同時,分別保存在兩組寄存器中。如圖2所示,加/解密時直接利用寄存器結果進入算法第一輪迭代,保證算法在10個時鐘內完成10輪迭代,從而減少Add Round Key的時間。

保存密鑰雖然多占用了約256個寄存器資源,但這樣做更易于實現算法的流水線操作,對提高整體性能有很大幫助。

2.3 輪函數優化設計

優化輪函數設計,減少輪函數的延時,是提高算法時鐘頻率的關鍵。本文通過對輪函數中Substitute Byte、Shift Row和Mix Column變換進行優化來提高算法的時鐘頻率。

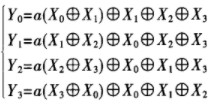

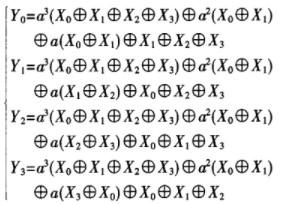

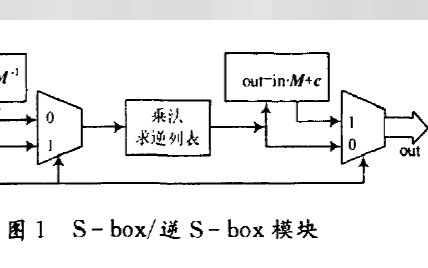

輪函數中Substitute Byte(S-Box)是對一個字節的非線性操作。使用Verilog HDL描述S-Box通常有兩種方法:(1)使用case語句進行行為描述,綜合后占用LE資源;(2)使用FPGA中的存儲器資源。AES算法的S-Box是一個8入8出的查找表,如果用LE實現,則在Cyclone芯片中每個S-Box需要208個LE,AES算法的并行運算需要32個S-Box,共6656個LE,不但占用大量的硬件資源,而且使結構復雜,增加了延時。而用存儲器資源實現S-Box,不需占用其他硬件資源,并且可以減少延時,是個很好的選擇。本文即采用這種方法,并充分利用器件資源:Cyclone器件中每個memory block可以設計為一個256×16bit的ROM,將加/解密過程的S-Box設計在同一個ROM內,加密S-Box內容置于ROM的前8bit,解密S-Box內容置于ROM的后8bit,這樣可以使memory block的數目比分別使用ROM設計時減少一半,大幅提高了資源利用率。Shift Row的硬件實現非常簡單,只是連線操作。為了進一步降低由于連線引起的延時,將Substitute Byte與Shift Row合為一體,使兩部分延時僅取決于S-Box的ROM。Mix Column變換被定義為系數在有限域GF(28)上的四次多項式矩陣乘法,輸入列向量(X0,X1,X2,X3),輸出列向量(Y0,Y1,Y2,Y3),加密過程是在GF(28)上乘以01、02、03,解密過程相對復雜,是在GF(28)上乘以09、0E、0B、0D。為了簡化設計以便于FPGA實現,可將矩陣乘法展開并整理,得到以下結果:

加密Mix Column:

解密Mix Column:

式中a是對一個字節的變換函數,其Verilog HDL描述為:

a={b[6:0],1′b0}^(8′h1b&{8{b}});

經過整理,簡化了Mix Column實現過程,節約了硬件資源。Add Round Key只是簡單的異或,占用資源較少。優化設計后輪函數的最大延時僅8.6ns,為提高整個設計的時鐘頻率提供了保障。

3 AES算法的快速實現

3.1 AES算法的硬件實現方式

AES算法的輪操作特點使得其硬件實現可以有多種方式:(1)串行運算:輪函數用組合邏輯實現,10輪迭代過程直接相連,前一輪結果直接作為下一輪的輸入,1個時鐘周期內完成一個分組運算,吞吐量可以達到最佳狀態。(2)基本迭代:采用反饋模式,所有迭代只用一個輪函數,10個時鐘周期完成一個分組運算。(3)輪內流水線:在每一個輪函數中插入寄存器,將一輪運算分成多個操作段,每個時鐘完成一個操作段,這種方式被很多人討論并使用,其優點是可以提高算法運行的時鐘頻率。

在以上幾種AES算法實現方式中,方式(1)由于10個輪函數同時工作,不但需要大量的寄存器資源和組合邏輯資源的支持,而且還增加了延時,一般的FPGA芯片難以滿足容量的要求,時鐘頻率也非常低,所以這種方法不適合加密算法的硬件實現。方式(2)實現簡單,資源占用較少,但每個分組運算時間比較長,吞吐量仍然相對較低。在方式(3)中,由于加密算法的輪操作特點使得輪內各級流水部件不能同時執行,增加了算法運行的時鐘數目。輪內流水線級數越多,時鐘數目也越多。雖然算法仿真頻率可以達到很高,但由于受硬件加密系統全局時鐘的影響,吞吐量并沒有明顯提高。

在對以上算法的幾種實現方式進行分析后,本文基于流水線技術,提出一種更快速的AES算法的FPGA實現方案。該方案即使在全局時鐘頻率較低的情況下,也能獲得很高的吞吐量。

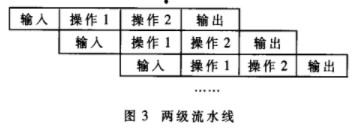

3.2 流水線設計

AES算法結構簡單,只需要邏輯運算和查找表運算。筆者通過優化設計輪函數,使得基本迭代方式下的時鐘頻率遠高于PCI接口的時鐘頻率33MHz。本文在滿足算法時鐘頻率的基礎上,通過降低算法分組數據的處理時間來提高吞吐量。具體做法是:采用兩級輪外流水線,將AES算法的10輪迭代過程分為前后兩個操作段,每個操作段可作為一級流水線,在操作段內部,每輪之間以反饋(FB)方式完成5輪基本迭代,前一個操作段結束后,將結果直接送入第二個操作段,同時去處理下一個分組數據,兩個操作段互不影響,并行執行。考慮到實際應用中數據總線寬度(如PCI總線)通常為32位,這里將AES算法IP核的數據寬度設置為32位,4個時鐘輸入/輸出一個分組數據。為了與每一級流水線5輪迭代過程相匹配,在輸入/輸出分組數據的第5n個時鐘內執行一輪空操作,使得輸入明文數據、輸出密文結果、第一級流水線和第二級流水線四步操作同時執行,從而實現圖3所示的流水線過程。在得到第一個分組結果后,每5個時鐘就會產生一個分組結果,從外部看起來,完成一個分組僅需要5個時鐘。

3.3 實驗結果與性能分析

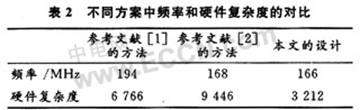

將設計在QuartusⅡ4.2軟件中綜合,仿真最高頻率為78.38MHz,完全可以滿足較低全局時鐘頻率的要求。整個系統設計采用33MHz時鐘,實驗測試結果表明,吞吐量已達到810Mbps。如果提高全局時鐘頻率,則吞吐量會超過1Gbps。

根據AES算法的特點及硬件加密系統的特點,給出了AES算法IP核的快速硬件設計方案。采用流水線技術和優化設計,在較低頻率下,可以獲得很高數據吞吐量,使加密算法的FPGA實現過程不再是傳輸速度的瓶頸。整個設計具有很強的實用性,運行穩定,且效果良好。對于AES算法分組長度和密鑰長度為192bit和256bit的情況,由于分組長度不同,執行輪數有所增加。要實現流水線操作并在資源使用和吞吐量方面達到較好的效果,還需要進一步優化設計,這也是今后研究的方向。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604371 -

寄存器

+關注

關注

31文章

5357瀏覽量

120692 -

計算機

+關注

關注

19文章

7520瀏覽量

88233

發布評論請先 登錄

相關推薦

如何優化AES算法中S-box和列混合單元?

AES中SubBytes算法在FPGA的實現

AES中的字節替換的FPGA實現

AES加密算法說明

基于AES算法研究與設計

AES算法中S—box和列混合單元的優化及FPGA實現的論文說明

使用FPGA實現AES算法的優化設計

使用FPGA實現AES算法的優化設計

評論