修改設計路徑

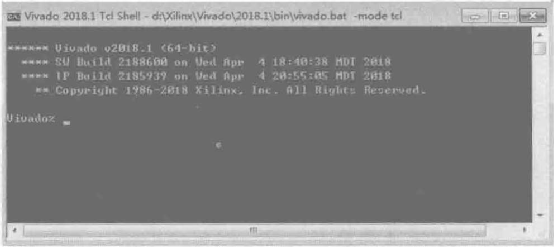

將啟動Vivado ?Tcl環境,并修改路徑,將路徑指向設計文件所在的目錄。下面給出修改路徑的步驟。 ? 第一步:在Windows操作系統的主界面下,執行菜單命令【開始】—【所有程序】—【Xilinx Design Tools】—【Vivado2018.X】—【Vivado2018.X Tcl Shell】,彈出“Vivado 2018.x Tcl Shell”界面,如圖4.1所示,在一系列提示信息后,出現提示符“Vivado%”。

第二步:如圖4.2所示,修改路徑,指向當前提供設計源文件的目錄。在“Vivado%”提示符后面輸入命令“cd e:/vivado_example/gate_verilog_no_project”。

設置設計的輸出路徑

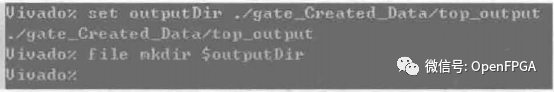

將設置設計的輸出路徑,設置設計輸出路徑的步驟如下所示。 第一步:如圖4.3所示,在“Vivado%”提示符后輸入命令“set outputDir ./gate_Created_Data/top_output”。

第二步:在“Vivado%”提示符后輸入命令“file mkdir $outputDir”。 ?

讀取設計文件

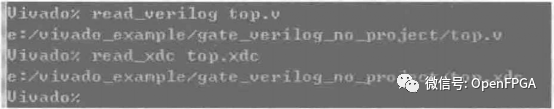

將讀取設計的源文件和約束文件,讀取設計源文件和約束文件的步驟如下所示。 第一步:如圖4.4所示,在“Vivado%”提示符后輸入命令“read_verilogtop.v”。 第二步:在“Vivado%”提示符后輸入命令“read_xdctop.xdc”。

運行設計綜合

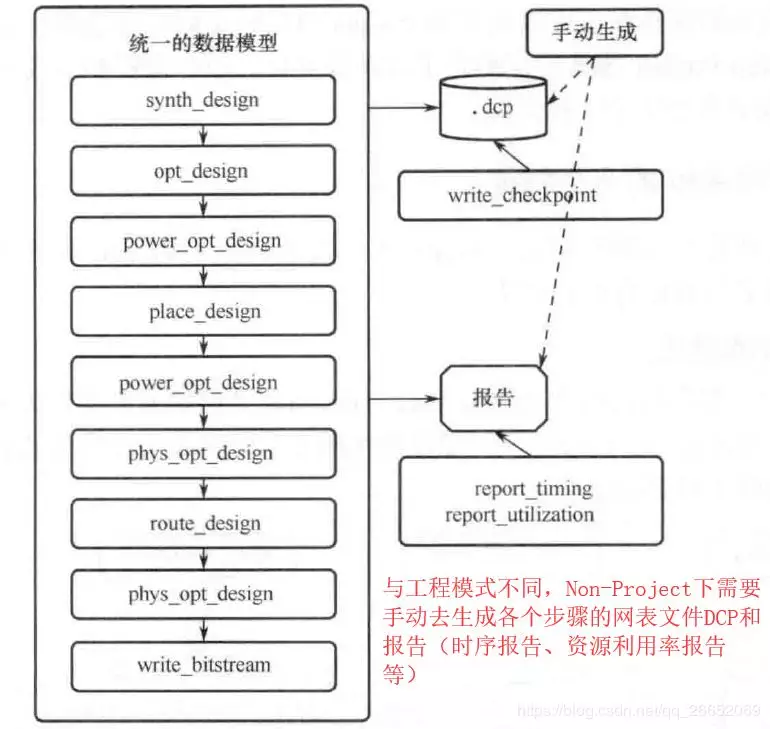

? 將對設計進行綜合,并執行分析。非工程模式下運行設計綜合并執行分析的步驟如下所示。公眾號:OpenFPGA 第一步:在“Vivado%”提示符后輸入“synth_design -top top -part xc7a75tfgg484-1”命令,對設計進行綜合 synth_design命令完整的語法格式為: ?

?

synth_design[-name][-part][-constrset][-top][-include_dirs] [-generic][-verilog_define][-flatten_hierarchy] [-gated_clock_conversion][-directive][-rtl][-bufg][-no_lc] [-fanout_limit][-mode][-fsm_extraction] [-keep_equivalent_registers][-resource_sharing] [-control_set_opt_threshold][-quiet][-verbose]更詳細的參數說明,請參考Xilinx提供的文檔。 第二步:當綜合完成后,在“Vivado%”提示符后輸入“write_checkpoint -force $outputDir/post_synth”命令,寫入檢查點。 第三步:在“Vivado%”提示符后面輸入“report_timing_summary -file $outputDir/post_synth_timing_summary.rpt”命令,用于生成時序報告。 第四步:在“Vivado%”提示符后面輸入“report_power -file $outputDir/post_synth_power.rpt”命令,用于生成功耗報告。 第五步:在“Vivado%”提示符后面輸入“start_gui”命令,啟動Vivado集成開發環境。 第六步:在圖上一步下方的“Tcl Console”窗口中輸入“stop_gui”命令,退出Vivado集成幵發環境。 ?

運行設計布局

對設計運行布局、邏輯優化、寫設計布局檢查點和生成時序總結報告。對設計進行布局和邏輯優化,以及進行分析的步驟如下所示。 第一步:在“Vivado%”提示符后輸入“opt_design”命令,對設計進行優化。

?

opt_design命令完整的語法格式為: opt_design [-retarget] [-propconst] [-sweep] [-bram_power_opt] [-remap] [-resynth_area] [-directive] [-quiet] [-verbose]更詳細的參數說明,詳見Xilinx提供的實現手冊。 第二步:在“Vivado%”提示符后輸入“power_opt_design”命令,對功耗進行優化。 ?

power_opt__design命令完整的語法格式為: power_optdesign [-quiet] [-verbose]? 更詳細的參數說明,詳見Xilinx提供的實現手冊。 第三步:在“Vivado%”提示符后輸入“place_design”命令,對設計進行布局。 ?

place_design命令完整的語法格式為: place_design [-directive] [-no_timing_driven] [-quiet] [-verbose]更詳細的參數說明,詳見Xilinx提供的實現手冊。 第四步:在“Vivado%”提示符后輸入“phys_opt_design”命令,對設計進行邏輯優化。 更詳細的參數說明,詳見Xilinx提供的實現手冊。 ?

phys_opt_design命令完整的語法格式為: phys_opt_design [-fanout_opt] [-placementopt] [-rewire] [-critical_cell_opt] [-dsp_register_opt][-bram_register_opt][-hold_fix][- retime] [-force_replication_on_nets] [-directive] [-quiet] [-verbose]第五步:在“Vivado%”提示符后輸入“write_checkpoin t-force $outputDir/post_place”命令,寫設計布局檢查點。 第六步:在“Vivado%”提示符后輸入“report_timing_summary -file $outputDir/post_place_timing_summary.rpt”命令,生成時序總結報告。 第七步:在“Vivado%”提示符后輸入“start_gui”命令,啟動Vivado集成開發環境。 第八步:在上一步下方的“Tcl Console”窗口中輸入“stop_gui”命令,退出Vivado集成開發環境。 ? ?

運行設計布線

將對設計進行布線、寫檢查點、生成時序總結報告、生產時序報告、生產時鐘利用率報告和生成功耗報告,寫verilog文件和xdc文件。運行設計布線及分析結果的步驟如下所示。公眾號:OpenFPGA 第一步:在“Vivado%”提示符后輸入“route_design”命令,對設計進行布線。 ?

?

route_design命令完整的語法格式為: route_design [-unroute] [-re_entrant] [-nets] [-physicalnets][-pin][-directive][-no_timing_driven][-preserve][-delay] [-free_resource_mode] -max_delay-min_delay[-quiet] [-verbose]更詳細的參數說明,詳見Xilinx提供的實現手冊。 第二步:在“Vivado%”提示符后輸入“write_checkpoint -force $outputDir/post_route”命令,寫檢查點。 第三步:在“Vivado%”提示符后輸入“report_timing_summary -file $outputDir/post_route_timing_summary.rpt”命令,生成時序總結報告。公眾號:OpenFPGA 第四步:在“Vivado%”提示符后輸入“report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt”命令,生成時序報告。 第五步:在“Vivado%”提示符后輸入“report_clock_utilization -file $outputDir/clock_util.rpt”命令,生成時鐘利用率報告。 第六步:在“Vivado%”提示符后輸入“report_utilization -file $outputDir/post_route_util.rpt”命令,生成利用率報告。 第七步:在“Vivado%”提示符后輸入“report_power -file $outputDir/post_route_power.rpt”命令,生成功耗報告。 第八步:在“Vivado%”提示符后輸入“report_drc -file $outputDir/post_imp_drc.rpt”命令,生成drc報告。 第九步:在“Vivado%”提示符后輸入“write_verilog -force $outputDir/top_impl_netlist.v”命令,寫verilog文件。 第十步:在“Vivado%”提示符后輸入“write_xdc -no_fixed_only -force $outputDir/top_impl.xdc”命令,寫xdc文件。 第十一步:在“Vivado%”提示符后面輸入“start_gui”命令,啟動Vivado集成開發環境。 第十二步:在上一步下方的“Tcl Console”窗口中輸入“stop_gui”命令,退出Vivado集成開發環境。 ?

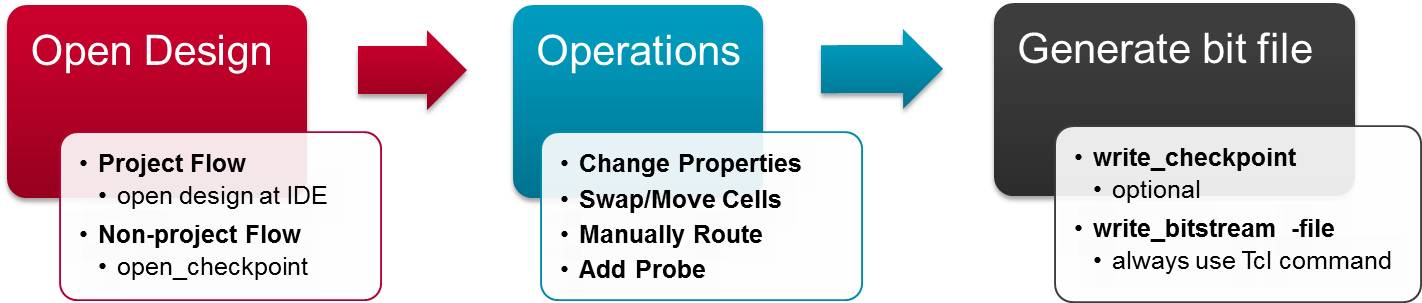

生成比特流文件線

將生成比特流文件。生成比特流文件的步驟如下所示。 在“Vivado%”提示符后輸入“write_bitstream -force $outputDir/top.bit”命令,將會生成比特流文件。 ?

下載比特流文件

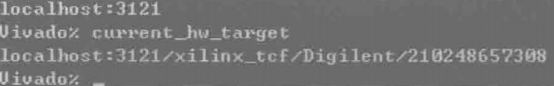

將下載比特流文件到FPGA中。下載比特流文件的步驟如下所示。 ? ? 第一步:在“Vivado%”提示符后面輸入“open_hw”命令,該命令用于打開硬件。公眾號:OpenFPGA 第二步:在“Vivado%”提示符后面輸入“connect_hw_server”命令,該命令用于連接服務器。圖4.8給出了輸入該命令后返回的連接服務器信息,表示連接服務器成功。

第三步:在“Vivado%”提示符后面輸入“current_hw_target”命令,該命令用于顯示當前連接的硬件目標。圖4.9給出了輸入該命令后返回的硬件目標信息。

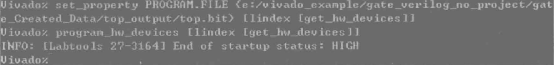

? 第四步:在“Vivado%”提示符后面輸入“open_hw_target”命令,該命令用于打開硬件目標。 第五步:在“Vivado%”提示符后面輸入set_property PROGRAM.FILE {e:/vivado_example/gate_verilog_no_project/gate_Created_Data/top_output/top.bit} [lindex[get_hw_devices]]命令,該命令用于分配編程文件。 第六步:在“Vivado%”提示符后面輸入“program_hw_devices [lindex[get_hw_devices]]”命令,該命令用于對FPGA器件進行編程。如果編程成功,則出現“Done pin status:HIGH”的提示信息,如圖4.11所示

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論