作者:falwat

版權(quán)聲明:本文為博主原創(chuàng)文章,遵循 CC 4.0 BY-SA 版權(quán)協(xié)議,轉(zhuǎn)載請(qǐng)附上原文出處鏈接和本聲明。

本文鏈接:https://blog.csdn.net/falwat/article/details/85918300

本文介紹如何在 vivado 開(kāi)發(fā)教程(一) 創(chuàng)建新工程 的基礎(chǔ)上, 使用IP集成器, 創(chuàng)建塊設(shè)計(jì)。

創(chuàng)建基本的MicroBlaze系統(tǒng)

點(diǎn)擊Vivado 左側(cè)流程導(dǎo)航器中的"IP INTERGRATOR" 下的 "Create Block Design".

點(diǎn)擊"Diagram"中心的"+", 或者使用快捷鍵"Ctrl+I", 或者右鍵選擇菜單"Add IP", 選擇"MicroBlaze" ,雙擊加入到塊設(shè)計(jì)中.

點(diǎn)擊"Diagram"窗口中的"Run Block Automation", 運(yùn)行塊自動(dòng)化. 在彈出的對(duì)話框中,根據(jù)需要修改選項(xiàng), 這里先不做任何修改, 點(diǎn)擊"OK"完成.

繼續(xù)點(diǎn)擊"Diagram"窗口中的"Run Block Automation", 運(yùn)行塊自動(dòng)化, 設(shè)置時(shí)鐘和復(fù)位信號(hào).

在"Diagram"窗口中,右鍵選擇菜單"Regenerate Laout", 重新生成布局, 如下圖所示:

添加外設(shè)

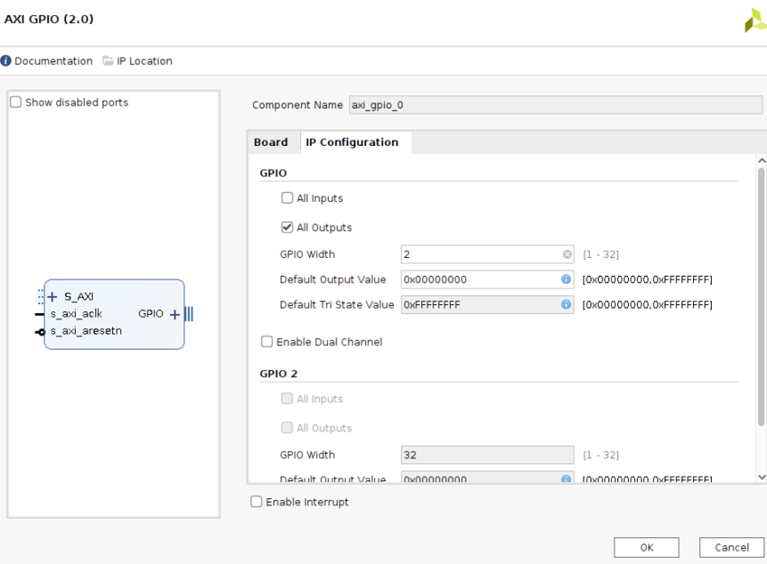

在"Diagram" 窗口中添加"AXI GPIO" IP核, 點(diǎn)擊"Diagram"窗口頂部的"Run Connection Automation", 運(yùn)行連接自動(dòng)化. 按下圖進(jìn)行配置, 配置完成后, 點(diǎn)擊"OK".

在"Diagram"窗口中,右鍵選擇菜單"Regenerate Laout", 重新生成布局, 如下圖所示:

按照上面的步驟,繼續(xù)添加串口IP("AXI Uartlite").

在"Diagram"窗口中,右鍵選擇菜單"Validate Design" 或使用快捷鍵"F6", 驗(yàn)證設(shè)計(jì). 驗(yàn)證通過(guò)后, 關(guān)閉"Block Design" 窗口.

生成輸出產(chǎn)品(Generate Output Products)

切回工程管理("PROJECT MANAGER" )視圖, 在 "system(system.bd)"上右鍵選擇菜單"Generate Output Products", 生成輸出產(chǎn)品.

在彈出的對(duì)話框中,設(shè)置并行運(yùn)行數(shù)量(Number of jobs), 點(diǎn)擊"Generate" 按鈕, 等待生成完成.生成過(guò)程中, 內(nèi)存占用和CPU占用會(huì)急劇飆升.

創(chuàng)建HDL包裝(HDL Wrapper)

在 "system(system.bd)"上右鍵選擇菜單"Create HDL Wrapper". 在彈出的對(duì)話框中,點(diǎn)擊"OK"即可, 生成的"system_wrapper"會(huì)自動(dòng)被設(shè)置為頂層.

審核編輯:何安

-

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66578 -

IP集成器

+關(guān)注

關(guān)注

0文章

4瀏覽量

5802

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何在TMS320C6727 DSP上創(chuàng)建基于延遲的音頻效果

Multi-Scaler IP的Linux示例以及Debug(上)

如何在SQL中創(chuàng)建觸發(fā)器

Banana Pi BPI-M4 Berry創(chuàng)建熱點(diǎn)和設(shè)置靜態(tài)IP

如何在espconn_gethostbyname上創(chuàng)建阻塞線程?

基于RL78/G16 FPB的觸摸樣例工程創(chuàng)建演示流程

stm32f072如何在keil里面創(chuàng)建寄存器函數(shù)的工程而非庫(kù)函數(shù)?

使用STM32CUBEMX創(chuàng)建一個(gè)基于RTOS的工程,互斥量創(chuàng)建不成功的原因?

如何利用Tcl腳本在Manage IP方式下實(shí)現(xiàn)對(duì)IP的高效管理

鴻蒙OpenHarmony【創(chuàng)建工程并獲取源碼】

如何在vivado創(chuàng)建新工程上使用IP集成器創(chuàng)建塊設(shè)計(jì)

如何在vivado創(chuàng)建新工程上使用IP集成器創(chuàng)建塊設(shè)計(jì)

評(píng)論