?投資摘要:

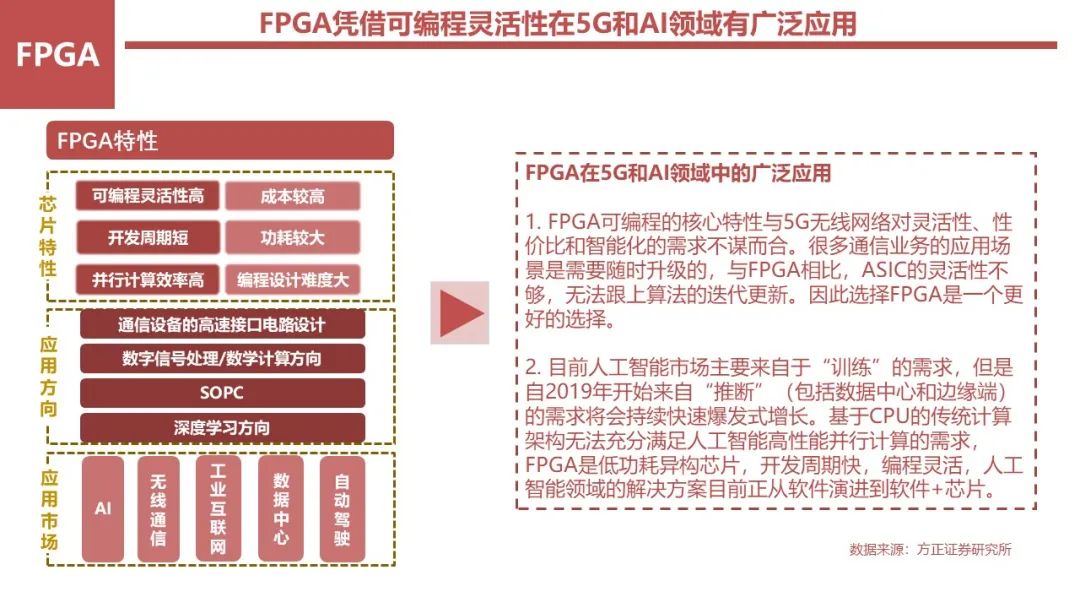

FPGA是一個高度集中的市場,龍頭賽靈思占據過半份額,前4名玩家合計份額90%+。憑借高進入壁壘,清晰且確定的競爭格局,美股FPGA廠商的估值在同類數字芯片公司中均位居前列。此外,龍頭賽靈思在快速增長的市場,維持了近20年50%+的市場份額,以及較高的ROIC水平,足以說明其極強的競爭優勢。 我們在系列報告一《FPGA給用戶提供了什么價值?》中,闡述了FPGA的價值在于高靈活的特性和高并行的架構,我們亦提到了FPGA競爭的關鍵點在于:制程領先、產品定義、架構創新以及EDA工具的易用性。

在本篇系列報告四中,我們將闡述FPGA清晰的競爭格局背后的原因,通過對FPGA全球三大公司Xilinx、Altera和Lattice的發展歷史進行了詳盡的復盤,系統地回答這些問題:FPGA商業模式的本質是什么?FPGA廠商自身的價值在哪里?為什么龍頭能有這么強的護城河? 我們認為,FPGA的商業模式的本質是,用高標準化的芯片覆蓋長尾市場以產生經濟性,龍頭之所以能有強的壟斷性份額,是因為其在一種客戶鎖定下的規模經濟下運作,使得龍頭可以在多輪迭代中不斷積累自身優勢,侵蝕其他玩家的份額,在這一過程中,落后的廠商不斷被淘汰,而行業的進入壁壘在不斷地提高。賽靈思成為龍頭的原因在于:1)制程領導者;2)對客戶的需求把握最好,優秀的競爭策略制定和執行能力;3)生態的培養效果最好。

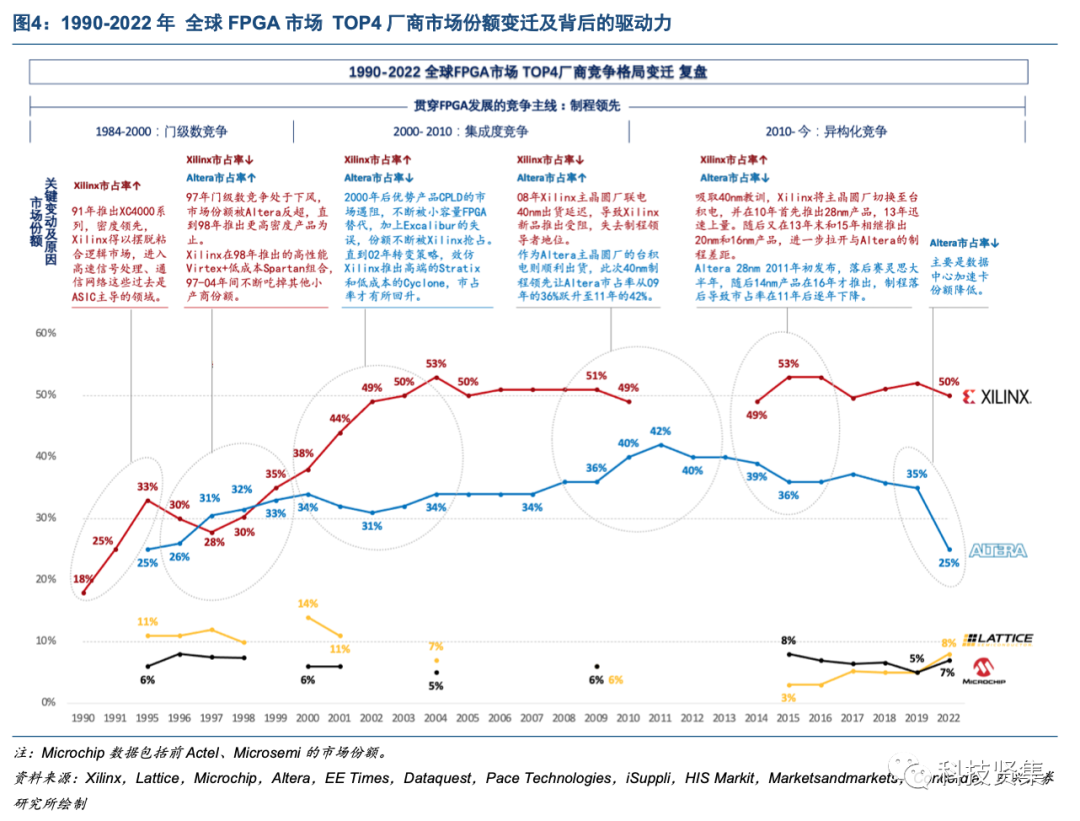

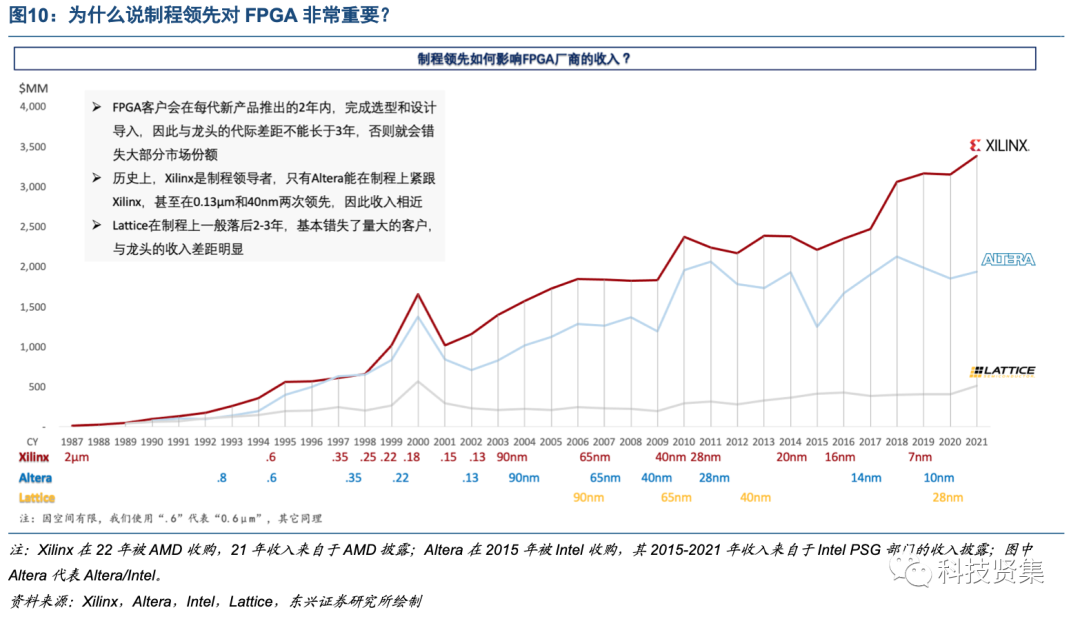

? 復盤1990-2022年FPGA競爭格局演變,我們發現了什么?制程競爭是貫穿FPGA整個發展歷史的競爭主線,制程領先是FPGA市場份額最直接的決定因素。除此之外,在FPGA發展的不同階段,有著不同的階段競爭主線,實質是FPGA不同階段的性能突破點:門級數競爭是FPGA廠商第一階段的競爭主線(1984-2000),FPGA不斷提升自身容量以獲得替代ASIC的市場,門級數領先者往往獲得大部分市場份額。集成度競爭是FPGA廠商第二階段的競爭主線 (2000-2010),將板上分立的DSP等器件納入到FPGA,背后是減少電路面積、降低功耗和系統成本的需求,先推出高集成度FPGA的廠商獲得了更多的替代DSP等競爭產品的份額。異構化競爭是FPGA目前的競爭主線 (2010-今),FPGA廠商競相推出SoC FPGA,通過將板上的CPU等處理器嵌入到FPGA中,使得SoC既具備CPU的靈活性,又具備FPGA的高并行計算能力,進一步提升系統性能、減少板上面積和功耗,不斷并獲得來自嵌入式處理的市場。

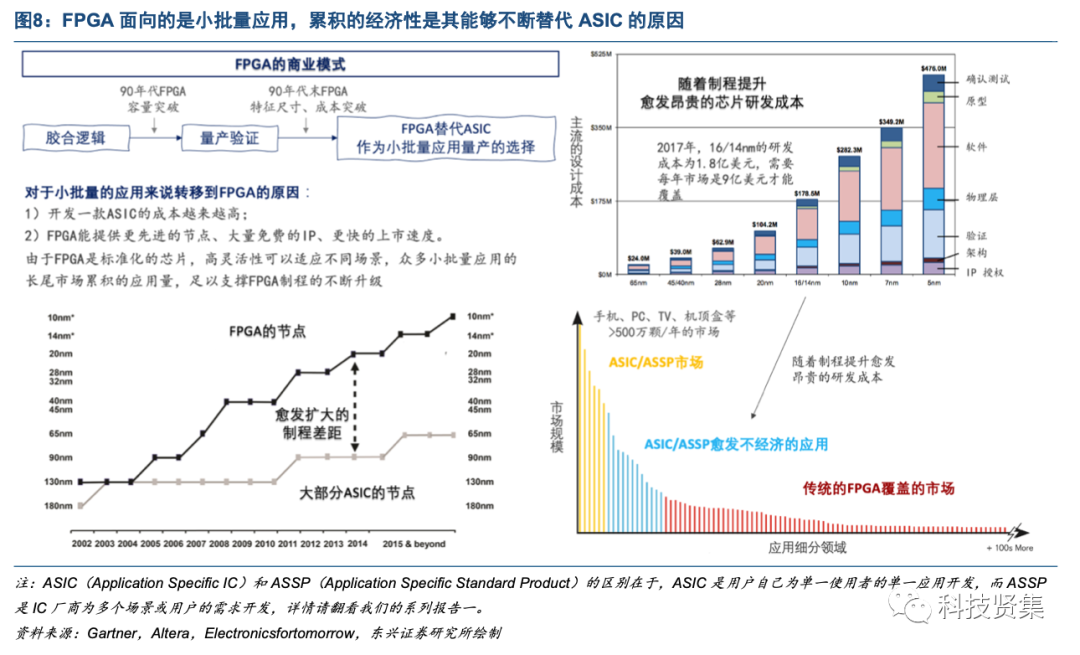

? FPGA商業模式的本質?用高標準化的芯片覆蓋長尾市場以產生經濟性,這些小批量應用累積起來的出貨量足以支撐FPGA的制程不斷升級。FPGA是高度標準化的芯片,通過改變FPGA中LUT4里面的16位掩碼,就能靈活地對應不同的組合電路,再結合寄存器,可以完成時序電路的功能,從而實現任意電路的“可編程”。隨著芯片制程的提升,研發成本變得愈發昂貴,為小批量的應用開發一顆ASIC/ASSP變得越來越不經濟,越來越多的客戶轉向使用FPGA。 為什么龍頭能有這么強的護城河?因為其在一種客戶鎖定下的規模經濟下運作,使得龍頭可以在多輪迭代中不斷積累自身優勢,侵蝕其他玩家的份額,在這一過程中,落后的廠商不斷被淘汰,而行業的進入壁壘在不斷地提高。

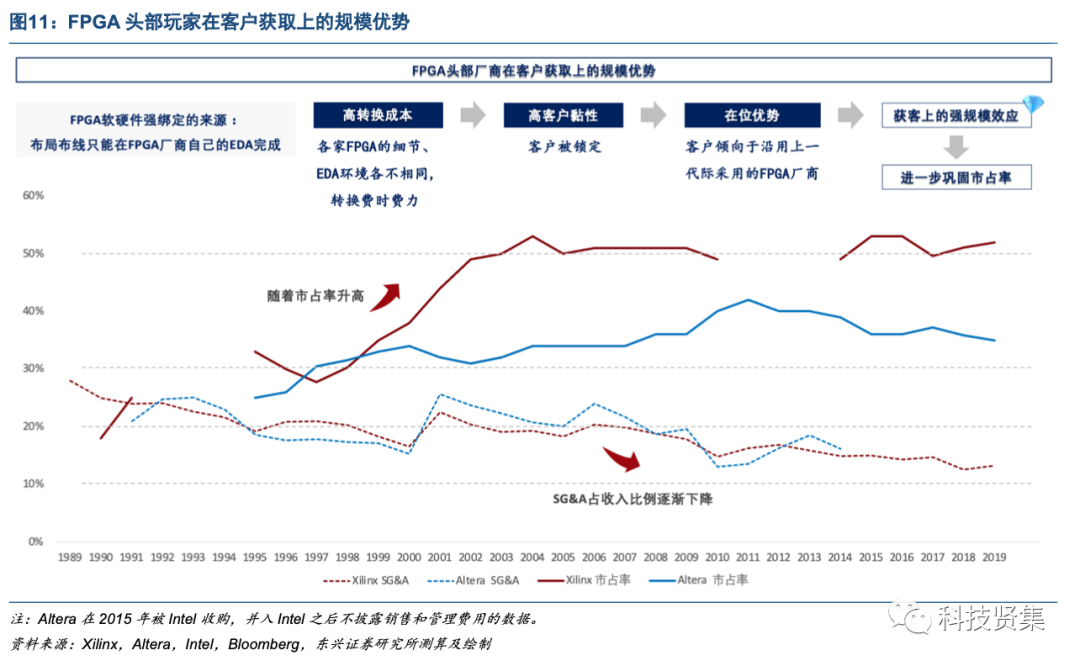

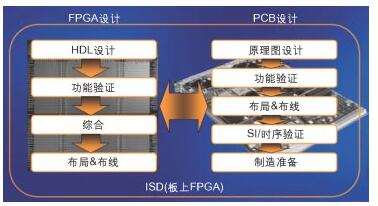

FPGA如何鎖定客戶?由于最關鍵的布局布線只能在FPGA廠商自己的EDA中進行,使得FPGA的軟硬件形成極強的綁定。如無必要,客戶通常不會更換FPGA廠商,而是根據自身的量產計劃每年重復訂購,展現非常強的客戶粘性。同樣地,為了減少轉換成本,客戶會傾向于沿用上一代FPGA的供應商,跨代際的客戶黏性也非常強。

? 如何理解FPGA的規模經濟?

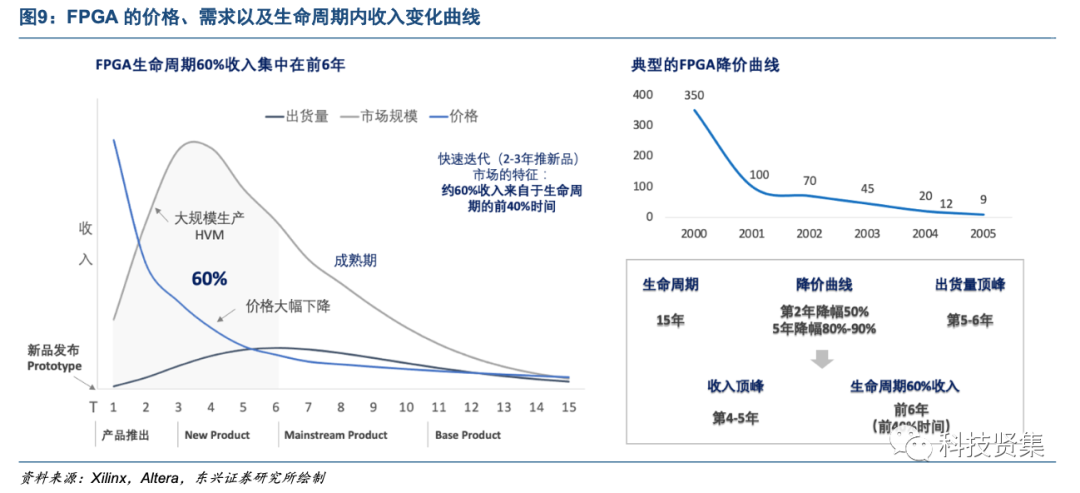

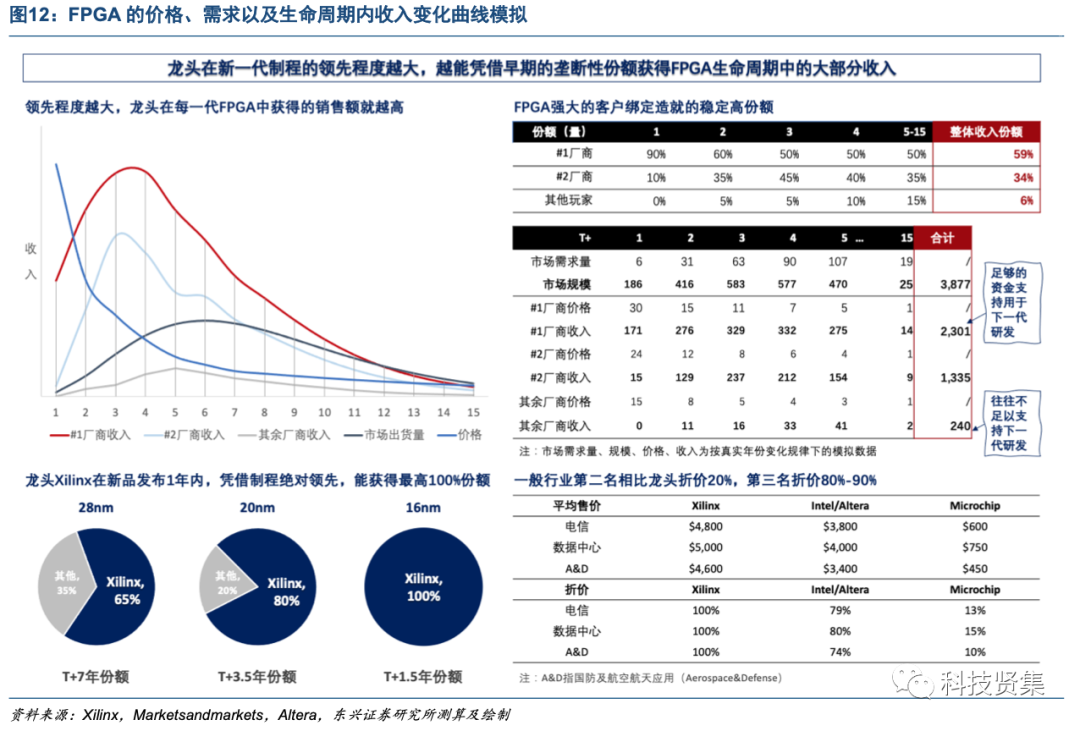

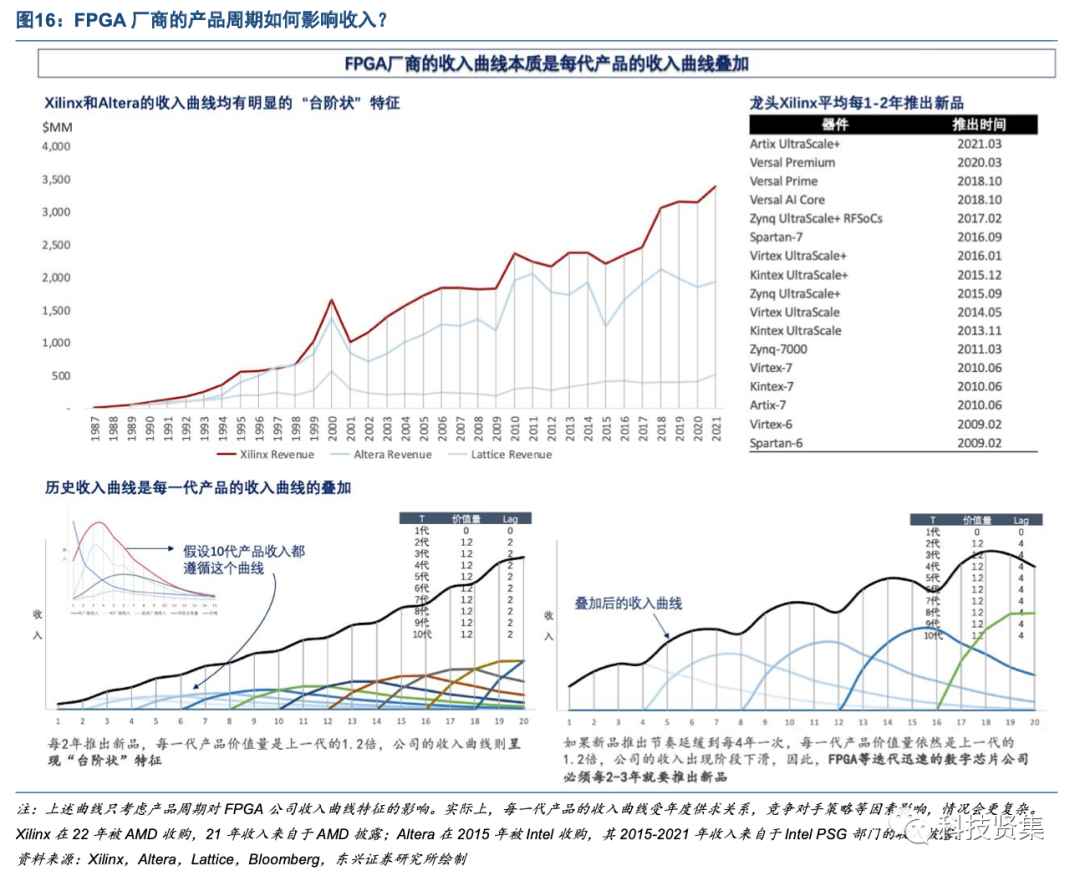

價格上,FPGA有著非常陡峭的降價曲線;需求上,出貨量的頂峰一般在第5-6年達到,這使得FPGA生命周期中約60%的收入在前6年發生,后9年FPGA參與者通常面對的是量價齊跌的市場。由于量大的客戶在前兩年就會被領先的玩家鎖定,如果不能做到前兩年內推出新一代制程的產品,基本就會錯失這一代產品市場收入最多的階段。因此,對于FPGA廠商來說,競爭策略就是盡可能領先對手推出新一代的產品,在前2年完成盡量多的Design-wins,以獲得更多被鎖定的客戶。在獲得強勁的Design-wins之后,FPGA廠商憑借HVM(High-Volume Manufacture)階段的大量訂單迅速降低成本,并進一步開啟激進的降價,以阻止落后的競爭者進入。由于FPGA的EDA和硬件強綁定的特性,客戶轉換成本極高,FPGA的頭部廠商在獲客成本上出現規模經濟,高的在位優勢進一步提升了行業的進入壁壘。在2-3輪制程迭代后,落后的廠商愈發無法獲得足夠的收入以投入到下一代產品的開發,選擇退出,市場上其他玩家的比例會大幅減少,市場份額會向頭部集中,清晰的格局使得FPGA頭部廠商的毛利率均穩定維持在60%+的高水平區間。FPGA龍頭在研發上同樣具有規模經濟。此外,FPGA廠商收入曲線的本質是每一代產品收入曲線的疊加,必須每2-3年推出新品,以避免產品周期造成的收入下滑。

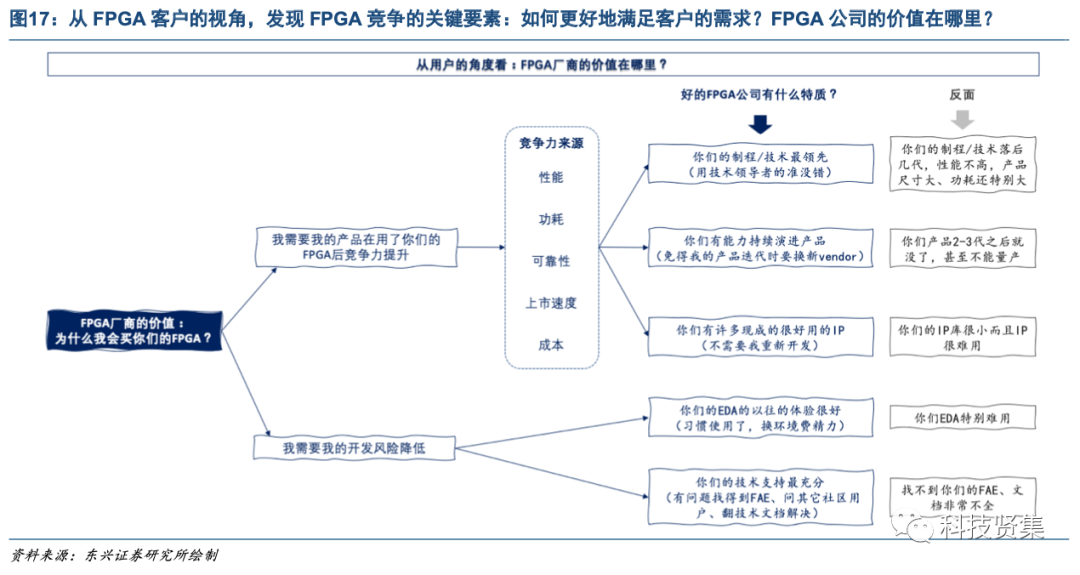

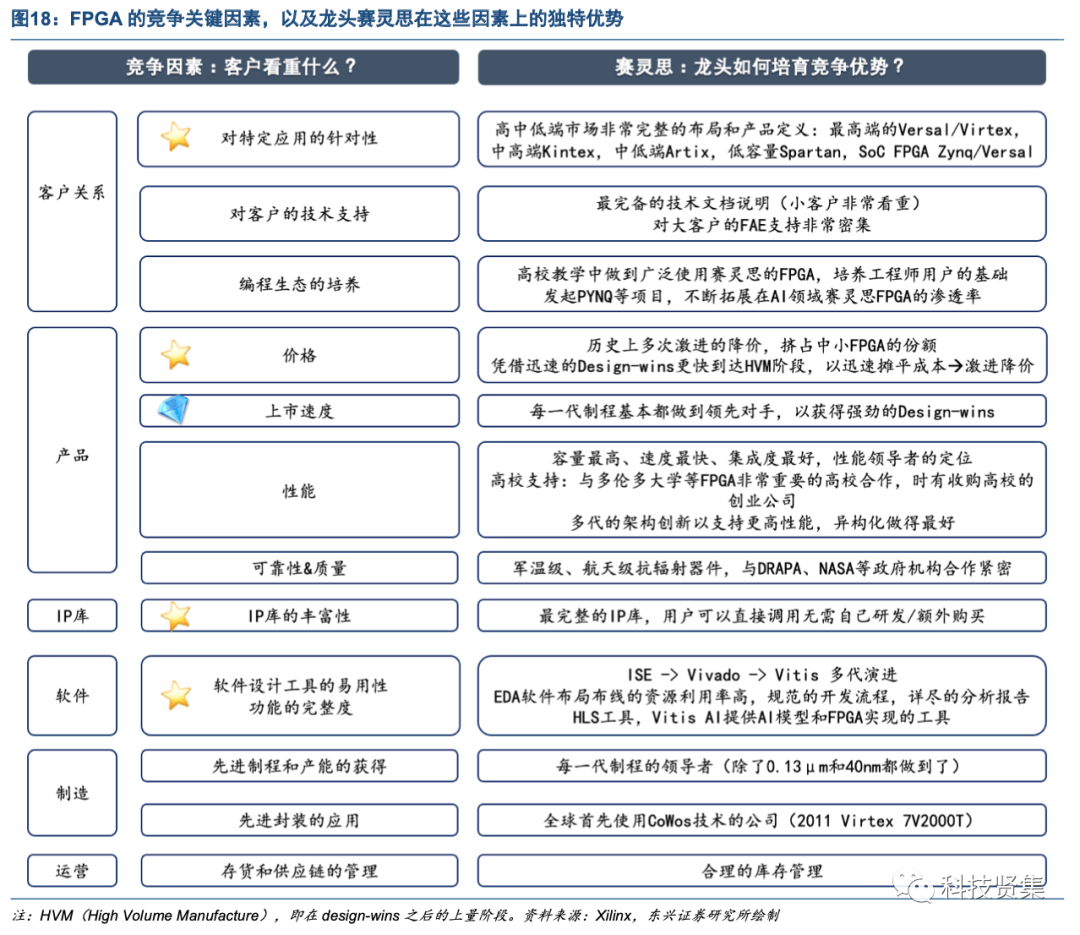

? 我們從FPGA的客戶的視角分析,發現客戶對FPGA主要有兩大訴求:一是為自己的產品獲得競爭力的提升,二是降低開發的風險。從客戶的視角延伸到FPGA競爭的關鍵因素,我們總結為以下六點:客戶關系、產品、IP庫、軟件、制造和運營能力。 我們認為,賽靈思成為龍頭的原因在于:1)制程領導者。 2)對客戶的需求把握最好,優秀的競爭策略制定和執行能力。 3)生態的培養效果最好。

風險提示:下游需求不及預期,中美貿易摩擦加劇。

?

?

?

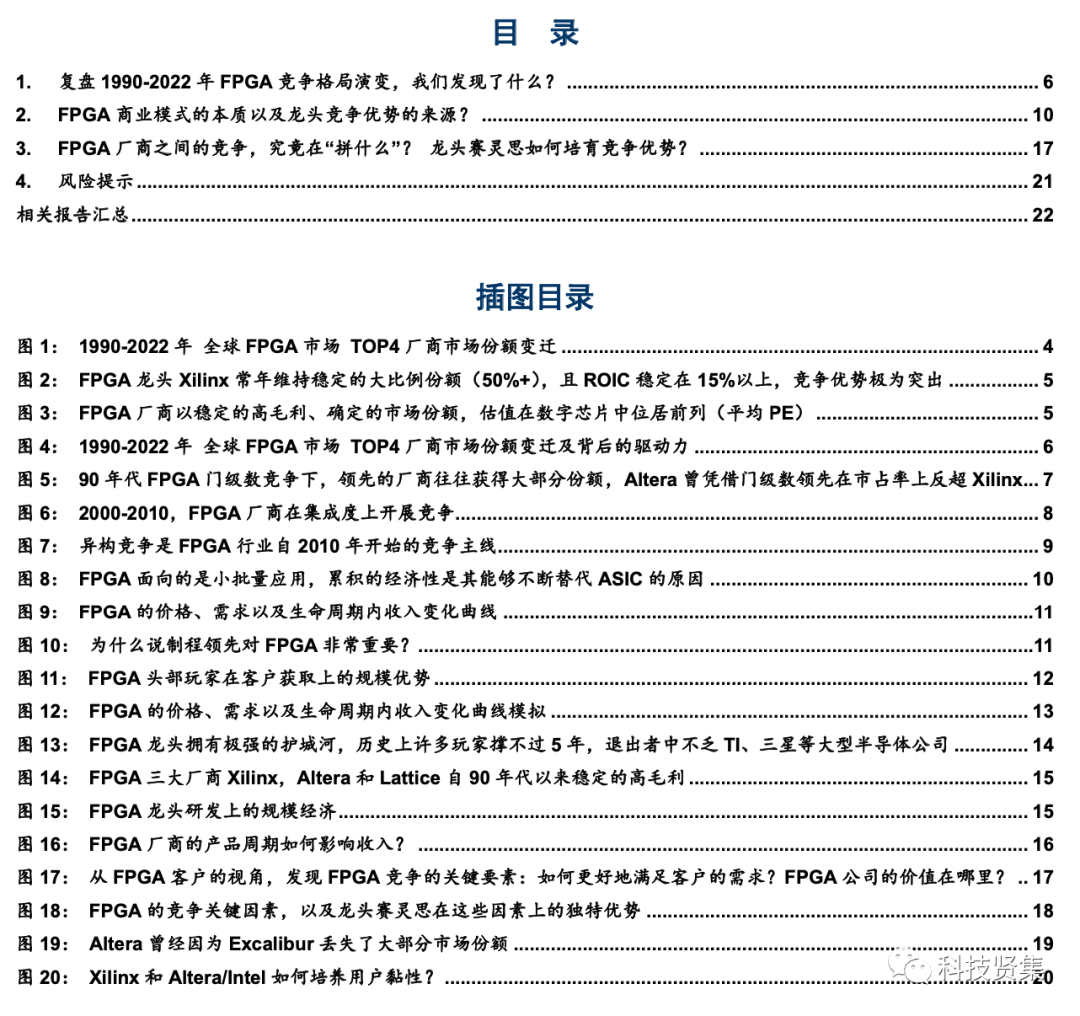

我們在系列報告一《FPGA給用戶提供了什么價值?》闡述了FPGA的價值在于高靈活性及高并行超低時延的計算能力,我們亦提到了FPGA競爭的關鍵點在于:制程領先、產品定義、架構創新以及EDA工具的易用性。在本篇系列報告四中,我們將系統地回答這些問題:FPGA廠商自身的價值在哪里?FPGA廠商的競爭究竟在拼什么?龍頭賽靈思是如何培育競爭優勢的? ? FPGA是一個高度集中的市場,龍頭賽靈思占據過半份額,前4名玩家合計份額90%+。根據Marketsandmarkets數據及我們估算,2022年,FPGA龍頭賽靈思全球市場占有率為50%,與第二名英特爾(收購Altera)的25%拉開了明顯差距,而作為行業第三、第四名的Lattice和Microchip(收購Microsemi)市場份額接近,均不超過10%。行業呈現高度集中態勢,CR4超過90%,且均為美國公司。其中,龍頭賽靈思在2003年市占率超過50%,在隨后20年間,基本保持在50%以上。 ?

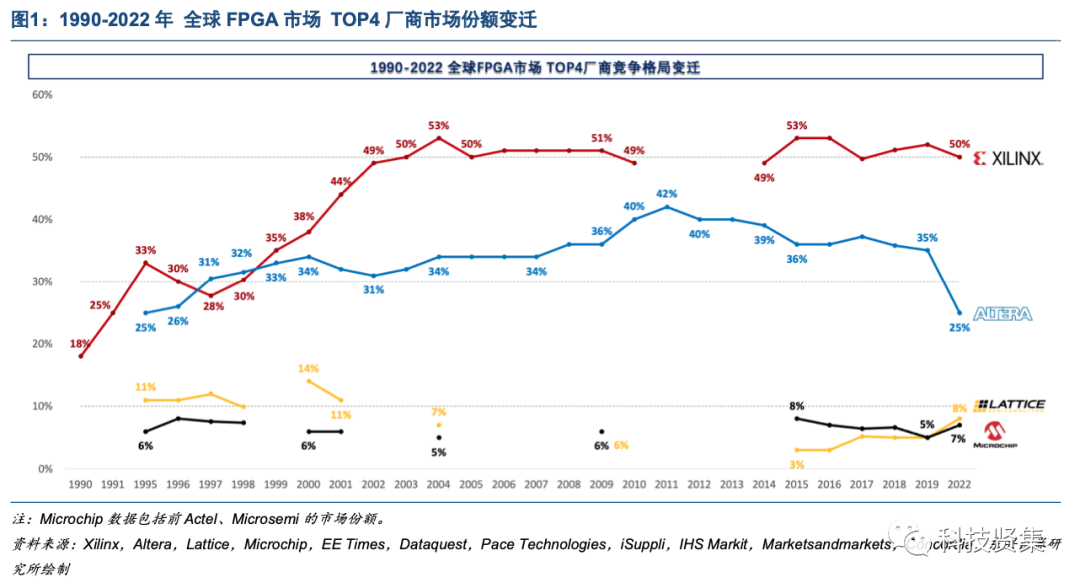

龍頭賽靈思維持了近20年的50%+的市場份額,以及較高的ROIC水平,足以說明其極強的競爭優勢。賽靈思自1984年發明FPGA以來,市場份額從1990年的18%一路爬升到2003年的50%,并在隨后20年間基本維持在50%上下,而在1990-2019近30年間,FPGA市場復合增長率為14%,一直保持著較高速度的增長。賽靈思在03年后的ROIC一直維持在15%上下的較高水平,并在2018-2019年爬升至20%+。在一個快速成長的行業中,龍頭能在15%+的ROIC水平維持近20年的50%的市場份額,足以說明FPGA龍頭有著非常強的競爭優勢。 ?

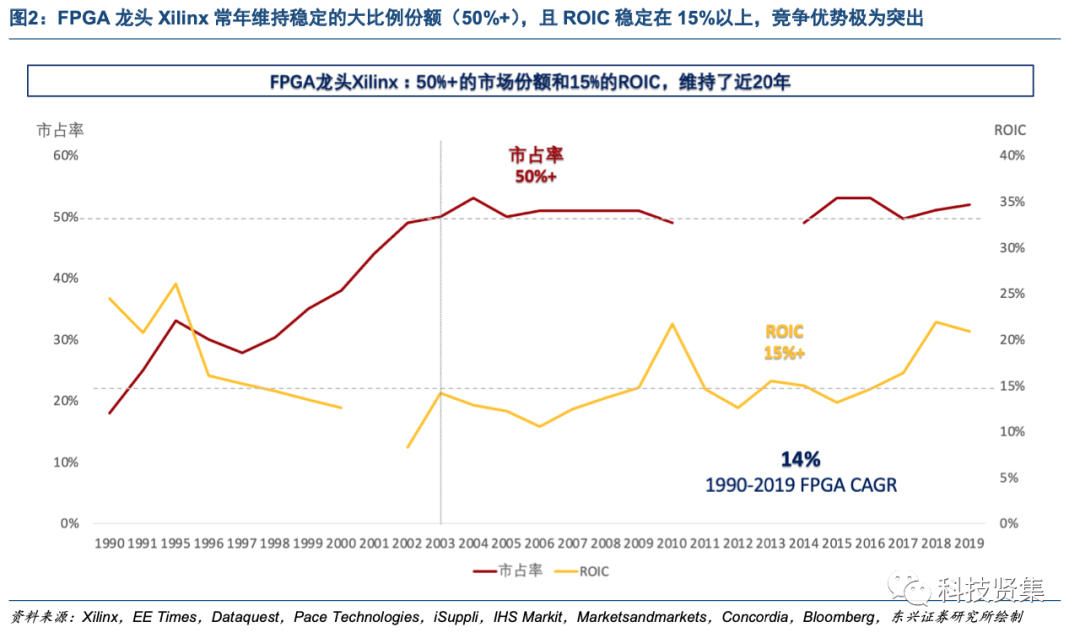

美股FPGA公司高估值的原因?高進入壁壘,清晰且確定的競爭格局。FPGA雖然是一個不大不小的市場(2022全球83億美元),但憑借高進入壁壘,以及確定且清晰的競爭格局,使得美股FPGA廠商的估值在同類數字芯片公司中均位居前列。 ?

01?

復盤1990-2022年FPGA的

競爭格局演變,我們發現了什么?

制程競爭是貫穿FPGA發展歷史的競爭主線,制程領先是FPGA市場份額最直接的決定因素。FPGA的通用性使其走線和面積比起ASIC來說不是最優。因此,FPGA必須在制程上做到領先ASIC或者ASSP數代,以帶來更有競爭力的性能表現,這使得FPGA對制程的追逐是必然的選擇。此外,FPGA從新品發布到量產階段中間存在客戶導入環節,在這期間客戶評估不同廠商新推出的FPGA,最后確定一家在后續量產的產品中使用,并在上面完成自己的電路設計,即一個Design-win,這一過程通常需要9-12個月。由于開發環境、產品架構等各不相同,一旦確定了之后,用戶轉移到另一家FPGA是非常困難和費時的。這種高綁定的特點,造就了FPGA非常強的壁壘,使得最先推出的玩家往往能贏得大部分市場份額。一般來說,在最新制程的design-wins能預測2-3年后在FPGA市場的份額,而且能在下一輪制程競爭中享有一定的在位優勢,因為客戶通常不會輕易更換供應商。FPGA龍頭賽靈思歷史上是制程領導者,市場份額從2003年后便維持在50%的水平,除了Altera能跟上賽靈思的節奏,行業其他玩家均落后龍頭2-3個代際。 ?

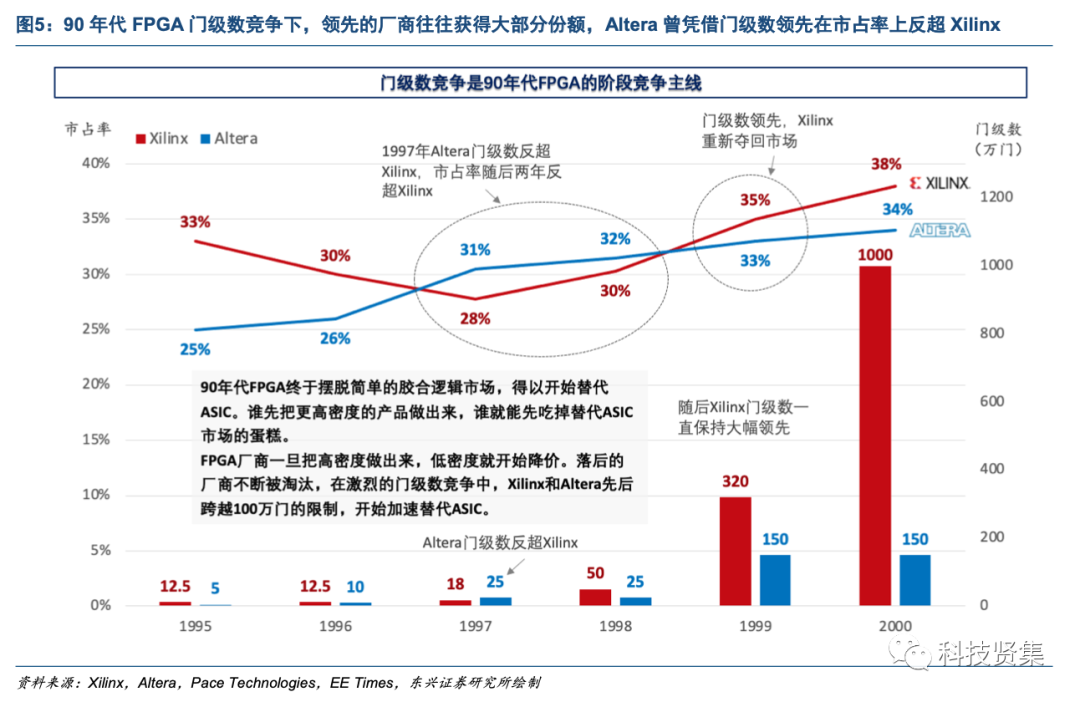

除了貫穿整個歷史的制程競爭外,在FPGA發展的不同階段,有著不同的階段競爭主線,實質是FPGA不同階段的性能和技術突破點: 門級數競爭是FPGA廠商第一階段的競爭主線(1984-2000)。替代ASIC的背后是性能提升的需求,門級數領先者往往獲得大部分市場份額。90年代,復雜的電子系統要求百萬門級的規模,大多使用標準單元和門陣列實現。90年代初,FPGA的容量只有20-50萬門,盡管脫離了膠合邏輯的市場,但仍無法進入更高端的ASIC市場。鑒于此,在整個90年代,FPGA廠商紛紛在門級數上展開競爭,誰先把更高密度的產品做出來,誰就能先吃掉替代ASIC市場的蛋糕。通過LUT輸入數量、簇結構、互聯形式等的架構改善,輔之以摩爾定律的推動,FPGA的密度和速度得以飛速提升。FPGA廠商一旦把更高密度的產品做出來,低密度就開始大幅降價,落后的廠商不斷被淘汰。在激烈的門級數競爭中,Xilinx和Altera先后在1998-1999年跨越100萬門的限制,開始加速替代門陣列、標準單元和ASIC,市占率得到持續的提升。

此階段,FPGA競爭者之間開展激烈的專利戰,以捍衛自身在高密度架構和EDA上競爭優勢。例如,Altera作為CPLD的發明者,1992年通過推出FLEX進入FPGA市場,Xilinx在1993年便開始與Altera開展了長達8年的專利戰,雙方互訴對方產品侵權,并不斷將對方包括CPLD在內的新品加入侵權列表,最后在01年以近似和解結束——Altera向Xilinx?支付了2000萬美元,并互相進行專利交叉互換,承諾5年內不向對方提起專利訴訟。1999年,Altera還與Clear Logic開展訴訟,指控對方利用Altera的EDA軟件為客戶進行pin-to-pin的FPGA到ASIC的轉換,最后使得Clear Logic在2002年退出市場。

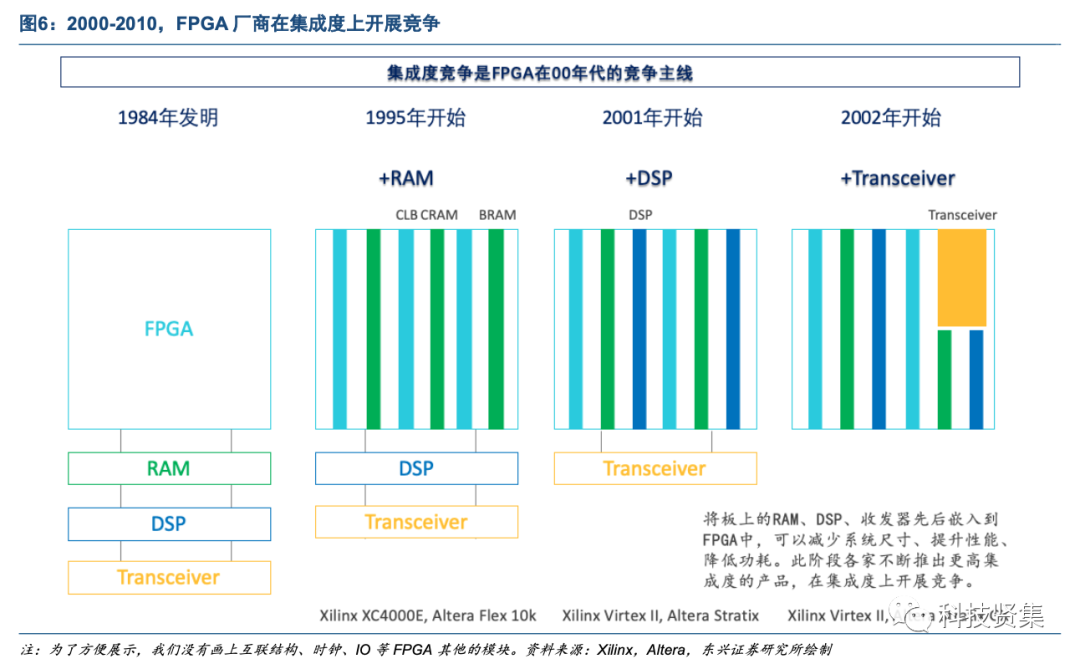

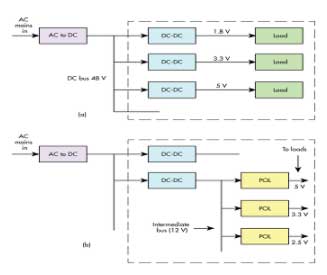

集成度競爭是FPGA廠商第二階段的競爭主線(2000-2010)。將板上分立的DSP等器件納入到FPGA,背后是減少電路面積、降低功耗和系統成本的需求,先推出高集成度FPGA的廠商獲得了更多的替代DSP等競爭產品的份額。90年代中期,FPGA廠商發現用戶在使用FPGA時,會頻繁將LUT作為存儲使用(即“軟”實現),占用了許多邏輯單元,導致FPGA容量出現不夠的情況。因此,RAM是第一個被固化到FPGA中的單元。將這些用戶頻繁使用到的功能固化到FPGA中,可以極大地提升計算效率,用戶也不需要為浪費寶貴的邏輯資源而煩惱,而且可以減少板上的走線、管腳和焊盤,進而減少PCB板的面積和功耗。例如,將DSP嵌入到FPGA中(而不是通過萬能的LUT+寄存器實現),可以節省80%的功耗和分立的DSP在板上占用的面積。因此,在90年代末完成門級數的超越后,FPGA廠商的競爭主線從門級數轉向集成度競爭,先后將原本屬于板上的RAM、DSP、收發器等單元嵌入到FPGA中,以降低客戶的功耗和總系統成本,并進一步蠶食板上其它分立器件的市場。Altera的FLEX 10K是第一個嵌入了RAM?的FPGA,Xilinx在00年通過收購Rocketchip擁有了高速收發器能力,并在02年3月發布的Virtex II Pro中嵌入了收發器。

然而,并不是一個FPGA上集成了越多固化單元就越好,除了最高端的客戶,許多客戶往往只需要特定方向上的固化單元集成。因此,FPGA廠商開始將產品線分化,Xilinx推出了高端的Virtex和低成本的Spartan兩條線,Virtex針對復雜的通信設備市場,Spartan和CPLD Coolrunner針對消費電子市場。其中,Virtex還區分了多個產品系列,比如Virtex 4中,LX是最高端的FPGA,針對大型的高密度通信應用,而SX系列上嵌入了豐富的DSP資源,用于替代分立的DSP器件,FX加入了高速串行連接。Altera也在02年推出了高端的Stratix和低成本的Cyclone,Stratix還分化了一個包含高速收發器的Stratix GX系列。可見,集成度競爭的背后是產品定義的競爭,反映了FPGA廠商和客戶溝通和需求把握能力。

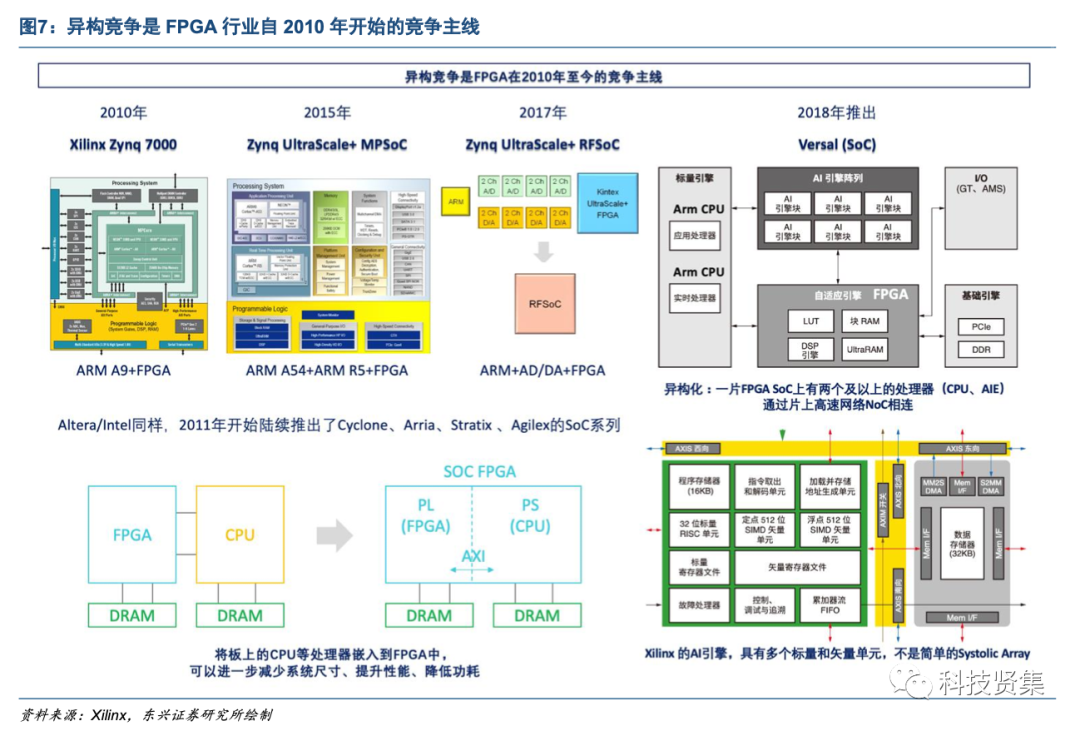

異構化競爭是FPGA廠商目前的競爭主線?(2010-今)。FPGA廠商競相推出SoC FPGA,通過將板上的CPU等處理器嵌入到FPGA中,不斷獲得來自嵌入式處理的市場。因為走線從PCB轉移到片內,處理時延更短,因此整體性能更高,并進一步減少板上的面積、降低功耗,使得SoC既具備CPU的靈活性,又具備FPGA的高并行計算能力。例如,Xilinx的RFSoC嵌入了ARM+4片ADC+4片DAC+1片Kintex UltraScale+ FPGA,相比分立的方案面積減少了50%,功耗降低30%-40%,成本降低40%-60%,時延比JESD204降低80%-90%。 自從2010年Xilinx推出Zynq 7000開始,FPGA進入了異構競爭的時代,進一步搶占原來使用分立的FPGA+CPU方案的市場。在Xilinx的Zynq系列中,PL(FPGA)與PS(ARM CPU)之間通過AXI總線通信。Xilinx在后續推出了針對高清視頻處理的Zynq MPSoC,以及針對無線通信的RFSoC。目前Xilinx的Zynq系列SoC FPGA在工業、多媒體處理、通信、醫療有非常廣泛的采用,最新的系列是在18年開始陸續推出的7nm ACAP Versal家族,在FPGA基礎上嵌入了CPU和Xilinx的AI引擎,單元之間通過高速NoC相連。Altera/Intel同樣,自2011年開始陸續推出了Cyclone、Arria、Stratix和Agilex的SoC FPGA,覆蓋低成本、性價比和高端場景。 ?

?

02?

FPGA商業模式的本質

以及龍頭競爭優勢的來源?

在這里我們將深入為大家解答:FPGA商業模式的本質是什么?為什么龍頭能有這么強的護城河?我們認為,FPGA的商業模式的本質是,用高標準化的芯片覆蓋長尾市場以產生經濟性;龍頭之所以能有強的壟斷性份額,是因為其在一種客戶鎖定下的規模經濟下運作,使得龍頭可以在多輪迭代中不斷積累自身優勢,侵蝕其他玩家的份額,在這一過程中,落后的廠商不斷被淘汰,而行業的進入壁壘在不斷地提高。 FPGA商業模式的本質是用高標準化的芯片覆蓋長尾市場,以產生經濟性,這些小批量應用累積起來的出貨量足以支撐FPGA的制程不斷升級。正如我們系列報告一提到的,FPGA是高度標準化的芯片,通過改變FPGA中LUT4里面的16位掩碼,就能靈活地對應不同的組合電路,再結合寄存器,可以完成時序電路的功能,從而實現任意電路的“可編程”。這一硬件可編程的特性,使得同一片FPGA既可以在5G的基站中實現信道編碼的功能,也可以在重新配置后放在數控機床中實現電機控制的功能。因此,FPGA又被稱作“萬能”芯片,可以用于實施任何電路設計。而ASIC/ASSP面向的是特定方向的大批量應用,諸如手機、PC、TV、機頂盒等的每年在500萬顆以上、甚至上億顆出貨量的市場。針對這些大批量的市場,專門開發一顆ASIC/ASSP足以攤平前期投入的研發成本。然而,隨著芯片制程的提升,研發成本變得愈發昂貴,為小批量的應用開發一顆ASIC/ASSP變得越來越不經濟,越來越多的客戶轉向使用FPGA。2017年,16/14nm的節點研發成本為1.8億美元,往往需要每年9億美元以上的市場才能覆蓋這一成本;開發7nm節點需要3.5億美元,研發成本和市場容量要求翻倍。而FPGA可以提供幾乎是最先進的節點、大量FPGA廠商自研/合作伙伴的免費IP,立刻可用的芯片為用戶的產品提供了更快的上市速度。隨著越來越多ASIC方案的用戶轉為使用FPGA進行量產,FPGA市場開始快速成長,從1990年的1億美元增長為2022年的83億美元。 ?

FPGA每一代產品一般從推出開始算起,大概在第4-5年達到收入的巔峰,近60%收入來自于前6年。從在售時間計算,一個FPGA的生命周期大概為10-15年,根據Altera的數據,銷售收入的頂峰一般發生在FPGA新品推出后的第4-5年,這是由于FPGA有著非常陡峭的降價曲線。Xilinx一般在新品推出的第2年后,價格降幅就能達到50%,在第9年的價格相比剛推出時的價格降幅高達90%,而出貨量的頂峰一般在第5-6年達到,這一價格和需求曲線的變化規律,使得FPGA生命周期中約60%的收入在前6年發生,后9年FPGA參與者面對的是量價齊跌的市場。因此,FPGA廠商的策略是盡可能參與到前6年的市場份額分配中。

實際上,前2-3年的制程領先對FPGA市場競爭格局非常重要。因為即使能在后9年獲得高市場份額,FPGA廠商得到的收入也非常的少。事實上,量大的客戶在前兩年就會被領先的玩家鎖定,后面新增的客戶基本為新轉移到更先進代際的客戶。因此,如果不能做到前兩年內推出新一代制程的產品,基本就會錯失這一代產品市場收入最多的階段。

FPGA如何鎖定客戶?由于最關鍵的布局布線只能在FPGA廠商自己的EDA進行,FPGA的軟硬件形成了極強的綁定。高轉換成本令客戶非常容易被鎖定,進而在整個生命周期形成穩定的需求量。FPGA廠商在發布新一代產品的原型開始,就會對客戶進行送樣測試,客戶在數個FPGA供應商之間進行選擇。一旦完成選型后,FPGA廠商就完成了一個“design-win”,這是因為客戶需要在FPGA上完成自己的電路設計,不會再更換FPGA供應商。正如我們系列報告一和前文中解釋的,將電路在FPGA上實現,最關鍵的環節是在布局布線。FPGA之所以能綁定客戶,是因為FPGA的布局布線從來只能在對應的FPGA廠商自己的EDA中完成,使得軟硬件形成了極強的綁定。并且,由于不同廠商FPGA的細節、EDA環境各不相同,轉換到另一家FPGA廠商是非常困難的。對于越大型的設計,轉換的難度更高,一般需要重新走一遍“綜合-布局布線”的流程,并伴隨著大量的調試工作,而這些新FPGA平臺的適配工作通常可以耗費近半年時間。因此,如無必要,客戶通常不會更換FPGA廠商,而是根據自身的量產計劃每年重復訂購,展現非常強的客戶粘性。這使得頭部玩家在獲客上有非常明顯的規模效應,穩定的客戶進一步鞏固了市占率。

高客戶黏性使得FPGA頭部玩家出現獲客成本的規模經濟,進一步提升了行業的進入壁壘。同樣地,為了減少轉換成本,客戶會傾向于沿用上一代FPGA的供應商,即跨代際的客戶黏性也非常強,這使得FPGA的頭部廠商在獲客成本上出現規模經濟。隨著Xilinx的市占率從1990年的19%上升到2003年的50%,其SG&A(銷售和管理費用)占收入比例從接近30%下降至20%,在Xilinx鞏固了市場地位后的20年間,又逐年下降至接近10%的水平。Altera同樣,SG&A比例從90年代最高的25%下降至2014年的16%,充分說明了頭部在獲客上的規模優勢。

因此,對于FPGA廠商來說,競爭策略就是盡可能領先對手推出新一代的產品,在前2年完成盡量多的Design-wins,以獲得更多被鎖定的客戶。由于選型的一過程通常持續9-12個月,如果有廠商在新品發布上可以做到領先對手大半年以上的時間,那客戶通常只能選擇這家廠商的產品進行設計,并在1-2年后量產,領先廠商因此能在早期獲得100%的份額。這也是為什么FPGA的制程領先往往能夠預測2年之后的市場份額。例如,Xilinx在2015年9月發布16nm的UltraScale+新品,而競爭對手Altera在2016年10月才發布14nm的Stratix 10,落后Xilinx一年以上的時間,這使得2017年6月時,Xilinx在新一代產品的市場份額達到了100%。

在獲得強勁的Design-wins之后,FPGA廠商憑借HVM(High-Volume Manufacture)階段的大量訂單迅速降低成本,并進一步開啟激進的降價,以阻止落后競爭者的進入。在客戶完成選型后,便開始自己的系統設計,完成最終的下游客戶送樣之后,就開始向FPGA廠商下大批量生產的訂單,一般客戶會在2年內完成選型到系統設計。一旦開啟HVM階段,FPGA廠商可以迅速攤平前期投入的包括NRE、軟件研發等的固定成本,并開始激進地降價。例如,Xilinx新品推出后每年降價30%,兩年累計降價50%。因此,制程落后2年以上的FPGA廠商,往往面臨著非常強的進入壁壘。我們測算,即使在第5年開始每年獲得市場上15%的需求量,在整個歷史周期獲得的累計收入也僅有整體市場的6%,往往不足以支撐下一代新品的研發。而龍頭可以獲得這一代FPGA在整個生命周期中59%的收入,足夠用于下一代產品的研發。換句話說,落后廠商會愈發落后,龍頭在新一代產品的競爭者會越來越少。

?

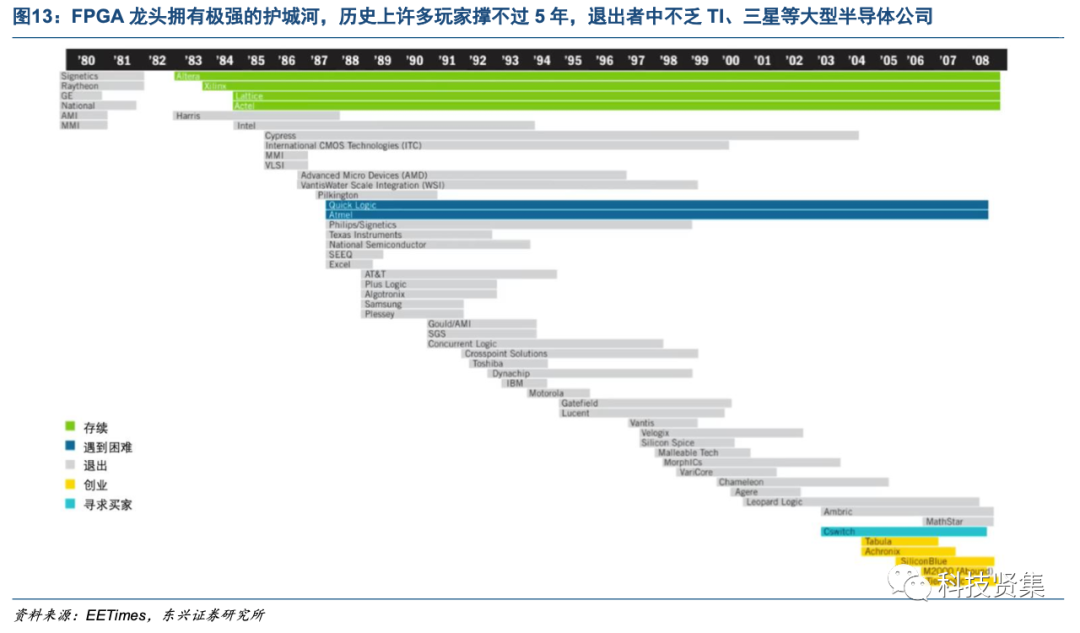

這也是為什么歷史上許多玩家撐不過5年的原因,落后的廠商無法獲得足夠的收入投入到下一代產品的高昂的開發中,選擇退出。在2-3輪迭代后,市場上其他玩家的比例會大幅減少,市場份額會向頭部集中。

除了成本之外,龍頭在產品定價上具有明顯的溢價。行業龍頭之外的玩家的產品普遍出現折價的情況。例如,行業第二名Intel/Altera的產品布局與Xilinx類似,其高、中、低產品線指標與Xilinx相近,但在電信、數據中心和A&D三個市場,平均售價均比Xilinx低20%以上。而行業第3-4名Microchip的產品集中在低價的中低容量領域,因此平均價格比Xilinx低80%-90%。

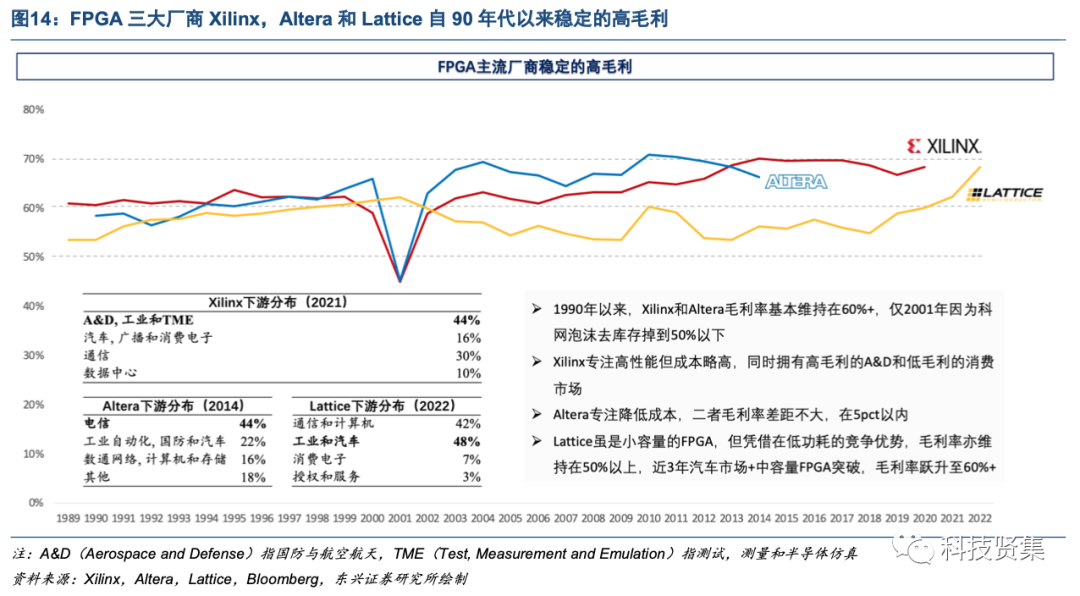

FPGA頭部廠商毛利率均穩定維持在60%+的高水平區間。1990年以來,Xilinx和Altera的毛利率基本維持在60%以上,僅2001年因為科網泡沫去庫存掉落至50%以下。其中,Xilinx專注高性能,但同時成本亦略高,下游來看,Xilinx同時擁有高毛利的A&D和低毛利的消費市場;而Altera下游集中在通信市場,來自A&D市場的收入占比較低,雖然價格低于Xilinx,但專注降低成本。綜合考慮下來,二者毛利率差距不大,在5pct以內。Lattice雖然是中小容量的FPGA,但憑借在低功耗的競爭優勢,毛利率也能維持在50%以上,近3年來更是憑借汽車市場的優勢和中容量FPGA的突破,將毛利率提升至60%+。

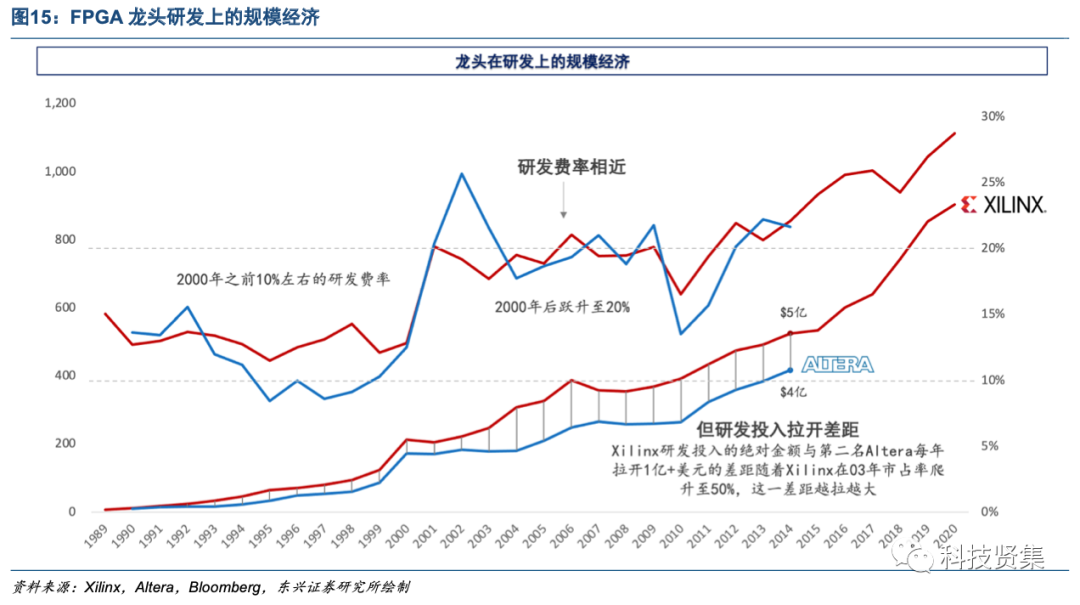

FPGA龍頭在研發上同樣具有規模經濟。作為龍頭,Xilinx可以在研發費率正常的情況下,絕對金額與第二名Altera每年拉開近1億美元以上的差距,隨著Xilinx在03年市占率爬升至50%,這一差距越拉越大。每年在研發上多出來的投入可以用于加強自身的競爭優勢,比如更多的技術/架構創新、更完善的EDA開發、更快的研發進度等方面,而不必損失盈利能力。

FPGA廠商收入曲線的本質是每一代產品收入曲線的疊加,必須每2-3年推出新品,以避免產品周期造成的收入下滑。我們測算,如果FPGA公司每2年推出新品,每一代產品價值量是上一代的1.2倍,公司的收入曲線將呈現“臺階狀增長”的特征。如果新品推出節奏延緩到每4年一次,在每一代產品價值量依然是上一代的1.2倍,公司的收入會出現階段性的下滑。因此,FPGA等迭代迅速的數字芯片公司,必須每2-3年就要推出更高價值量的新品,以避免收入出現“青黃不接”的情況,龍頭Xilinx更是每1-2年就推出新品。除了產品周期外,FPGA廠商的收入曲線還疊加了當年的宏觀經濟、個別下游需求、庫存水平等因素的影響。例如,1996-1997年、2000-2001年、2007-2009年、2012年、2015年、2018-2019年都有宏觀經濟下滑背景下半導體行業去庫存的情況。

?

03?

FPGA廠商之間的競爭,究竟在“拼什么”?

龍頭賽靈思如何培育競爭優勢?

我們從FPGA的客戶的視角分析,發現客戶對FPGA主要有兩大訴求:一是為自己的產品獲得競爭力的提升,二是降低開發的風險。一般來說,系統的競爭力來自于在性能、功耗、可靠性、上市速度和成本上的綜合表現,FPGA的客戶——工程師在設計其產品時往往是基于以上五個維度思考,并在產品設計上做出自己的權衡。通常來說,更先進代際的FPGA能提供更好的性能和功耗表現,能做到更小的芯片或者相同面積下更高的性能,使得自家產品更受消費者的青睞。因此,選擇制程領導者是慣例。除此之外,在以上五個維度的表現最貼近自身情況,即產品定義最接近需求的FPGA,往往會獲得青睞。

第二,工程師會優先選擇能持續迭代的產品,需要FPGA公司做出產品演進的承諾,以避免發生自己產品迭代時需要更換FPGA廠商的情況。更重要是,由于從新品推出到量產往往需要9-12個月,工程師會優先選擇那些有可靠量產歷史的廠商,以避免出現FPGA廠商倒閉,導致的自己產品不能量產的風險。此外,FPGA廠商提供的各種軟IP對于工程師來說是非常有吸引力的,從EDA的IP庫中調用FPGA廠商的提供的IP,可以極大地節省他們的開發時間和難度,如果FPGA廠商提供的IP很少、或者可靠性不高,則是扣分項。

?

?

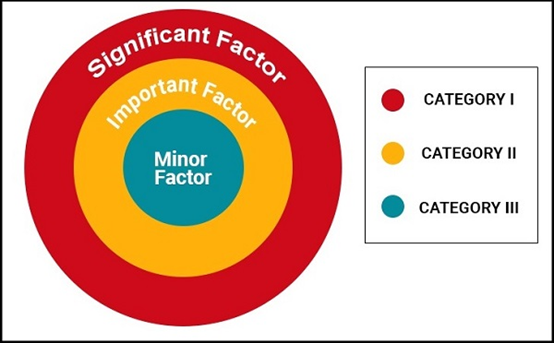

除了產品競爭力以外,工程師的另一大訴求是降低開發風險,他們在選擇某一個廠商的FPGA時,往往是由于過去在這家廠商的開發體驗很好,而換開發環境是每一個工程師竭力避免的。由于各家FPGA和EDA細節各不相同,在一家FPGA廠商能跑通的設計,直接不加調試轉移到另一家FPGA廠商能跑通的可能性非常低,其中的工作量往往具有高度的不確定性。因此,為了降低開發的成本和風險,如無必要,工程師往往不愿意切換到新的FPGA廠商。此外,FPGA廠商的技術支持也是非常重要的考慮,在FPGA的開發中的時常會遇到各種問題,對于大客戶來說往往有充分的FAE對接支持,但是FPGA更多的是中小客戶群體,此時FPGA如果有充分的技術文檔、或者有完備的開發社區,就能減少大部分開發遇到的問題。 ? 從客戶的視角延伸到FPGA競爭的關鍵因素,我們總結為以下六點:客戶關系、產品、IP庫、軟件、制造和運營能力,并在圖中逐一回答了賽靈思在這六個因素中如何做到獨一無二,即賽靈思是如何培育自己的競爭優勢的。 ? 我們認為,賽靈思成為龍頭的原因在于:1)制程領導者。正如我們前文分析,制程是FPGA市場份額的最直接競爭因素。除了0.13μm和40nm之外,賽靈思一直是行業內制程領導者的角色,能持續開啟“技術領先-訂單-成本優勢-客戶黏性-下一代研發投入”的正向循環; ?

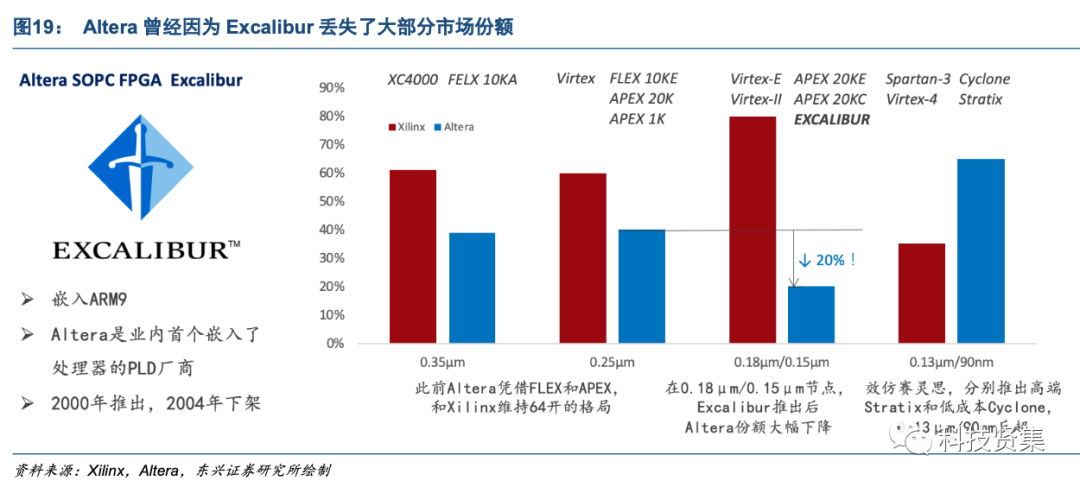

2)對客戶的需求把握最好,優秀的競爭策略制定和執行能力。在FPGA中嵌入固化單元,往往比使用LUT、寄存器等萬能資源來說,擁有更低的功耗和面積。盡管如此,要嵌入哪些固化單元需要設計者權衡,因為FPGA的開發者購買的是整個芯片,他們仍有可能為自己不需要或者不使用的功能付費;另一方面,如果FPGA的固化功能太少,其在市場上的競爭力就大為降低,因為客戶不得不使用太多的寶貴的可編程邏輯資源,去實現本來應該固化的功能,功耗和時延均大幅增加。這都需要FPGA公司有非常好的客戶的溝通。因此,早在1998年,賽靈思就區分了高端和低容量的市場,針對低容量市場推出了低成本的Spartan,面向那些需要FPGA的靈活性和高并行性,但又不需要通信市場一樣需要收發器等高性能的硬核的場景。而00年Altera專注于推出最高性能的Excalibur,并沒有重視低容量市場,直到Excalibur失敗后,2002年Altera才效仿賽靈思推出高端的Stratix和低成本的Cyclone。除了產品,賽靈思在98年第一個在Virtex上實現了FPGA的遠程升級功能,只需要簡單地將編程文件發送到聯網的設備中,就可以使其符合不斷變化的通信標準,不需要工程師走到基站一個個升級軟件,而這一點是當時很多ASIC所沒辦法做到的。這一遠程重配置功能的加入為客戶節省了大量的時間和金錢的成本,使得Virtex在通信市場大受歡迎,推動Xilinx的市場份額從98年的30%提升至03年的50%。 Altera歷史上在Excalibur的失敗,說明了產品定義和需求匹配的重要性。在FPGA上嵌入處理器硬核,早在2000年就有過嘗試。在0.18/0.15μm節點中,Altera為了和賽靈思在性能上競爭,將ARM9嵌入到了其最新的SOPC FPGA Excalibur中,成為業內首個將處理器嵌入到FPGA的廠商。然而,剛剛經歷科網泡沫的客戶將功耗提升到了和性能同等重要的位置,不愿意為過高性能的FPGA付費,對FPGA需求仍然在靈活性上,使得Altera在0.18/0.15μm的FPGA市場份額陡降至僅有20%,而此前賽靈思和Altera一直都維持在6-4分成的局面。Altera之后吸取了教訓,在嵌入固化單元時進行了非常小心的考慮,不再一味強調產品的性能,而是強調了解客戶需求,并在2002年推出了針對高端市場的Stratix和中低容量的Cyclone,在0.13μm/90nm市占率反超賽靈思。然而,?Xilinx在FPGA全市場的市占率已經和Altera拉開了明顯差距。1999年,Xilinx和Altera市占率分別為35%和33%,相當接近;在2000-2002年,Xilinx憑借高性能的Virtex在業內樹立了技術領導者的地位,以及低成本的Spartan迅速擴大客戶群和出貨量,市占率迅速爬升,在2002年達到了49%,而Altera市占率降低到了31%,基本錯失了最佳的追趕期。

?

?

3)生態的培養效果最好。賽靈思有著所有FPGA廠商中最完備的文檔說明,這一點對于中小客戶來說非常有吸引力,因為他們通常沒有大客戶擁有的FAE支持。在用戶群體培養中,在高校中FPGA教學中幾乎都會以賽靈思為例,工程師的基礎最好。在IP庫中,賽靈思擁有最完整的IP庫,910個IP中,近60%是自研IP,用戶可以直接調用,不需要自己重新研發,而Altera約為278個,選擇范圍遠小于Xilinx。除此之外,Xilinx在多個維度上有非常強的綜合表現,包括EDA的迭代速度、易用性等。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論