什么是FPGA原型?? FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能

2022-07-19 16:27:29 1735

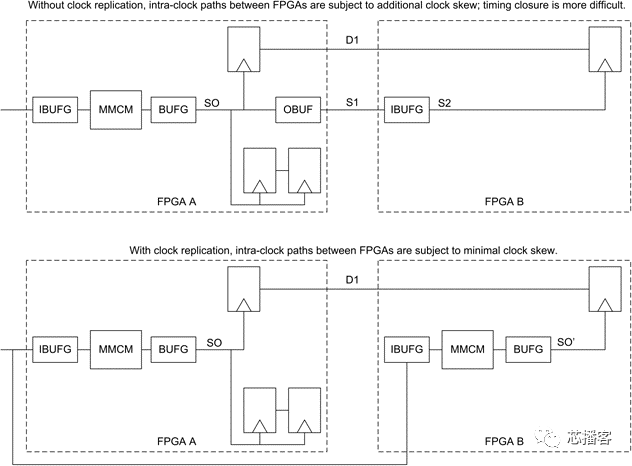

1735 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣:

2023-04-25 11:15:20 1629

1629

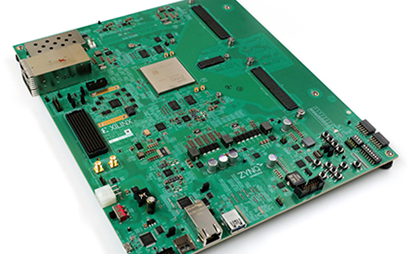

國微思爾芯發布3億門原型驗證系統,采用業界最高容量的 Intel? Stratix? 10 GX 10M FPGAs。

2020-09-08 10:56:20 883

883 Tape Out并回片后都可以進行驅動和應用的開發。目前ASIC的設計變得越來越大,越來越復雜,單片FPGA已不能滿足原型驗證要求,多片FPGA驗證應運而生。本文我就將與大家探討FPGA原型驗證的幾個經典挑戰性場景,(具體應對的辦法,請戳原文。)容量限制和性能要求

2020-08-21 05:00:12

一般我們用的FPGA的時鐘都是用晶振來提供的,我想請教一下大家,可以用鎖相環芯片AD9518(或者其它鎖相環)來生成時鐘供給FPGA,作為FPGA的系統時鐘

2013-08-17 11:20:41

大家好,我最近設計了一塊FPGA板子,FPGA焊接上去,我想看一下FPGA是否能正常工作,請問大家有哪些辦法

2014-04-30 17:22:21

各位專家好:

??????? 關于多片C6678的同步調試問題想咨詢下:

?????? 我打算做兩個板子,每個板子上集成兩片C6678的芯片,板間通信打算用光傳輸,現在想咨詢的問題是在用CCS進行調試的時候,這個能不能實現同步調試,比如在某個時間一起停下來,去看看各自寄存器或者變量的值。謝謝。

2018-06-21 02:37:42

調試過程中發現:多片AD9361同步后,一段時間內相位恒定,散熱風扇撤掉或者一二十分鐘后會有片子相位翻轉180°,片子位號隨機,請問一下這個是片子本身特性還是散熱影響(若散熱影響,麻煩告知影響機理),又或者代碼哪里未設置對?期待您的回答

2023-12-07 07:36:42

Hi,ADI我們現在在做一個5.8GHz的多通道接收機系統,需要多片AD9361之間載波相位同步我在AD9361的userguide UG570 page19,發現ad9361的external LO只能支持70MHz至4GHz?我的理解是否正確如果我希望使用5.8GHz的本振同步,有方法實現嗎?

2018-10-08 10:51:27

多片AD9680如何同步?需要注意什么問題?

2023-12-08 08:02:57

用FPGA控制兩片AD9739(以下簡稱A和B),其中A的SYNC_OUT接到了B的SYNC_IN,而A的SYNC_IN和B的SYNC_OUT接到了FPGA中。

現在配置0x10寄存器,采用無同步

2023-11-27 14:45:26

用4片AD9910,各種模式輸出單片的調試都沒有問題。現在要調多片同步,按照數據手冊上的要求進行各個寄存器的配置,25M參考時鐘輸入,內部用鎖相環陪頻到1G,就是多片同步不了,12腳一直為高,檢測

2018-11-20 09:11:33

用4片AD9910,各種模式輸出單片的調試都沒有問題。

現在要調多片同步,按照數據手冊上的要求進行各個寄存器的配置,25M參考時鐘輸入,內部用鎖相環陪頻到1G,就是多片同步不了,12腳一直為高,檢測不到有效地SYNC_IN信號,不知道原因,請技術支持幫助

2023-11-27 06:00:09

工作電路由輸入時鐘(CLKIN)實現同步,而后端電路由工作時鐘(PROCLK)實現同步, 為了使四片DDC和EPLD之間系統時鐘同步,系統要求用一個時鐘信號源產生四路相干時鐘分別分配給EPLD和四片

2019-06-04 05:00:17

通道驗證同步和校準軟件開發與生產硬件開發并行為了應對這一行業挑戰,有一個基于軟件可配置的高速轉換器的新型多通道RF到位開發平臺。該開發平臺集成了數據轉換器,RF分配,功率調節和時鐘,以提供16通道直接S

2020-08-21 14:24:29

在STM32f407XX系列中,系統時鐘(SYSTEM)默認的是HSE提供的,這里舉例我們就將默認HSE切換成HSI提供。我們先來看一下時鐘樹(建議保存此圖)首先、在系統中時鐘都是設置好的,如果不是

2021-08-10 07:57:18

我們來看一下MCU設計中的情況,其中IoT RAM明顯比外部DRAM具有優勢。在下面的通用MCU圖中,工作/靜態存儲器部分越來越需要擴展。在整個工作空間中使用DRAM會增加系統的功耗,并需要集成刷新

2021-11-10 06:59:22

原型驗證---用軟件的方法來發現硬件的問題 在芯片tap-out之前,通常都會計算一下風險,例如存在一些的嚴重錯誤可能性。通常要某個人簽字來確認是否去生產。這是一個艱難的決定。ASIC的產品NRE

2019-07-11 08:19:24

with Tcl...........................................953.9 Gate Clock 處理............................................993.10 多片 FPGA 驗證

2015-09-18 15:26:25

ASIC設計-FPGA原型驗證

2020-03-19 16:15:49

最近在做一個項目,負責單片機與FPGA的SPI口收發通信驗證任務。將沒有往SPIbuf里寫數據時,將單片機設為幀主模式,在signaltap端可以看到時鐘信號和片選信號的變化,但調試時會發現程序卡在

2015-09-27 17:15:52

適合SoC設計的一款支持嵌入式處理器和較大軟件內容的獨特驗證平臺。與所有HAPS-50系統一樣,HAPS-51也采用可編程時鐘發生器,支持高級監控和自檢測特性以及遠程配置與設置功能。此外,多塊功能板

2018-11-20 15:49:49

`我的keil用不了,幫我看一下,怎么解決啊`

2013-04-13 21:32:12

采用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。 目前的頂級

2019-07-12 06:38:15

摘要:隨著石油勘探的發展,在地震勘探儀器中越來越需要高精度的同步技術來支持高效采集。基于這種目的,采用FPGA技術設計了一種時鐘恢復以及系統同步方案,并完成了系統的固件和嵌入式軟件設計。通過室內測試

2019-06-18 08:15:35

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

我想做多個FPGA的時鐘同步,目前的想法是用一個FPGA的內部時鐘,復制到外接IO口,接到另一個FPGA的外部時鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復制多次,驅動多個FPGA的同步嗎。對驅動能力有什么要求?其中每一個FPGA都用的是一個EP4CE的最小系統板。

2019-01-21 15:07:41

FPGA/CPLD設計(高級篇)(第2版)》選擇ALTERA的器件可以看一下這兩本《設計與驗證Verilog HDL》 吳繼華,王誠 這書不錯,看電子版就好了《高級FPGA設計結構、實現也優化》(美)克里

2018-08-21 09:20:19

的設計和驗證的復雜性需求。隨著原型技術在設計分割以及多 FPGA 聯 合調試領域的進步,基于FPGA 的原型系統不僅可以滿足百萬門級的設計需求,還可以實現設計規模高達15 億門。基 于FPGA

2018-08-07 09:41:23

用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。 目前的頂級

2020-07-07 09:08:34

采用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。

2019-10-14 07:07:06

為什么不能采用基于現場可編程門陣列(FPGA)的原型?驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。

2019-08-13 07:45:06

`板主,注冊那天就激活了,但一直顯示是待驗證會員。按論壇任務提示也找不到“重新接收驗證郵件”鏈接按鈕在哪里?麻煩板主看一下是怎么回事,能不能幫忙人工改一下用戶組?謝謝。`

2016-12-06 11:33:33

請教大神如何利用FPGA實現原型板原理圖的驗證?

2021-04-29 06:57:34

和發送數據,處理異步信號,以及為帶門控時鐘的低功耗ASIC進行原型驗證。 這里以及后面章節提到的時鐘域,是指一組邏輯,這組邏輯中的所有同步單元(觸發器、同步RAM塊以及流水乘法器等)都使用同一個網絡

2022-10-14 15:43:00

請幫看一下這個圖有問題嗎,改成這樣可以嗎

2013-12-16 19:37:33

500MSPS的采樣,但是沒有提到任何多片同步的機制?有沒有具體的實現多片ADCs(8路數據,最少4片)的同步實現操作?

2019-01-11 08:06:29

請教一下論壇里的諸位大牛; 我需要用多片AD9361接收5.8GHz的射頻信號,如何保證多片AD9361的相位同步?因為AD9361的external LO只能支持70MHz至4GHz,不能滿足

2019-02-15 14:55:35

如何將多片AD9361芯片進行相位同步,技術文檔有說通過sync管腳進行MCS同步,但是僅僅只針對數據時鐘完成同步。個人理解數據相位主要由RF混頻處理以及后續數字處理決定,通過sync管教能夠完成

2018-12-25 11:42:25

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。

2019-06-18 07:43:00

原型驗證環境概述一套完整的RFID系統是由閱讀器(Reader)、電子標簽芯片(Tag)也就是所謂的應答器(Transponder)及應用軟件三部分組成。電子標簽芯片的FPGA原型驗證環境也是一套完整

2019-05-29 08:03:31

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40 隨著大容量高速度的FPGA的出現,在流片前建立一個高性價比的原型驗證系統已經成為縮短系統級芯片(SoC)驗證時間,提高首次流片成功率的重要方法。本文著重討論了用FPGA建

2009-09-11 15:50:09 16

16 FPGA驗證是基于VHDL的VLSI設計中非常重要的一個環節。用戶設計的電子系統首先必須是可綜合的,綜合之后再通過FPGA原型驗證,即可在物理層面對用戶設計完成實物驗證。通過FPGA驗證

2010-07-12 19:13:59 28

28 隨著SoC設計復雜度的提高,驗證已成為集成電路設計過程中的瓶頸,而FPGA技術的快速發展以及良好的可編程特性使基于FPGA的原型驗證越來越多地被用于SoC系統的設計過程。本文討論

2010-11-11 16:00:07 35

35 基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 2890

2890

富士通微電子正式采用亞科鴻禹FPGA原型驗證平臺

富士通微電子(上海)有限公司近日赴北京亞科鴻禹電子有限公司,圓滿完成了對StarFire-V530原型驗證板的測試驗收工作。

2010-02-24 08:50:34 740

740 新思科技有限公司推出HAPS-600 系列,這是其HAPS系列基于現場可編程門陣列(FPGA)原型驗證系統中容量最高的一款產品

2011-03-22 09:32:15 1437

1437 對ASIC設計進行FPGA原型驗證時,由于物理結構不同,ASIC的代碼必須進行一定的轉換后才能作為FPGA的輸入。 現代集成電路設計中,芯片的規模和復雜度正呈指數增加。尤其在ASIC設計流程中

2011-03-25 15:16:20 108

108 S2C日前宣布其Verification Module技術(專利申請中)已可用于其基于 Xilinx 的FPGA原型驗證系統中。V6 TAI Verification Module可以實現在FPGA原型驗證環境和用戶驗證環境之間高速海量數據傳輸。用戶

2011-09-20 09:07:58 1231

1231 新思科技公司日前宣布:該公司推出其Synopsys HAPS?-70系列基于FPGA的原型驗證系統,從而擴展了其HAPS產品線以應對系統級芯片(SoC)設計的不斷增加的規模及復雜度。

2012-11-27 21:51:39 1284

1284 如今,設計人員使用兩種相對獨立的方法進行 SoC 原型驗證:以事務級模型為基礎的虛擬原型驗證和基于 FPGA 的原型驗證。 虛擬原型驗證執行快速的 TLM,并可提供更高效的調試和分析方案,非常適合

2017-02-08 14:32:11 293

293 介紹了精密時鐘同步協議(PTP)的原理。本文精簡了該協議,設計并實現了一種低成本、高精度的時鐘同步系統方案。該方案中,本地時鐘單元、時鐘協議模塊、發送緩沖、接收緩沖以及系統打時標等功能都在FPGA

2017-11-17 15:57:18 6196

6196

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘

2018-09-01 08:29:21 5302

5302

以及ZYNQ 7020模組。XCVU13P主器件具有極其豐富的FPGA可編程邏輯資源,提供了強悍的算法原型驗證能力。同時平臺板載的ZYNQ 7020器件可用于系統管理并增強系統的靈活性。該平臺提供有

2020-05-19 10:50:05 2521

2521 從美通社獲知,2020年7月8日,國微思爾芯,全球領先的原型驗證解決方案供應商,推出新系列的原型驗證系統 Prodigy? S7。Prodigy? S7 是國微思爾芯第 7 代原型驗證系統,配備

2020-07-13 09:32:30 709

709 Virtex UltraScale+ VU19P是賽靈思密度最高的FPGA,是ASIC和SOC原型驗證的最佳選擇。

2020-10-22 14:23:13 1385

1385 ,加速超大規模設計驗證,提升設計性能 完整的原型驗證解決方案包括多FPGA深度調試,系統級協同建模及 90 多種應用接口子板庫 2020年10月22日,國微思爾芯,一站式EDA驗證解決方案專家,正式推出面向超大規模SoC原型市場的ProdigyTM S7-19P原型驗證系統。 S7-19P提供單、

2020-10-23 15:02:18 2375

2375 其次,部分FPGA開發板也被用在IP和小型芯片設計的開發驗證場景。這部分開發板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應開發驗證場景,一般由用戶自己負責手工實現從設計到FPGA功能原型的流程。

2022-04-28 09:38:33 2249

2249 電路,是可編程的邏輯陣列。FPGA 的基本結構包括可編程輸入輸出單元、基本可編程邏輯單元、數字時鐘管理模塊、嵌入式塊RAM、豐富的布線資源、內嵌專用硬核,以及底層內嵌功能單元。 ? 圖1? 某FPGA的基本邏輯單元?? 市售常見的基于FPGA的平臺產品包括FPGA開發板、FPGA原型驗證系統。既然

2022-04-28 14:16:59 2968

2968

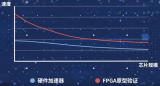

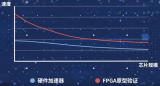

從系統的特性上看,FPGA 原型系統支持多FPGA、自動分割;性能較高的情況下運行系統軟件;仿真加速器的超大容量可以放全芯片的設計,進行全芯片的系統功能/性能/功耗驗證。

2022-05-25 09:35:13 7629

7629 FPGA(Field Programmable Gate Array)原型驗證,基于其成本適中、速率接近真實系統環境等優點,受到了驗證工程師的青睞。正是由于廣泛豐富的應用場景,FPGA 原型系統

2022-09-19 13:40:03 533

533

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-03-28 14:11:15 768

768 FPGA原型驗證在數字SoC系統項目當中已經非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統顯的格外重要

2023-04-03 09:46:45 928

928 當SoC系統的規模很大的時候,單片FPGA驗證平臺已經無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-04-06 11:20:48 603

603 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-04-07 09:42:57 594

594 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:03 628

628 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:37 443

443 FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 852

852 門控時鐘是一種在系統不需要動作時,關閉特定塊的時鐘的方法,目前很多低功耗SoC設計都將其用作節省動態功率的有效技術。

2023-04-20 09:15:13 764

764 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 426

426

多片FPGA原型驗證系統的拓撲連接方式各不相同,理想的多片FPGA原型驗證系統應該可以靈活配置,可以使用其相應的EDA工具

2023-05-08 11:51:40 326

326

FPGA原型驗證的原理是將芯片RTL代碼綜合到FPGA上來驗證芯片的功能。對于目前主流行業應用而言,芯片規模通常達到上億門甚至數十億門,一顆FPGA的容量難以容納下芯片的所有邏輯功能。

2023-05-18 12:52:52 381

381

當SoC的規模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統。

2023-05-23 15:31:10 319

319 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-05-23 15:46:24 481

481

FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制,通常只有1000個左右的用戶IO引腳。

2023-05-23 17:12:35 1149

1149

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 769

769

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

引言Preface如何快速便捷的完成巨型原型驗證系統的組網,并監測系統的連通性及穩定性?如何將用戶設計快速布局映射到參與組網的原型驗證系統的每一塊FPGA?隨著用戶設計規模的日益增大,傳統基于單片

2022-06-16 10:19:18 459

459

FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現在叫西門子EDA。

2024-01-22 09:21:01 546

546

FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 97

97 FPGA原型驗證平臺與硬件仿真器在芯片設計和驗證過程中各自發揮著獨特的作用,它們之間存在明顯的區別。

2024-03-15 15:07:03 131

131

電子發燒友App

電子發燒友App

評論