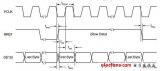

對于數(shù)據(jù)采集接收的一方而言,所謂源同步信號,即傳輸待接收的數(shù)據(jù)和時鐘信號均由發(fā)送方產(chǎn)生。FPGA應(yīng)用中,常常需要產(chǎn)生一些源同步接口信號傳輸給外設(shè)芯片,這對FPGA內(nèi)部產(chǎn)生

2012-05-04 11:42:26 4167

4167

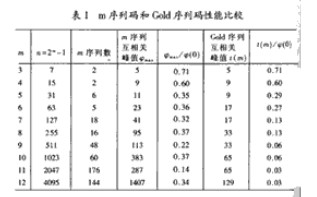

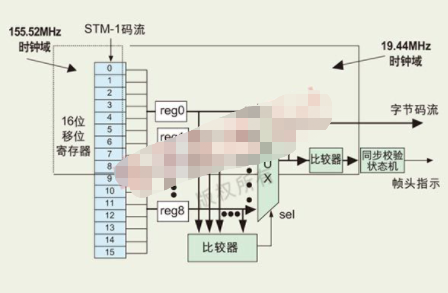

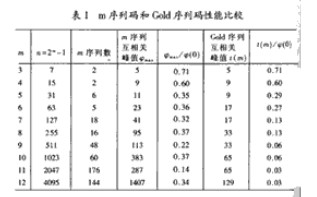

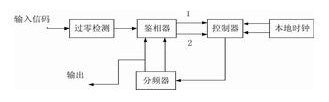

本文介紹一種基于現(xiàn)場可編程門陣列(FPGA)的通信系統(tǒng)同步提取方案的實現(xiàn)。本文只介紹了M序列碼作為同步頭的實現(xiàn)方案,對于m序列碼作為同步頭的實現(xiàn),只要稍微做一下修改,即加一些相應(yīng)的延時單元就可以實現(xiàn)。

2013-04-11 10:53:23 3829

3829

是指FPGA與外部器件共用外部時鐘;源同步(SDR,DDR)即時鐘與數(shù)據(jù)一起從上游器件發(fā)送過來的情況。在設(shè)計當中,我們遇到的絕大部分都是針對源同步的時序約束問題。所以下文講述的主要是針對源同步的時序約束。 根據(jù)網(wǎng)絡(luò)上收集的資料以及結(jié)合自

2020-11-20 14:44:52 6859

6859

時鐘使能電路是同步設(shè)計的重要基本電路,在很多設(shè)計中,雖然內(nèi)部不同模塊的處理速度不同,但是由于這些時鐘是同源的,可以將它們轉(zhuǎn)化為單一的時鐘電路處理。在FPGA的設(shè)計中,分頻時鐘和源時鐘的skew不容易

2020-11-10 13:53:41 4795

4795

“全局時鐘和第二全局時鐘資源”是FPGA同步設(shè)計的一個重要概念。合理利用該資源可以改善設(shè)計的綜合和實現(xiàn)效果;如果使用不當,不但會影響設(shè)計的工作頻率和穩(wěn)定性等,甚至?xí)?dǎo)致設(shè)計的綜合、實現(xiàn)過程出錯

2023-07-24 11:07:04 655

655

摘要:FPGA異步時鐘設(shè)計中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設(shè)計中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時根據(jù)實踐經(jīng)驗給出了解決這些問題的幾種同步策略。關(guān)鍵詞

2009-04-21 16:52:37

SDH設(shè)備時鐘(SEC)是SDH光傳輸系統(tǒng)的重要組成部分,是SDH設(shè)備構(gòu)建同步網(wǎng)的基礎(chǔ),也是同步數(shù)字體系(SDH)可靠工作的前提。SEC的核心部件由鎖相環(huán)構(gòu)成。網(wǎng)元通過鎖相環(huán)跟蹤同步定時基準,并通過

2019-08-07 07:07:21

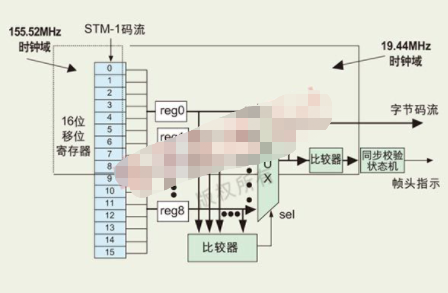

FPGA設(shè)計中幀同步系統(tǒng)的實現(xiàn)數(shù)字通信時,一般以一定數(shù)目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經(jīng)分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 16:22:49

FPGA設(shè)計中幀同步系統(tǒng)的實現(xiàn)數(shù)字通信時,一般以一定數(shù)目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經(jīng)分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 17:44:43

我們的設(shè)計用到了FPGA和AD9789進行CMOS電平的數(shù)字通信。fpga的時鐘跟AD9789的時鐘是異步的,不知道這樣的設(shè)計會不會導(dǎo)致fpga和ad9789的通信不穩(wěn)定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。謝謝!

2023-12-21 08:29:25

位同步時鐘的提取原理是什么?位同步時鐘的提取電路該怎樣去設(shè)計?

2021-05-07 06:51:36

你好,我在Viv 2016.4上使用AC701板。我需要同步從一個時鐘域到另一個時鐘域的多位信號(33位)。對我來說,這個多位信號的3階段流水線應(yīng)該足夠了。如果將所有觸發(fā)器放在同一個相同的切片

2020-08-17 07:48:54

你好,正在使用CH32V307VCT6連接一片fpga,遇到幾個問題: CH32V307VCT6 的FSMC_CLK 如何設(shè)置為持續(xù)輸出時鐘信號,以作為fpga接口的時鐘信號

2022-06-15 09:42:04

視頻信號(包括數(shù)據(jù)與時鐘,其中數(shù)據(jù)位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數(shù)據(jù)的延時,也就是信號的建立與保持時間在經(jīng)過FPGA后出現(xiàn)偏移。造成后端的DA不能正確的采集到數(shù)據(jù)。

2014-02-10 16:08:02

。 對于一個設(shè)計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預(yù)測的時鐘。在CPLD/FPGA設(shè)計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅(qū)動的單個主時鐘去控制設(shè)計項目中的每一個觸發(fā)器。 只要

2012-03-05 14:29:00

拉票第一名,所以直接獲得試用機會項目描述:位同步時鐘提取現(xiàn)在本科階段平時喜歡鉆研,征戰(zhàn)了2016TI杯電子設(shè)計競賽,并獲得省二,對FPGA以及Verilog HDL有一定程度的了解,自己通過FPGA

2016-08-29 15:40:44

CAN里有一個位同步的概念,我以前用STM32時,還有專門用于做位同步的結(jié)構(gòu)體請問我現(xiàn)在用FPGA作CAN,需不需要設(shè)計位同步?還是外接的獨立CAN控制器自己本身就有位同步

2018-10-10 09:35:45

?注意:合成頻率將在FPGA內(nèi)部用于讀取fifo,但也通過oddr轉(zhuǎn)發(fā)到外部芯片。我對在FPGA內(nèi)部實現(xiàn)dpll的其他方法持開放態(tài)度。謝謝。

2020-07-31 10:19:37

同一個時鐘域中,或者來自不同的源(即使它們具有相同的時鐘頻率)在將信號同步到 FPGA 或不同的時鐘域時,有多種設(shè)計可供選擇。在xilinx fpga中,最好的方法是使用xilinx參數(shù)化宏,創(chuàng)建這些

2022-10-18 14:29:13

求大佬介紹一種基于現(xiàn)場可編程門陣列(FPGA)的同步方案?

2021-04-08 06:25:03

在FPGA上實現(xiàn)時鐘信號的多路同步輸出該怎么做呢?好像要用到FPGA內(nèi)部的PLL,將時鐘信號分成多路輸送到其他板塊,求高手解答該怎么做輸入時鐘由一個50M的晶振提供

2023-03-21 14:51:29

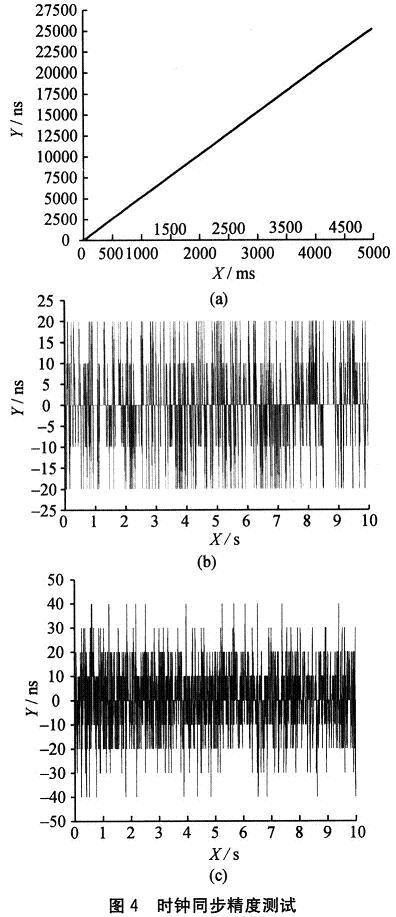

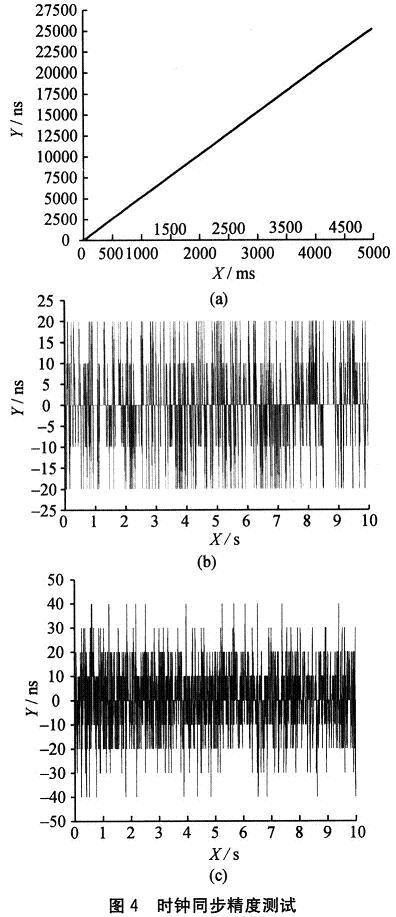

摘要:隨著石油勘探的發(fā)展,在地震勘探儀器中越來越需要高精度的同步技術(shù)來支持高效采集。基于這種目的,采用FPGA技術(shù)設(shè)計了一種時鐘恢復(fù)以及系統(tǒng)同步方案,并完成了系統(tǒng)的固件和嵌入式軟件設(shè)計。通過室內(nèi)測試

2019-06-18 08:15:35

數(shù)字電路中,時鐘是整個電路最重要、最特殊的信號:因此, 在FPGA設(shè)計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅(qū)動單個主時鐘去控制設(shè)計項目中的每一個觸發(fā)器。同步設(shè)計時,全局時鐘輸入一般都接在器件的時鐘端, 否則會使其性能受到影響。

2012-05-23 19:51:48

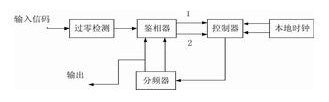

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個同步系統(tǒng),以實現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。一個簡單的接收系統(tǒng)框圖如圖1所示。

2019-09-17 06:28:08

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個同步系統(tǒng),以實現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。

2019-09-19 07:28:51

我想做多個FPGA的時鐘同步,目前的想法是用一個FPGA的內(nèi)部時鐘,復(fù)制到外接IO口,接到另一個FPGA的外部時鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復(fù)制多次,驅(qū)動多個FPGA的同步嗎。對驅(qū)動能力有什么要求?其中每一個FPGA都用的是一個EP4CE的最小系統(tǒng)板。

2019-01-21 15:07:41

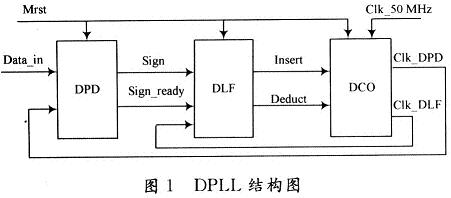

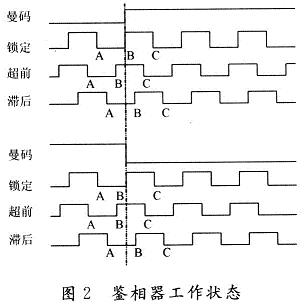

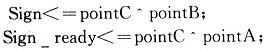

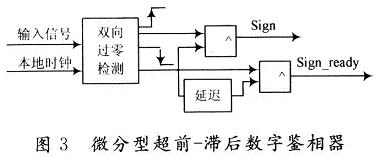

信息。自同步法又可以分為兩種,即開環(huán)同步法和閉環(huán)同步法。開環(huán)法采用對輸入碼元做某種變換的方法提取位同步信息。閉環(huán)法則用比較本地時鐘和輸入信號的方法,將本地時鐘鎖定在輸入信號上。閉環(huán)法更為準確,但是也更為復(fù)雜。那么,我們該怎么利用FPGA設(shè)計提取位同步時鐘DPLL?

2019-08-05 06:43:01

在串行數(shù)據(jù)傳輸?shù)倪^程中,如何在FPGA中利用低頻源同步時鐘實現(xiàn)LVDS接收字對齊呢?

2021-04-08 06:39:42

我們建議的設(shè)置如下:希望ADC工作在200 MHz,采樣速率為200 MSPS。最初,為了避免FPGA內(nèi)部操作和ADC數(shù)據(jù)之間的同步問題,我們計劃從FPGA驅(qū)動ADC輸入時鐘。現(xiàn)在我們擔心高采樣率

2020-08-25 09:23:10

微波作為無線和傳輸設(shè)備的重要接入設(shè)備,在網(wǎng)絡(luò)設(shè)計和使用中要針對接入業(yè)務(wù)的類型,提供滿足其需求的時鐘同步方案。當前階段,微波主要支持的時鐘同步類型包括:GPS,BITS,1588,1588

2019-07-12 07:46:39

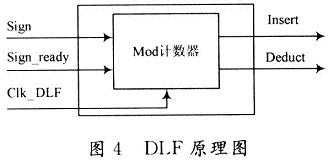

教你如何運用VHDL技術(shù)去設(shè)計DPLL?數(shù)字環(huán)路濾波器是怎樣設(shè)計的?

2021-04-08 06:05:32

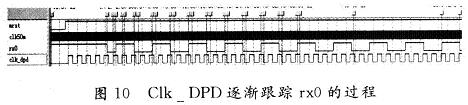

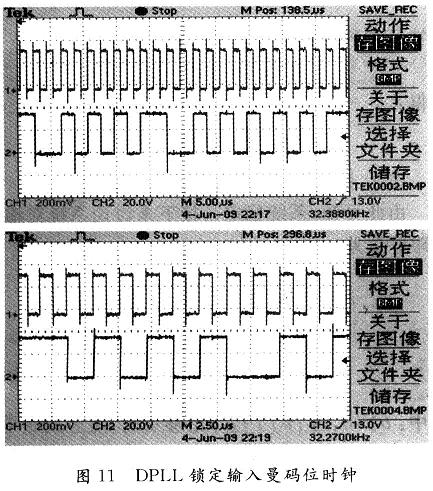

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數(shù)字鎖相環(huán)設(shè)計方法。

2021-05-06 08:00:46

求一種基于FPGA的鎖相環(huán)位同步提取電路的設(shè)計方案。

2021-04-29 06:52:21

的代碼時,都需要調(diào)整采樣時鐘的相位才能夠進行正確的采樣,有時調(diào)整相位也采樣不正確。這是采樣時鐘與數(shù)據(jù)不同步造成的么?我在網(wǎng)上看了一些資料,說可以使用idelay增加時鐘的延時,我的FPGA

2016-08-14 16:58:50

接口部分電路進行處理。 一般的時鐘同步化方法如下圖所示。 實質(zhì)上,時鐘采樣的同步處理方法就是上升沿提取電路,經(jīng)過上升沿提取輸出信息中,帶有了系統(tǒng)時鐘的信息,所以有利于保障電路的可靠性和可移植性

2018-02-09 11:21:12

)類型,例如FPGA上電時SPI閃存,FPGA CCLK為3MHz并且最初使用x1模式,FPGA如何知道SPI(或BPI)閃存的工作時鐘頻率和位寬?FPGA如何改變SPI(或BPI)閃存的工作時鐘頻率和位寬?

2020-05-06 10:21:02

計算FPGA外部引腳的頻率。我需要將其與內(nèi)部FPGA時鐘同步嗎?內(nèi)部參考時鐘以60Mhz運行,外部頻率在10khz到15khz之間變化,不同步的外部頻率是否會導(dǎo)致錯誤或問題?以上來自于谷歌翻譯以下

2019-06-18 09:37:29

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎(chǔ)上,提出了一種基于FPGA 的GPS同步時鐘裝置的設(shè)計方案,實現(xiàn)了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40 DLL在FPGA時鐘設(shè)計中的應(yīng)用:在ISE集成開發(fā)環(huán)境中,用硬件描述語言對FPGA 的內(nèi)部資源DLL等直接例化,實現(xiàn)其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發(fā)板設(shè)計中的

2009-11-01 15:10:30 33

33 本文設(shè)計了一種在數(shù)字通信系統(tǒng)中的數(shù)字鎖相位同步提取方案,詳細介紹了本設(shè)計的位同步提取原理及其各個組成功能模塊的VHDL語言實現(xiàn),并在Quartus II開發(fā)平臺上仿真驗證通過。本

2010-08-06 14:28:08 64

64 本文闡述了用于FPGA的可優(yōu)化時鐘分配網(wǎng)絡(luò)功耗與面積的時鐘布線結(jié)構(gòu)模型。并在時鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時鐘偏差,探討了FPGA時鐘網(wǎng)絡(luò)中鎖相環(huán)的實現(xiàn)方案。

2010-08-06 16:08:45 12

12 為實現(xiàn)設(shè)備中存在的低速數(shù)據(jù)光纖通信的同步復(fù)接/ 分接,提出一種基于FPGA 的幀同步頭信號提取檢測方案,其中幀頭由7 位巴克碼1110010 組成,在數(shù)據(jù)的接收端首先從復(fù)接數(shù)據(jù)中

2010-10-26 16:56:54 46

46 為實現(xiàn)分布式系統(tǒng)高精度同步數(shù)據(jù)采集及實時控制,提出一種基于IEEE1588協(xié)議的分布式系統(tǒng)時鐘同步方法。通過分析影響同步精度的因素,采用FPGA設(shè)計時間戳生成器,并且采用晶振

2010-12-30 15:52:22 41

41 同步信號的提取及行場計數(shù)器電路

準確提取視頻信號中的同步信號對于本項目的成攻至關(guān)重要,幸運的是市場上提供了LM1881芯片,它僅需幾個外接元件,就可

2009-12-08 14:48:22 2150

2150

基于FPGA的新型誤碼測試儀的設(shè)計與實現(xiàn)

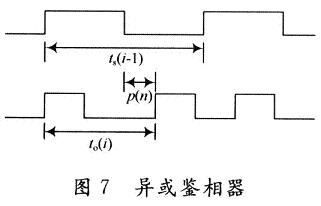

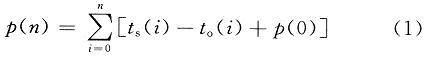

本文設(shè)計實現(xiàn)了一種用于測量基帶傳輸信道的誤碼儀,闡述了主要模塊的工作原理,提出了一種新的積分鑒相同步時鐘提取的實

2010-02-09 10:42:01 876

876

數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

背景知識:

隨著數(shù)字電路技術(shù)的發(fā)展,數(shù)字鎖相環(huán)在調(diào)制解調(diào)、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 5474

5474 同步網(wǎng)時鐘及等級

基準時鐘 同步網(wǎng)由各節(jié)點時鐘和傳遞同步定時信號的同步鏈路構(gòu)成.同步網(wǎng)的功能是準確地將同步定時信號從基

2010-04-03 16:27:34 3661

3661 FPGA的時鐘頻率同步設(shè)計

網(wǎng)絡(luò)化運動控制是未來運動控制的發(fā)展趨勢,隨著高速加工技術(shù)的發(fā)展,對網(wǎng)絡(luò)節(jié)點間的時間同步精度提出了更高的要求。如造紙機械,運行速

2010-01-04 09:54:32 2762

2762

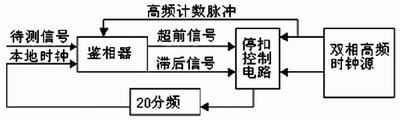

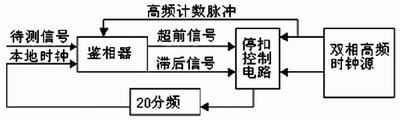

基于fpga的鎖相環(huán)位同步提取電路

該電路如圖所示,它由雙相高頻時鐘

2010-10-08 12:00:23 1483

1483

在FPGA設(shè)計中,為了成功地操作,可靠的時鐘是非常關(guān)鍵的。設(shè)計不良的時鐘在極限的溫度、電壓下將導(dǎo)致錯誤的行為。在設(shè)計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

FPGA 異步時鐘設(shè)計中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設(shè)計中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時根據(jù)實踐經(jīng)驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 同步技術(shù)是跳頻系統(tǒng)的核心。本文針對FPGA的跳頻系統(tǒng),設(shè)計了一種基于獨立信道法,同步字頭法和精準時鐘相結(jié)合的快速同步方法,同時設(shè)計了基于雙圖案的改進型獨立信道法,同步算

2013-05-06 14:09:20 22

22 DLL在_FPGA時鐘設(shè)計中的應(yīng)用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現(xiàn)的。

2015-10-28 14:25:42 1

1 位同步提取實驗的實驗報告,位同步提取實驗的實驗報告,位同步提取實驗的實驗報告

2016-05-26 10:58:41 0

0 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 目前,大型設(shè)計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發(fā)沿設(shè)計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設(shè)計的要求,一般在FPGA設(shè)計中采用全局時鐘資源驅(qū)動設(shè)計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 時鐘的管理。本文詳細介紹了利用嵌入式微控制器MSP430單片機和數(shù)字鎖相環(huán)(DPLL)來實現(xiàn)嵌入式同步時鐘系統(tǒng)的方案和設(shè)計實例。 系統(tǒng)總體結(jié)構(gòu) 同步設(shè)備的同步時鐘系統(tǒng)要求能達到3級時鐘標準,可使用從SDH網(wǎng)絡(luò)上提取的時鐘或外部時

2017-11-04 10:21:44 6

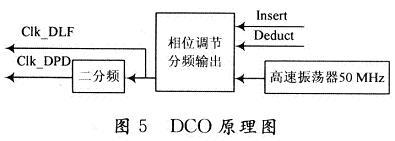

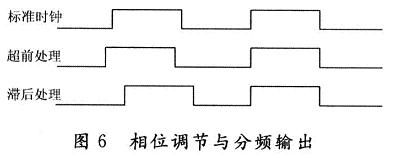

6 介紹一種采用FPGA(現(xiàn)場可編程門陣列電路)實現(xiàn)SDH(同步數(shù)字體系)設(shè)備時鐘芯片設(shè)計技術(shù),硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術(shù),可以在FPGA 中實現(xiàn)需要專用芯片才能實現(xiàn)的時鐘芯片各種功能,而且輸入時鐘數(shù)量對比專用芯片更加靈活,實現(xiàn)該功能的成本降低三分之一.

2017-11-21 09:59:00 1840

1840

介紹了精密時鐘同步協(xié)議(PTP)的原理。本文精簡了該協(xié)議,設(shè)計并實現(xiàn)了一種低成本、高精度的時鐘同步系統(tǒng)方案。該方案中,本地時鐘單元、時鐘協(xié)議模塊、發(fā)送緩沖、接收緩沖以及系統(tǒng)打時標等功能都在FPGA

2017-11-17 15:57:18 6196

6196

微波作為無線和傳輸設(shè)備的重要接入設(shè)備,在網(wǎng)絡(luò)設(shè)計和使用中要針對接入業(yè)務(wù)的類型,提供滿足其需求的時鐘同步方案。當前階段,微波主要支持的時鐘同步類型包括:GPS,BITS,1588,1588

2017-12-07 20:51:01 559

559 異步復(fù)位同步釋放 首先要說一下同步復(fù)位與異步復(fù)位的區(qū)別。 同步復(fù)位是指復(fù)位信號在時鐘的上升沿或者下降沿才能起作用,而異步復(fù)位則是即時生效,與時鐘無關(guān)。異步復(fù)位的好處是速度快。 再來談一下為什么FPGA設(shè)計中要用異步復(fù)位同步釋放。

2018-06-07 02:46:00 1989

1989 基于FPGA的數(shù)字系統(tǒng)設(shè)計中大都推薦采用同步時序的設(shè)計,也就是單時鐘系統(tǒng)。但是實際的工程中,純粹單時鐘系統(tǒng)設(shè)計的情況很少,特別是設(shè)計模塊與外圍芯片的通信中,跨時鐘域的情況經(jīng)常不可避免。如果對跨時鐘

2018-09-01 08:29:21 5302

5302

一般的位同步電路大多采用標準邏輯器件按傳統(tǒng)數(shù)字系統(tǒng)設(shè)計方法構(gòu)成,具有功耗大,可靠性低的缺點。用FPGA設(shè)計電路具有很高的靈活性和可靠性,可以提高集成度和設(shè)計速度,增強系統(tǒng)的整體性能。本文給出了一種基于fpga的數(shù)字鎖相環(huán)位同步提取電路。

2019-04-19 08:24:00 3113

3113

我們系統(tǒng)中,主板與從板之間通過交換網(wǎng)片的HW0、HW4互連,要使主板與從板的交換網(wǎng)之間能夠正常交換,必須使這兩個交換網(wǎng)片有一致的幀同步時鐘及位同步時鐘。在現(xiàn)在的單板中,從板的時鐘由主板直接送出。整個系統(tǒng)采用的時鐘源有3種方式:

2018-10-30 11:36:23 7

7 時鐘是FPGA設(shè)計中最重要的信號,FPGA系統(tǒng)內(nèi)大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 5065

5065

。 不要隨意將內(nèi)部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產(chǎn)生的時鐘,或者可以通過建立時鐘使能或者DCM產(chǎn)生不同的時鐘信號。 FPGA盡量采取同步設(shè)計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關(guān)系的異步時鐘,必須

2020-12-11 10:26:44 1482

1482 對于 FPGA 來說,要盡可能避免異步設(shè)計,盡可能采用同步設(shè)計。 同步設(shè)計的第一個關(guān)鍵,也是關(guān)鍵中的關(guān)鍵,就是時鐘樹。 一個糟糕的時鐘樹,對 FPGA 設(shè)計來說,是一場無法彌補的災(zāi)難,是一個沒有打好地基的樓,崩潰是必然的。

2020-11-11 09:45:54 3656

3656 引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時鐘資源架構(gòu),熟練掌握時鐘資源對于FPGA硬件設(shè)計工程師及軟件設(shè)計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 AD9546:雙DPLL數(shù)字化時鐘同步器數(shù)據(jù)表

2021-03-22 20:36:12 7

7 傳統(tǒng)的異步采集方法會影響采集到的功耗信息的信噪比,降低功耗分析的成功率。針對異步采集的問題提出一種新的時鐘同步功耗信息采集方法。該采集方法基于現(xiàn)場可編程門陣列(FPGA)的時鐘同步采集平臺

2021-03-31 15:50:21 6

6 對于一個設(shè)計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預(yù)測的時鐘。只要可能就應(yīng)盡量在設(shè)計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5827

5827

AD9542:四輸入、五輸出、雙DPLL同步器和自適應(yīng)時鐘轉(zhuǎn)換器產(chǎn)品手冊

2021-05-08 12:48:49 6

6 AD9545:快速輸入,10輸出,雙DPLL/IEEE1588 1小步同步和Jetter Clearan數(shù)據(jù)Sheet

2021-05-21 14:38:29 4

4 AD9543:四路輸入、10路輸出、雙DPLL/IEEE 1588同步器和抖動清除器

2021-05-27 15:35:55 3

3 ,首先要從同步數(shù)據(jù)流中提取幀同步信息,幀同步提取性能的優(yōu)劣直接影響整個數(shù)據(jù)的處理質(zhì)量與整個系統(tǒng)的性能。使用FPGA技術(shù)可以實現(xiàn)同步系統(tǒng)的模塊化、小型化和芯片化,得到穩(wěn)定可靠的幀同步器。

2021-06-23 15:44:00 2451

2451

(29)FPGA原語設(shè)計(差分時鐘轉(zhuǎn)單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設(shè)計(差分時鐘轉(zhuǎn)單端時鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設(shè)計(單端時鐘轉(zhuǎn)差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設(shè)計(單端時鐘轉(zhuǎn)差分時鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 ?xilinx 的 FPGA 時鐘結(jié)構(gòu),7 系列 FPGA 的時鐘結(jié)構(gòu)和前面幾個系列的時鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

2592 ASIC 和FPGA芯片的內(nèi)核之間最大的不同莫過于時鐘結(jié)構(gòu)。ASIC設(shè)計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結(jié)構(gòu)進行處理,但是 FPGA設(shè)計則完全不必。

2022-11-23 16:50:49 686

686

時鐘信號的同步 在數(shù)字電路里怎樣讓兩個不同步的時鐘信號同步? 在數(shù)字電路中,時鐘信號的同步是非常重要的問題。因為在信號處理過程中,如果不同步,就會出現(xiàn)信號的混淆和錯誤。因此,在數(shù)字電路中需要采取一些

2023-10-18 15:23:48 771

771 fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設(shè)備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導(dǎo)致通訊數(shù)據(jù)的錯誤

2023-10-18 15:28:13 1060

1060 中,時鐘是很重要的一個因素,而時鐘配置芯片則是為了提供時鐘信號而存在。 時鐘是FPGA中非常重要的因素,因為FPGA必須在時鐘邊沿上完成一次操作。時鐘信號決定了FPGA內(nèi)部計算和通訊的速度,因此時鐘信號的穩(wěn)定性和精度至關(guān)重要。 FPGA實現(xiàn)時鐘同步通常有兩種方式:一種是通過外部時鐘輸入

2023-10-25 15:14:20 1045

1045 兩個機器的時鐘怎么同步? 在現(xiàn)代社會中,時間同步對于各種科學(xué)研究、工業(yè)生產(chǎn)和通信技術(shù)都具有重要意義。在許多應(yīng)用程序中,如分布式系統(tǒng)、計算機網(wǎng)絡(luò)和數(shù)據(jù)同步等領(lǐng)域,為了確保數(shù)據(jù)的一致性和準確性,需要確保

2024-01-16 14:26:32 254

254 時鐘同步怎樣組網(wǎng)? 時鐘同步是計算機網(wǎng)絡(luò)中的重要問題,主要用于確保在多個節(jié)點之間保持時間的一致性。時鐘同步對于網(wǎng)絡(luò)的可靠性和性能至關(guān)重要,因此組網(wǎng)時時鐘同步必須仔細考慮。 在計算機網(wǎng)絡(luò)中,各個節(jié)點

2024-01-16 15:10:13 168

168

![]()

![]()

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評論