ASIC和FPGA具有不同的價(jià)值主張,在作出選擇前必須仔細(xì)評(píng)估。兩種種技術(shù)對(duì)比。這里介紹了ASIC和FPGA 的優(yōu)勢(shì)與劣勢(shì)。

2011-03-31 17:30:09 5382

5382

不久前,據(jù)國(guó)外媒體報(bào)道,華為公司正在首次使用ASIC來(lái)替代其設(shè)備中的FPGA芯片,而這些芯片原本采購(gòu)于FPGA主要廠商之一的Altera【 電子發(fā)燒友網(wǎng)關(guān)于此事報(bào)道:華為ASIC設(shè)計(jì)案,FPGA雙雄

2012-11-14 08:47:56 1970

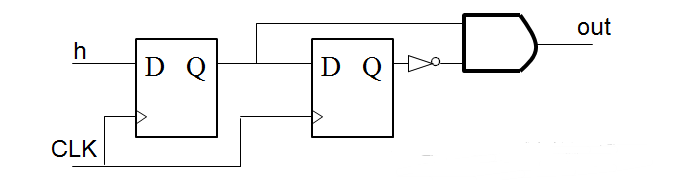

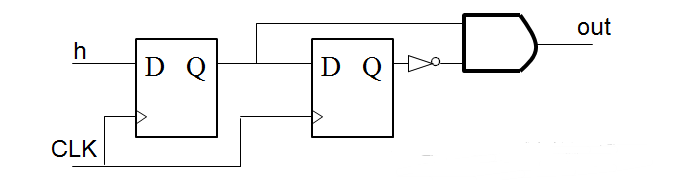

1970 要養(yǎng)成良好的Verilog代碼風(fēng)格,要先有硬件電路框圖之后再寫代碼的習(xí)慣,設(shè)計(jì)出良好的時(shí)序,這樣才能在FPGA開(kāi)發(fā)或者ASIC設(shè)計(jì)中起到事半功倍的效果,否則會(huì)事倍功半。

2020-11-19 13:54:02 3008

3008

ASIC的設(shè)計(jì)流程是怎樣的?FPGA的開(kāi)發(fā)流程又是怎樣的?

2021-11-01 07:08:47

原型驗(yàn)證過(guò)程中的ASIC到FPGA的代碼是怎樣進(jìn)行轉(zhuǎn)換的?

2021-05-08 09:16:18

1、概念區(qū)別: ASIC(專用集成電路)是一種在設(shè)計(jì)時(shí)就考慮了設(shè)計(jì)用途的IC。 FPGA(現(xiàn)場(chǎng)可編程門陣列)也是一種IC。顧名思義,只要有合適的工具和適當(dāng)?shù)膶I(yè)基礎(chǔ),工程師就可以對(duì)FPGA

2020-12-01 17:41:49

專用集成電路(ASIC)采用硬接線的固定模式,而現(xiàn)場(chǎng)可編程門陣列 (FPGA)則采用可配置芯片的方法,二者差別迥異。可編程器件是目前的新生力量,混合技術(shù)也將在未來(lái)發(fā)揮作用。 與其他技術(shù)一樣,有關(guān)

2019-07-19 06:24:30

.......................................51.5 Verilog 良好編程習(xí)慣........................................62基于 ALTERA 的 ASIC 驗(yàn)證

2015-09-18 15:26:25

ASIC設(shè)計(jì)-FPGA原型驗(yàn)證

2020-03-19 16:15:49

談?wù)?b class="flag-6" style="color: red">ASIC_FPGA_區(qū)別與聯(lián)系,也許面試的時(shí)候能用到

2012-05-23 19:47:59

。ASIC 的特點(diǎn)是面向特定用戶的需求, ASIC 分為全定制和半定制。亮點(diǎn)在于專用,量身定制所以執(zhí)行速度較快。一句話總結(jié)就是,市場(chǎng)上買不到的芯片。水果的 A 系列處理器就是典型的 ASIC。二、FPGA

2020-09-25 11:34:41

的小型項(xiàng)目,FPGA則更為適合。FPGA技術(shù)的主要優(yōu)勢(shì)仍是產(chǎn)品投放市場(chǎng)的時(shí)間較短。在ASIC的優(yōu)勢(shì)方面,ASIC加電后可立即運(yùn)行,就單位邏輯大小而言封裝選擇更多,還可包括某些模擬邏輯。與此相對(duì)比,FPGA

2017-09-02 22:24:53

,稱為半定制專用集成電路,相對(duì)來(lái)說(shuō)更接近FPGA,甚至在某些地方,ASIC就是個(gè)大概 念,FPGA屬于ASIC之下的一部分。FPGA基本就是高端的CPLD,兩者非常接近。我現(xiàn)在用的是ALTERA...

2021-11-24 07:09:18

ASIC是一種為專門目的而設(shè)計(jì)的集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計(jì)、制造的集成電路。ASIC的特點(diǎn)是面向特定用戶的需求,亮點(diǎn)在于運(yùn)行速度在同等條件下比FPGA快。FPGA作為

2017-06-12 15:56:59

FPGA與ASIC(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-10 11:34:28

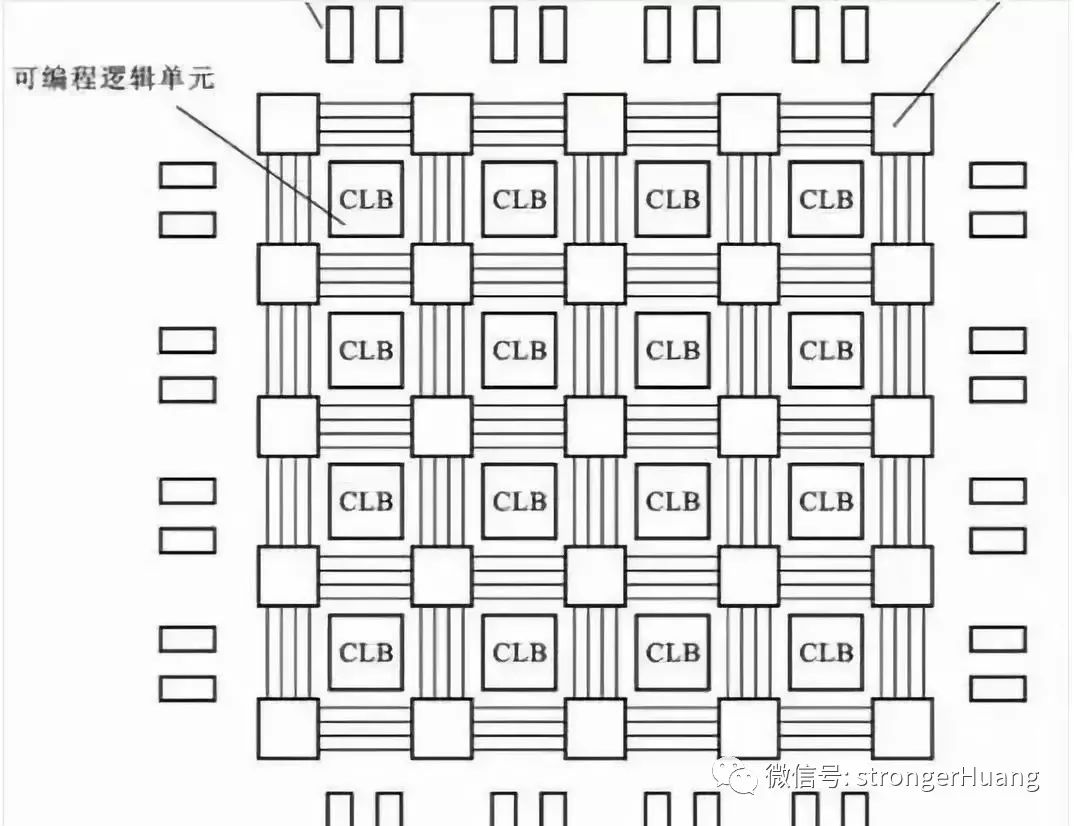

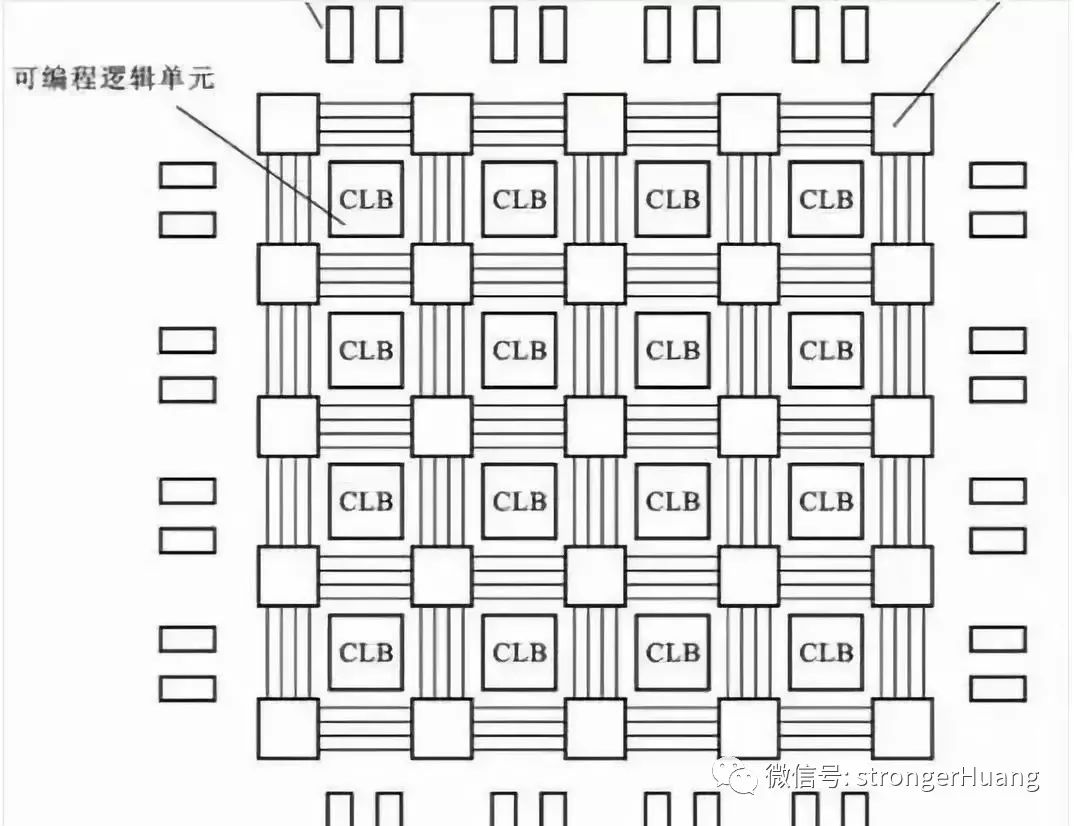

是由觸發(fā)器和查找表以及互聯(lián)線等基本結(jié)構(gòu)組成的,其實(shí)在我們?cè)诖a里面能夠看到的就是與非門以及觸發(fā)器,不要把verilog和c語(yǔ)言等同起來(lái),根本就是不同的東西,沒(méi)有什么可比性,在寫一句程序的時(shí)候應(yīng)該想到

2017-05-02 16:59:07

(60)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)11.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)15)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 06:42:51

(77)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)31.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)35)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 07:48:24

(59)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)11.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)15)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 06:57:59

(69)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)21.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)25)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 07:31:44

我已經(jīng)完成了我的fpga實(shí)現(xiàn),如何轉(zhuǎn)向asic實(shí)現(xiàn)?我們正在使用ieee_proposed。這項(xiàng)技術(shù)具體嗎?

2020-03-19 09:28:49

cogoask講解fpga和ASIC是什么意思FPGA入門知識(shí),什么是FPGA?FPGA是英文Field Programmable Gate Array的縮寫,即現(xiàn)場(chǎng)可編程門陣列,它是在PAL

2012-02-27 17:46:03

本公司招FPGA,CPLD,ASIC等相關(guān)兼職講師,短期技術(shù)培訓(xùn),要求有實(shí)際項(xiàng)目經(jīng)驗(yàn),兩年以上項(xiàng)目經(jīng)歷,表達(dá)力強(qiáng),有親和力,日薪千可日結(jié) ,可只在北京,周末。有意者請(qǐng)聯(lián)系QQ:***soft-xiang@foxmail.com簡(jiǎn)歷主題請(qǐng)寫: 課程名+學(xué)歷+性別+姓名+年齡+聯(lián)系方式

2012-12-03 17:18:45

[導(dǎo)讀]什么是FPGA,單片機(jī),DSP,ASIC?你真的知道嗎?ASIC原本就是專門為某一項(xiàng)功能開(kāi)發(fā)的專用集成芯片,比如你看攝像頭里面的芯片,小小的一片,集成度很低,成本很低,可是夠用了。一個(gè)山寨

2021-07-16 08:13:27

問(wèn)題,畢竟ASIC設(shè)計(jì)中可以自由配置scratchpad的大小。 綜上所述,FPGA和 ASIC在面向AI的專用設(shè)計(jì)中,雖然表面都是寫RTL,但是在具體架構(gòu)和思想上已經(jīng)有了較大的差異。FPGA

2023-03-28 11:14:04

。

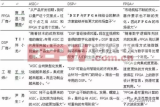

用戶使用FPGA時(shí),可以通過(guò)硬件描述語(yǔ)言(Verilog或VHDL),完成的電路設(shè)計(jì),然后對(duì)FPGA進(jìn)行“編程”(燒寫),將設(shè)計(jì)加載到FPGA上,實(shí)現(xiàn)對(duì)應(yīng)的功能。

加電時(shí),FPGA將EPROM

2024-01-23 19:08:55

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載2: FPGA、ASIC和ASSP特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD FPGA

2017-09-21 22:00:39

我的設(shè)計(jì)完全在Verilog中,并且已經(jīng)使用Spartan FPGA進(jìn)行了測(cè)試。我將源代碼提供給ASIC工廠,以實(shí)現(xiàn)作為ASIC使用他們(我認(rèn)為)的概要工具。我的問(wèn)題是,有沒(méi)有辦法使用任何

2019-07-25 13:44:31

喜我知道如何使用verilog為FPGA制作通用字節(jié)寫,字寫存儲(chǔ)器模型。但有沒(méi)有辦法制作一點(diǎn)寫內(nèi)存模型?我在網(wǎng)上看了很多但找不到一個(gè)。而我所做的存儲(chǔ)器模型最終會(huì)在讀寫時(shí)產(chǎn)生幾個(gè)延遲周期(因?yàn)槲?b class="flag-6" style="color: red">寫特性

2019-04-16 10:48:55

ASIC驗(yàn)證能夠采用的主要技術(shù)是什么?如何利用現(xiàn)成FPGA開(kāi)發(fā)板進(jìn)行ASIC原型開(kāi)發(fā)?

2021-05-08 07:51:04

到FPGA或ASIC系統(tǒng)的開(kāi)發(fā)時(shí)間。它包含了一個(gè)簡(jiǎn)單的"從FIFO"接口,使得和FPGA系統(tǒng)互聯(lián)很簡(jiǎn)單。從FIFO接口功能具備從讀和從寫信號(hào),可以讀或寫***到FX2LP 4 K

2012-11-22 16:11:20

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個(gè)單獨(dú)的奇偶校驗(yàn)寫使能位,但在FPGA RAM中沒(méi)有單獨(dú)的Pariaty寫使能位。 如何實(shí)現(xiàn)ASIC RAM奇偶校驗(yàn)寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

(70)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)21.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)25)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 06:29:31

熟練掌握Verilog,FPGA已經(jīng)入門,求推薦易懂的ASIC入門書,小弟感激不盡啊

2012-10-25 13:25:55

(76)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)31.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)35)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2022-02-23 07:33:53

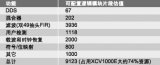

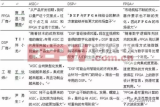

ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。

2019-09-02 07:58:00

ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。從可編程性、集成度、開(kāi)發(fā)周期、性能和功率五個(gè)方面探究,你會(huì)發(fā)現(xiàn)軟件無(wú)線電設(shè)計(jì)中選擇ASIC、FPGA和DSP時(shí)需要考慮哪些因素?

2019-08-16 07:51:25

在過(guò)去10年間,全世界的設(shè)計(jì)人員都討論過(guò)使用ASIC或者FPGA來(lái)實(shí)現(xiàn)數(shù)字電子設(shè)計(jì)的好處。通常這些討論將完全定制IC的性能優(yōu)勢(shì)和低功耗與FPGA的靈活性和低NRE成本進(jìn)行比較。設(shè)計(jì)隊(duì)伍應(yīng)當(dāng)在ASIC

2019-07-15 07:00:39

采用 Verilog HDL 語(yǔ)言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 FPGA是ASIC設(shè)計(jì)者的一道普通難題摘要:隨著開(kāi)發(fā) ASIC 與 SOC 的掩膜費(fèi)用、復(fù)雜度和工具成本的上升,今天很多設(shè)計(jì)小組正在選用 FPGA 實(shí)現(xiàn)自己的產(chǎn)品設(shè)計(jì)。但是,在設(shè)計(jì)者跨

2010-06-18 16:21:42 10

10 ASIC和FPGA設(shè)計(jì)中的多點(diǎn)綜合技術(shù)

盡管在技術(shù)發(fā)展的每一個(gè)時(shí)刻做出精確的預(yù)言是困難的,但ASIC和FPGA所集成的門數(shù)仍象數(shù)年前INTEL的Gordon Monre預(yù)言的那樣平均每18個(gè)月增加一倍.

2010-06-19 10:05:09 11

11 面向ASIC和FPGA設(shè)計(jì)的多點(diǎn)綜合技術(shù)

隨著設(shè)計(jì)復(fù)雜性增加,傳統(tǒng)的綜合方法面臨越來(lái)越大的挑戰(zhàn)。為此,Synplicity公司開(kāi)發(fā)了同時(shí)適用于FPGA或 ASIC設(shè)計(jì)的多點(diǎn)綜合技術(shù),它

2009-12-26 14:34:33 563

563 FPGA原型驗(yàn)證和其他驗(yàn)證方法是不同的,任何一種其他驗(yàn)證方法都是ASIC驗(yàn)證中的一個(gè)環(huán)節(jié),而FPGA驗(yàn)證卻是一個(gè)過(guò)程。由于FPGA與ASIC在結(jié)構(gòu)、性能上各不相同,ASIC是基于標(biāo)準(zhǔn)單元庫(kù),FPGA用的

2010-09-10 17:22:26 989

989 對(duì)ASIC設(shè)計(jì)進(jìn)行FPGA原型驗(yàn)證時(shí),由于物理結(jié)構(gòu)不同,ASIC的代碼必須進(jìn)行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計(jì)中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計(jì)流程中

2011-03-25 15:16:20 108

108 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 我經(jīng)常收到關(guān)于各類設(shè)備之間的差異的問(wèn)題,諸如ASIC、ASSP、SoC和FPGA之間的區(qū)別問(wèn)題。例如是SoC是ASIC嗎?或ASIC是SoC嗎?ASIC和ASSP之間的區(qū)別是什么?以及高端FPGA應(yīng)該歸類為SoC嗎?

2014-07-17 09:42:39 42262

42262 數(shù)字電路中的FPGA和verilog教程,好東西,喜歡的朋友可以下載來(lái)學(xué)習(xí)。

2016-01-18 17:44:30 42

42 基于EP1C3的FPGA程序之seg7_verilog

2016-01-20 15:22:50 11

11 FPGA_Verilog學(xué)習(xí)資料 part1。

2016-03-14 14:28:54 47

47 FPGA_Verilog學(xué)習(xí)資料 part2。

2016-03-14 14:27:50 36

36 FPGA_Verilog學(xué)習(xí)資料 part3。

2016-03-14 14:24:16 29

29 FPGA_Verilog學(xué)習(xí)資料,part4。

2016-03-14 14:23:30 9

9 (ebook) Chu - FPGA Prototyping Using Verilog Examples

2016-06-03 16:16:53 14

14 Xilinx FPGA工程例子源碼:在FPGACPLD中實(shí)現(xiàn)AD或DA的文章(英文Verilog)

2016-06-07 15:07:45 17

17 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 FPGA原型驗(yàn)證和其他驗(yàn)證方法是不同的,任何一種其他驗(yàn)證方法都是ASIC驗(yàn)證中的一個(gè)環(huán)節(jié),而FPGA驗(yàn)證卻是一個(gè)過(guò)程。

2017-02-11 12:46:11 2975

2975 基于FPGA Verilog-HDL語(yǔ)言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

35 FPGA verilog 相關(guān)設(shè)計(jì)實(shí)踐

2017-09-06 11:19:34 32

32 ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。本文從可編程性、集成度、開(kāi)發(fā)周期、性能和功率五個(gè)方面論述了選擇ASIC、FPGA

2017-10-24 11:51:00 0

0 ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。本文從可編程性、集成度、開(kāi)發(fā)周期、性能和功率五個(gè)方面論述了選擇ASIC、FPGA

2017-11-21 20:58:01 1300

1300

ASIC 和 FPGA 具有不同的價(jià)值主張,選擇其中之一之前,一定要對(duì)其進(jìn)行仔細(xì)評(píng)估。2種技術(shù)的比較信息非常豐富。這里介紹了ASIC和FPGA的優(yōu)勢(shì)與劣勢(shì)。

2017-11-25 09:24:44 4374

4374 不過(guò)在聯(lián)發(fā)科副總經(jīng)理暨智能設(shè)備事業(yè)群總經(jīng)理游人杰看來(lái),雖然CPU、GPU等通用型芯片以及FPGA可以適應(yīng)相對(duì)更多種的算法,但是特定算法下ASIC的性能和效能要更高。另外,雖然FPGA的便定制特性比ASIC芯片更加靈活,但部署FPGA所付出的成本也要比ASIC更高。

2018-05-04 15:39:03 251868

251868

隨著處理器被添加到傳統(tǒng)FPGA中,可編程性被添加到ASIC中,FPGA和ASIC的分界線日益模糊。

2018-07-23 17:07:00 805

805 有人認(rèn)為,除了人才短缺、開(kāi)發(fā)難度較大,相比未來(lái)的批量化量產(chǎn)的ASIC芯片,FPGA在成本、性能、功耗方面仍有很多不足。這是否意味著,在ASIC大爆發(fā)之際,FPGA將淪為其“過(guò)渡”品的命運(yùn)?

2018-08-29 17:46:00 936

936 有人認(rèn)為,除了人才短缺、開(kāi)發(fā)難度較大,相比未來(lái)的批量化量產(chǎn)的ASIC芯片,FPGA在成本、性能、功耗方面仍有很多不足。這是否意味著,在ASIC大爆發(fā)之際,FPGA將淪為其“過(guò)渡”品的命運(yùn)?

2018-09-01 08:25:26 6826

6826 在相當(dāng)長(zhǎng)的一段時(shí)間內(nèi),FPGA、ASIC、DSP三者不同的技術(shù)特征造就了它們不同的應(yīng)用領(lǐng)域,DSP在數(shù)字信號(hào)方面是絕對(duì)的霸主,ASIC是專業(yè)定制領(lǐng)域的牛人,而FPGA由于其價(jià)格高、功耗大,主要

2018-11-29 14:37:02 647

647

FPGA是可編程ASIC。 ASIC:專用集成電路,它是面向?qū)iT用途的電路,專門為一個(gè)用戶設(shè)計(jì)和制造的。

2018-12-15 09:58:46 5195

5195 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之學(xué)習(xí)FPGA選擇verilog還是vhdl詳細(xì)資料說(shuō)明。

2019-03-22 14:00:07 24

24 ASIC芯片一旦流片功能就無(wú)法改變,基本專片專用。而FPGA可配置特性就可以應(yīng)用在功能會(huì)改變的場(chǎng)合,例如,原型驗(yàn)證,ASIC設(shè)計(jì)過(guò)程中會(huì)使用到FPGA來(lái)進(jìn)行原型驗(yàn)證;功能升級(jí),在產(chǎn)品中采用FPGA實(shí)現(xiàn)一些業(yè)內(nèi)暫時(shí)還沒(méi)成熟的解決方案,可以在后續(xù)功能變動(dòng)時(shí)方便升級(jí)。

2019-08-25 10:40:01 10934

10934

隨著處理器被添加到傳統(tǒng)FPGA中,可編程性被添加到ASIC中,FPGA和ASIC的分界線日益模糊。FPGA變得比之前更加流行了。

2019-10-18 15:01:51 2550

2550 FPGA vs. ASIC 你看好誰(shuí)?

2020-01-15 16:10:22 4104

4104 電子技術(shù)行業(yè)里面的攻城師們應(yīng)該對(duì)ASIC、FPGA和單片機(jī)這些名字都不陌生,但我相信并不是所有人都清楚ASIC和FPGA之間的區(qū)別和關(guān)系,下面我們分幾個(gè)方面去理清一下他們之間的瓜葛糾紛吧!

2020-06-04 11:36:11 5697

5697 ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。本文從可編程性、集成度、開(kāi)發(fā)周期、性能和功率五個(gè)方面論述了選擇ASIC、FPGA

2020-08-28 10:48:00 0

0 FPGA 要取代 ASIC 了,這是 FPGA 廠商喊了十多年的口號(hào)。可是,FPGA 地盤占了不少,ASIC 也依舊玩得愉快。這兩位仁兄到底有啥不一樣呢?

2020-12-25 11:56:57 9

9 FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)圖文稿(ltspice 放置電源)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)圖文稿資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 12:17:02 10

10 FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)(單片機(jī)電源維修)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)修訂稿(空調(diào)電源芯片)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)修訂稿資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 13:13:56 10

10 FPGA_ASIC-MAC在FPGA中的高效實(shí)現(xiàn)(理士電源技術(shù)有限公司)-該文檔為FPGA_ASIC-MAC在FPGA中的高效實(shí)現(xiàn)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-08-04 19:03:13 8

8 FPGA CPLD中的Verilog設(shè)計(jì)小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計(jì)小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 的完整 Verilog 代碼 。 在這個(gè)FPGA Verilog項(xiàng)目中,一些簡(jiǎn)單的處理操作都是在Verilog中實(shí)現(xiàn)的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 15:50:21 5111

5111 (77)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)31.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)35)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2021-12-29 19:42:39 0

0 將ASIC設(shè)計(jì)移植到FPGA芯片中,對(duì)于大部分設(shè)計(jì)團(tuán)隊(duì)來(lái)講都是巨大的挑戰(zhàn)。主要體現(xiàn)在:ASIC的設(shè)計(jì)一般都非常大,往往需要做多FPGA芯片劃分;需要支持足夠的處理性能;需要保證其功能的正確性;需要保證移植前后的功能具有等價(jià)性。

2022-04-14 15:01:08 1780

1780 需要門級(jí)驗(yàn)證:FPGA 和 ASIC 一樣需要設(shè)計(jì)級(jí)驗(yàn)證。但是,FPGA 在門級(jí)不是細(xì)粒度的,因此它們不需要門級(jí)驗(yàn)證。您將每個(gè)門都放置在 ASIC 設(shè)計(jì)中,因此您需要驗(yàn)證每個(gè)門。

2022-06-20 16:13:05 2184

2184

FPGA vs ASIC 相同點(diǎn) 都設(shè)計(jì)使用硬件描述語(yǔ)言(HDL),如VHDL或Verilog。但ASIC相比于FPGA開(kāi)發(fā)上,代碼風(fēng)格更為隨意,因?yàn)?b class="flag-6" style="color: red">FPGA是先有電路,后有代碼,ASIC是先有代碼

2022-11-28 10:30:13 771

771 FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號(hào)。可是,FPGA地盤占了不少,ASIC也依舊玩得愉快。那么,這兩位仁兄到底有啥不一樣呢?

2023-03-31 14:41:41 1138

1138

FPGA和ASIC都是數(shù)字電路的實(shí)現(xiàn)方式,但它們有不同的優(yōu)缺點(diǎn)和應(yīng)用場(chǎng)景。本文將以通俗易懂的方式解釋FPGA和ASIC的概念、基本組成、及其應(yīng)用場(chǎng)景。

2023-08-14 16:37:35 1152

1152 FPGA和ASIC作為數(shù)字電路的常見(jiàn)實(shí)現(xiàn)方式,其聯(lián)系和區(qū)別備受關(guān)注。本文將從FPGA和ASIC的基本概念入手,深入研究它們的區(qū)別與聯(lián)系,以幫助讀者更好地理解兩者的應(yīng)用場(chǎng)景和選擇方法。

2023-08-14 16:38:51 1583

1583 FPGA和ASIC是數(shù)字電路中常見(jiàn)的實(shí)現(xiàn)方式,因此人們經(jīng)常會(huì)想要了解哪種芯片在未來(lái)的發(fā)展中更具有前途。然而,這取決于具體的應(yīng)用場(chǎng)景和需求。在本文中,我們將探討FPGA和ASIC的優(yōu)劣勢(shì),并分析哪種芯片在特定的應(yīng)用場(chǎng)景中更具有優(yōu)勢(shì)。

2023-08-14 16:40:20 1028

1028

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論