美國賽靈思(Xilinx)2012年4月5日使用28nm工藝制造的FPGA “Virtex-7 X690T”演示了有線通信系統(背板)。該FPGA配備有80個以最大13.1Gbit/秒的速度工作的高速串行收發器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848 最大的收發器數量。 圖1 Xilinx的7系列FPGA隨著集成度的提高,其高速串行收發器不再獨占一個單獨的參考時鐘,而是以Quad來對串行高速收發器進行分組,四個串行高速收發器和一個COMMOM(QPLL)組成一個Quad,每一個串行高速收發器稱為一個Channel,以XC7K325T為例,GTX在F

2020-11-20 12:08:15 17712

17712

輸入輸出端口 從Implemented Design中可以看到FPGA中資源大致分布如下。中間藍色是CLB可編程邏輯塊、DSP或BRAM,兩側的彩色矩形塊是I/O接口和收發器,劃分的方塊是不同的時鐘域 Configurable Logic Block (CLB)可編程邏

2022-12-27 15:54:52 1788

1788 。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

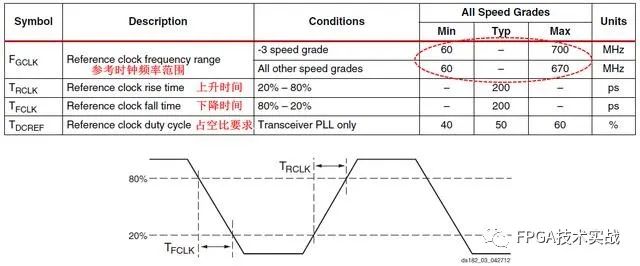

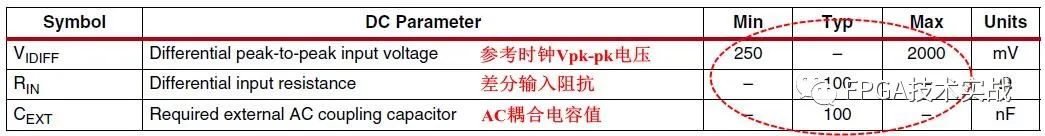

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1956

1956

你好我嘗試使用xilinx 7系列收發器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收發器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

本帖最后由 QQ3511836582 于 2017-3-29 15:42 編輯

疑問描述測試表明,Spartan-6 FPGA的GTP收發器有可能受到臨近bank中用戶管腳的干擾。因此,賽靈思

2017-03-21 14:34:27

FPGA GTP收發器設計指導疑問描述測試表明,Spartan-6 FPGA的GTP收發器有可能受到臨近bank中用戶管腳的干擾。因此,賽靈思針對bank0和bank2中管腳的使用提出了一些新的建議

2016-08-25 09:46:38

FPGA的任意一個管腳都可以作為時鐘輸入端口,但是FPGA專門設計了全局時鐘,全局時鐘總線是一條專用總線,到達片內各部分觸發器的時間最短,所以用全局時鐘芯片工作最可靠,但是如果你設計的時候時鐘太多

2012-02-29 09:46:00

數據訪問狀態的功能簡單地說就是中斷監測和數據收發。每次系統復位后 FPGA 會自動配置 PDIUSBD12 器件,配置完成之后設備收發器模塊會處于空閑狀態(TS_IDLE)。PDIUSBD12 器件

2018-11-27 09:20:08

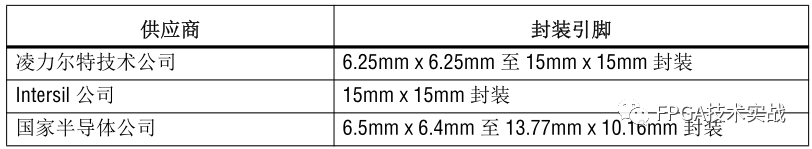

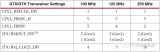

FPGA高速收發器設計原則高速FPGA設計收發器選擇需要考慮的因素

2021-04-09 06:53:02

高速收發器(SERDES)的運用范圍十分廣泛,包括通訊、計算機、工業和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數據的系統。但普通高速收發器的并行總線設計已無法滿足現在的要求。將收發器整合在FPGA中,成為解決這一問題的選擇辦法。FPGA高速收發器設計時,我們需要注意哪些事項呢?

2019-08-07 06:26:42

_XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)電壓主要有VCCINT(內核電壓),VCCRAM(RAM塊電壓),VCCAUX(輔助電壓),VCCO(IO電壓)以及高速串行收發器GTX Transceiver的供電電壓。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2021-12-28 06:38:44

我正在研究使用高速收發器接收部分的定制電路板。所有四個接收器的參考時鐘相同,為125 MHz。我從焦平面陣列(FPA)接收數據并使用8 / 10b編碼。我可以讓FPA重復顯示空白行(字符1FFD

2020-05-05 11:39:41

所需的關鍵信息:管腳編號、管腳名稱、管腳DDR內存分組、管腳BANK編號、輔助組(VCCAUX)、超級邏輯域(SLR)、I/O管腳類型(配置、HR、HP、收發器管腳等)以及與器件Pin-to-Pin兼容相關的NC管腳信息。圖4、Pinout文件內容舉例

2021-05-28 09:23:25

所需的關鍵信息:管腳編號、管腳名稱、管腳DDR內存分組、管腳BANK編號、輔助組(VCCAUX)、超級邏輯域(SLR)、I/O管腳類型(配置、HR、HP、收發器管腳等)以及與器件Pin-to-Pin兼容相關的NC管腳信息。圖4、Pinout文件內容舉例

2021-07-08 08:00:00

描述 PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2022-09-21 07:56:06

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2022-09-27 06:46:35

CAN收發器是連接CAN控制系統與CAN總線網絡的橋梁,當選型CAN收發器時應該注意哪些參數?本文將帶大家深入的了解收發器的每項參數與其在實際應用中的意義。

2020-12-18 07:16:27

在CAN通信中,收發器起到了十分相當特別的作用。目前市面的收發器型號也是不計其數,本文則是根據收發器的發展,簡單介紹幾款收發器的特點。很多年前,NXP的CAN收發器幾乎在每一個CAN節點上都看的到,當時最常見的型號就是PCA82C250。

2019-09-03 06:04:44

我需要能夠使用SFP收發器。我想使用收發器向導,但我不知道選擇哪些選項。我不確定我的轉賬率是多少。我知道我需要使用的時鐘大約是600MHz。我還需要能夠從此收發器恢復時鐘。收發器是否有輸出時鐘?謝謝你的幫助。

2020-04-07 14:39:32

描述PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2022-09-26 06:32:49

`描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2015-05-11 10:30:22

`描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2015-05-11 10:27:03

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2018-09-10 09:02:14

挑戰。這些收發器可為模擬RF信號鏈提供數字接口,允許輕松集成到ASIC或FPGA,進行基帶處理。基帶處理器(BBP)允許在終端應用和收發器設備之間的數字域中處理用戶數據。

2019-09-19 06:20:59

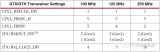

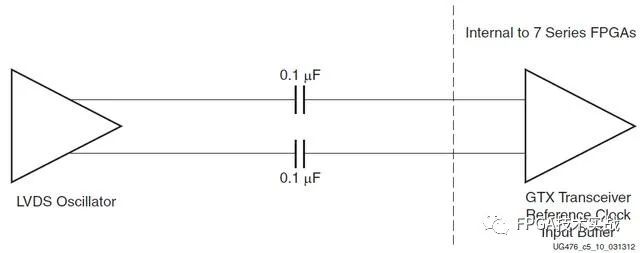

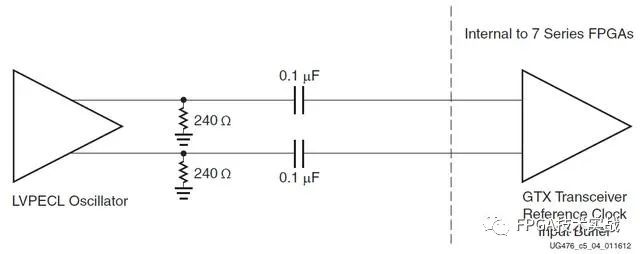

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述GTX/GTH收發器時鐘

2021-11-11 07:42:37

嗨,我有2個靜態配置的GTX收發器用于HD-SDI操作。我可以使用一個收發器的Txoutclk為兩個收發器配備Txusrclock嗎?通過這種方式,我可以只用1個Txusrclock為FPGA邏輯

2020-08-19 07:43:50

使用高級校準技術驗證收發器FPGA

2019-09-19 09:05:14

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發器。請問我能直接把FPGA的引腳直接連在CAN收發器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:25:39

一、概述

IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問

2023-06-21 11:23:12

Xilinx FPGA上的JESD204B發送器和接收器框圖。發送器/接收器通道實現加擾和鏈路層;8B/10B編碼器/解碼器和物理層在GTP/GTX/GTHGbit 收發器中實現。圖4. 使用Xilinx

2018-10-16 06:02:44

基于FPGA的通用異步收發器設計

2012-08-18 00:03:20

大家好,我正著手開發我的第一個真正的FPGA PCB。沒有更簡單的開發板:)我正在試圖弄清楚如何使用帶有FPGA的1000BASE-T 1.25 GBd小型可插拔收發器。我告訴我需要終止FPGA上

2019-01-22 10:22:55

光纖收發器的優勢如何區分單纖收發器與雙纖收發器?

2021-01-14 07:26:53

這是我的第一個涉及FPGA的項目,我正在尋找更有經驗的用戶的好建議,指出我正確的方向。我想實現一個通過以太網端口連接到源的2.4GHz,15Mbps獨立通信收發器。我一直在檢查SDR系統的實現,但

2019-08-19 10:17:23

,似乎FPGA架構I將獲得32位側并行總線,并且我假設時鐘與其頻率匹配(5G / 32)。我想將總線寬度從32位改為50位(這很容易)。但是,我要求更寬總線的新時鐘是從收發器輸出的總線頻率的32/50。是否可以在FPGA內部生成此時鐘,并將此時鐘的副本提供給IO引腳。謝謝

2020-05-11 09:06:46

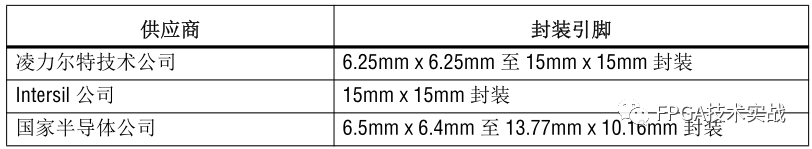

選擇合適的千兆位收發器(GT)是通信和實時處理領域尤其需要重點考慮的設計事項,但特定的市場領域可能會存在太多的標準、協議或使用模型。有時針對某一種應用就會涉及到好幾種標準,為了選擇最適合的千兆位收發器,必須對各種協議的最新發展情況了如指掌。

2019-10-31 06:57:54

引入多個收發器來提升帶寬,將是其設計的一個重要組成部分。無論是 SmartNIC、還是密集的服務器互聯拓補,都依賴于 FPGA 開展初始部署和調整,然后才會轉向 ASIC 。長期以來,Xilinx

2020-09-02 18:55:07

描述PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2018-08-31 08:59:25

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平輸出28.5Gbps的信號要用什么電平?

2014-11-10 09:12:51

描述PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流和電壓

2018-08-10 09:36:45

如何把故障保護偏置應用于閑置總線?老式收發器與新式收發器的區別在哪里?

2021-05-24 07:03:57

你好我試圖在KC705板上使用收發器來生成比特流。我正在使用Vivado 2012.3和7系列FPGA收發器向導v2.3。我之前使用過具有不同傳輸者名稱的IBERT核心。IBERT收發器名稱類似于

2020-07-28 10:29:31

我是FPGA設計的新手,但我已經閱讀了數據表,應用筆記......幾周以來我仍然無法使用收發器。但絕望之后,我只是按照這個示例/教程:http://china.xilinx.com/support

2020-07-24 14:35:18

請問“窄帶收發器”和一般的收發器(比如CC1101)有什么區別

2018-06-21 07:54:27

大家好,我想在我的測試板上使用FPGA中唯一的時鐘。(FPGA是zynq ultrascale +,時鐘來自quad228(GTH收發器)的clk0。)我嘗試了各種各樣的東西,比如

2020-04-30 08:16:16

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發器。請問我能直接把FPGA的引腳直接連在CAN收發器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:05:37

選擇合適的FPGA千兆位收發器為什么至關重要?

2021-04-13 06:58:27

`有誰知道這個收發器哪里能買么,有25mm×15mm規格的么`

2013-12-13 11:44:18

FPGA高速收發器設計原則

高速收發器(SERDES)的運用范圍十分廣泛, 包括通訊、計算機、工業和儲存,以及必須在芯片與

2009-04-07 22:26:14 986

986 基于FPGA的高速時鐘數據恢復電路的實現

時鐘數據恢復電路是高速收發器的核心模塊,而高速收發器是通信系統中的關鍵部分。隨著光纖在通信中的應用,信道可以承載

2009-10-25 10:29:45 3626

3626

面向收發器(SERDES) FPGA 的PDN 設計對電源有嚴格的要求,需要干凈的電壓源。雖然低功耗應用中通常采用低泄漏(LDO) 線性穩壓器,但這一方法必須仔細的隔離電壓源。電路板設計人員在這

2011-05-11 18:29:41 57

57 DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有

2017-02-08 09:14:00 671

671 PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。 它利用一個 PMBus 接口來實現電流和電壓

2017-02-08 09:22:11 419

419 PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2017-02-08 15:59:50 789

789 了解如何在您的 ?UltraScale? FPGA? 設計中部署串行收發器。了解并利用串行收發器模塊的特性,如 ?8B/10B? 和 ?64B/66B? 編碼、通道綁定、時鐘校正和逗點檢測。其它專題

2017-02-09 08:04:41 327

327 賽靈思(Xilinx)公司FPGA器件的高速串行收發器類別如下

2017-02-11 11:11:30 5958

5958

在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

Xilinx公司業界首款28 nm FPGA Kintex-7 10Gbps 收發器性能演示。

2018-06-01 15:50:00 3960

3960 設計人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴接收機均衡來補償信號失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發器 和 Altera Stratix V GX 收發器的均衡能力。

2018-05-23 15:47:00 3974

3974

每一個收發器擁有一個獨立的發送端,發送端有PMA(Physical Media Attachment,物理媒介適配層)和PCS(Physical Coding Sublayer,物理編碼子層)組成

2018-06-20 13:48:00 2709

2709

首次演示新型Xilinx 7系列GTH收發器,通過背板以13.1 Gb / s的速度運行。

2019-01-03 13:25:38 4048

4048 該演示展示了Xilinx SERDES開發的最新成果,首次公開展示了Xilinx 58Gb / s PAM4收發器。

2018-11-29 06:21:00 2048

2048 該視頻演示了具有32.75G背板功能的Virtex?UltraScale+?FPGA,功率優化的收發器。

該收發器具有同類最佳的發送抖動和第三代客戶驗證的自適應接收器均衡功能......

2018-11-28 06:39:00 2161

2161 Xilinx推出全球首款28nm FPGA,展示10Gbps SERDES功能

Xilinx在Kintex-7 K325T FPGA上展示了10Gbps收發器,這是有史以來第一款28nm FPGA。

2018-11-28 06:30:00 3785

3785 Xilinx GTX(12.5 Gb / s)收發器與SFP +和10G背板一起運行。

2018-11-30 06:36:00 9807

9807 spartan-6 FPGA GTP收發器。在本文檔中,gtp_dual是gtpa1_dual圖塊的同義詞。

?Dual是兩個GTP收發器的集群或集合,共享兩個差分參考時鐘針對和模擬電源針。

2019-02-15 14:42:47 27

27 本章介紹virtex-6 FPGA GTH收發器向導,并提供相關信息,包括其他資源、技術支持和向xilinx提交反饋。向導自動執行創建HDL包裝器的任務,以配置virtex-6設備中的高速串行GTH收發器。

2019-02-20 09:35:45 4

4 7系列FPGA GTP收發器的可定制Logicore?IP Chipscope?Pro集成誤碼率測試(IBert)內核用于評估和監控GTP收發器。該核心包括在FPGA邏輯中實現的模式生成器和校驗

2019-02-20 14:30:00 25

25 和AFCT-701SDZ 10 Gbs以太網SFP +收發器產品與具有自適應DFE的XilinxVirtex?-6FPGA 11.18 Gbps收發器的高速互操作性。 Xilinx產品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問和GTX收發器的動態重新配置端口屬性,還包括通信邏輯,以允許設計在運行時通過JTAG進行訪問。

2021-05-02 22:10:00 5587

5587

引言:本文我們介紹GTX/GTH收發器時鐘架構應用,該文內容對進行PCIe和XAUI開發的FPGA邏輯設計人員具有實際參考價值,具體介紹: PCIe參考時鐘設計 XAUI參考時鐘設計 1.PCIe

2021-03-29 14:53:47 5441

5441

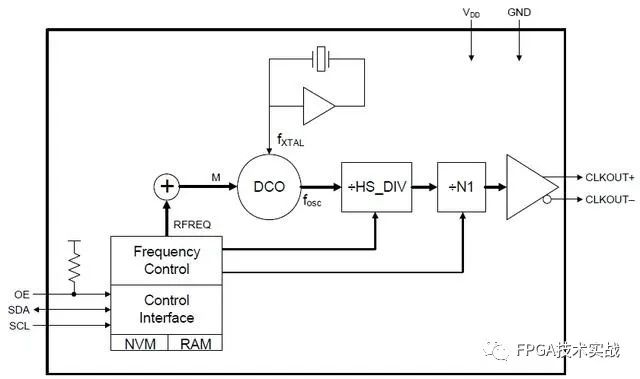

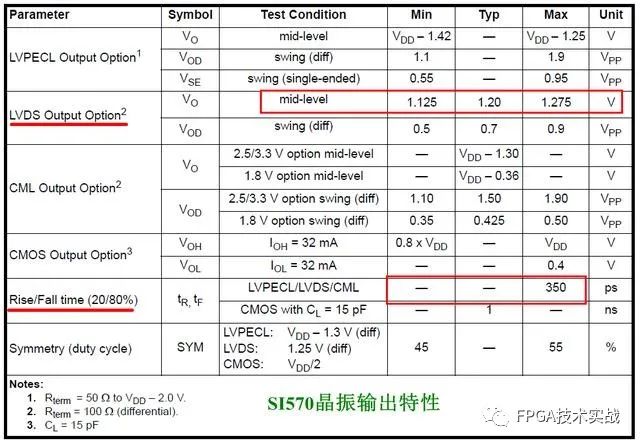

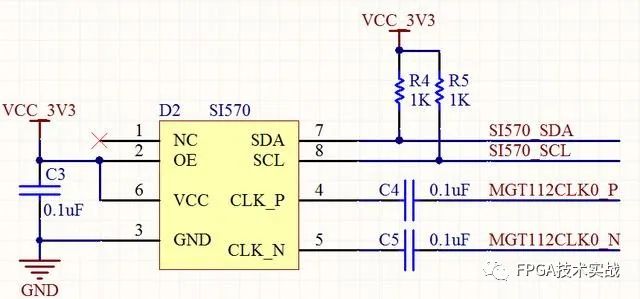

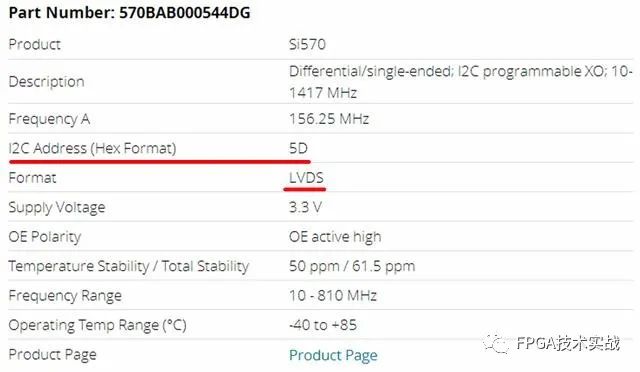

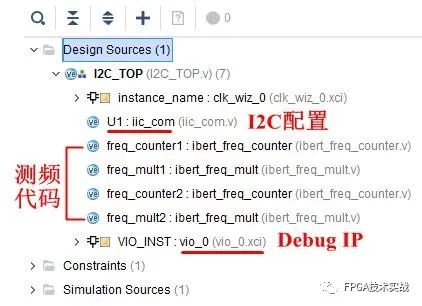

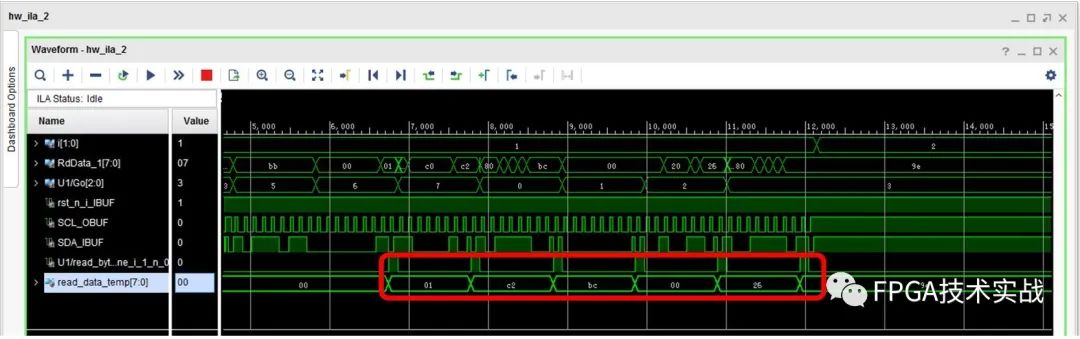

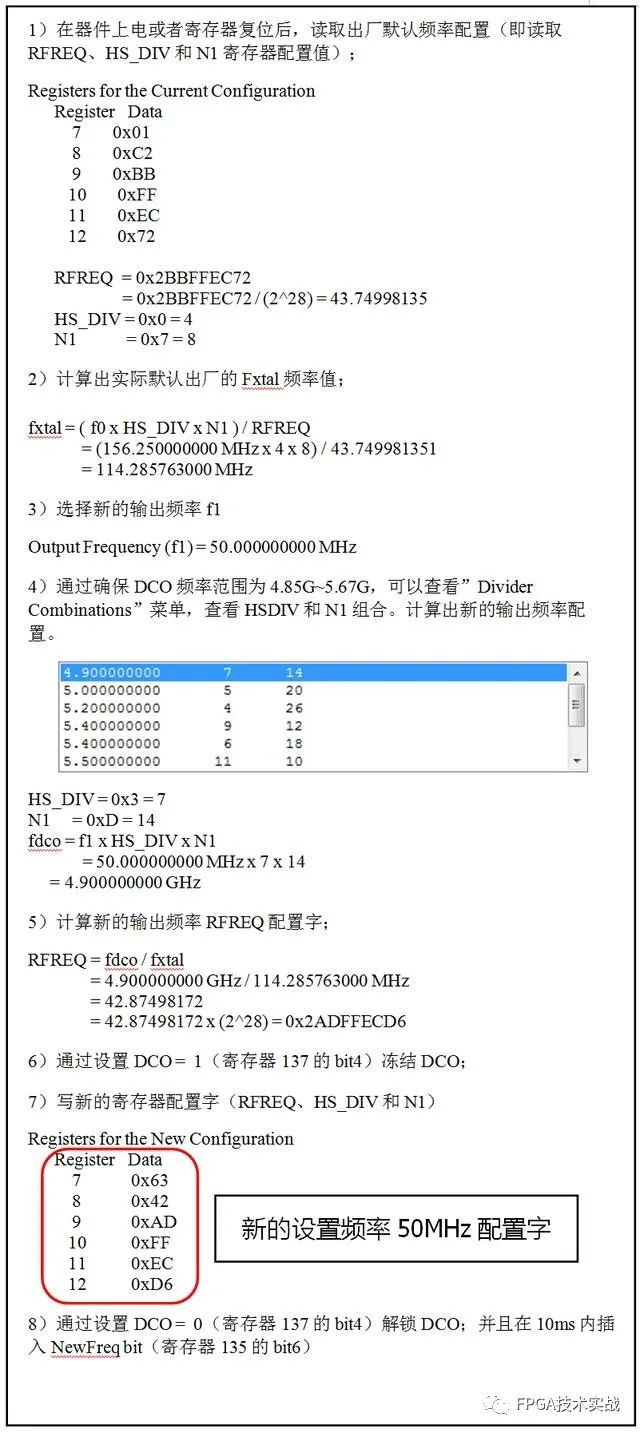

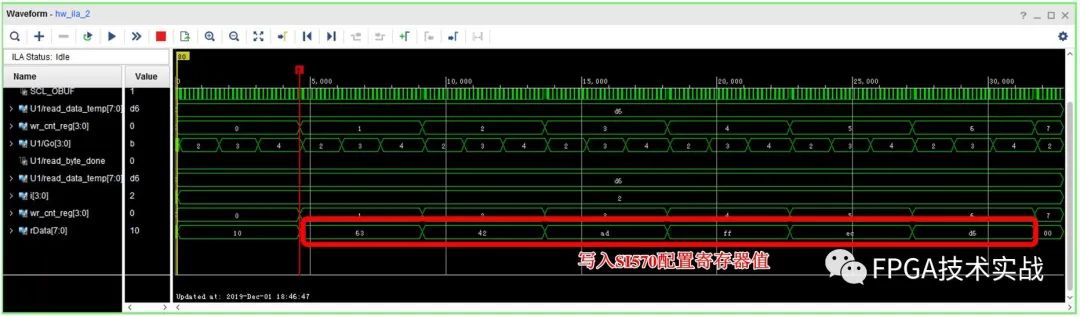

晶振是數字電路設計中非常重要的器件,時鐘的相位噪聲、頻率穩定性等特性對產品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發器輸入參考時鐘的硬件設計及FPGA軟件設計給出設計案例,供大家參考。

2021-04-07 12:00:44 3914

3914

面向收發器 (SERDES) FPGA 的PDN設計對電源有嚴格的要求,需要干凈的電壓源。雖然低功耗應用中通常采用低泄漏 (LDO) 線性穩壓器,但這一方法必須仔細的隔離電壓源。

2021-05-02 09:58:00 1527

1527

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述 GTX/GTH收發器時鐘

2021-11-06 19:51:00 35

35 xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH、GTZ四種串行高速收發器,可以支持多種協議如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

電子發燒友App

電子發燒友App

評論