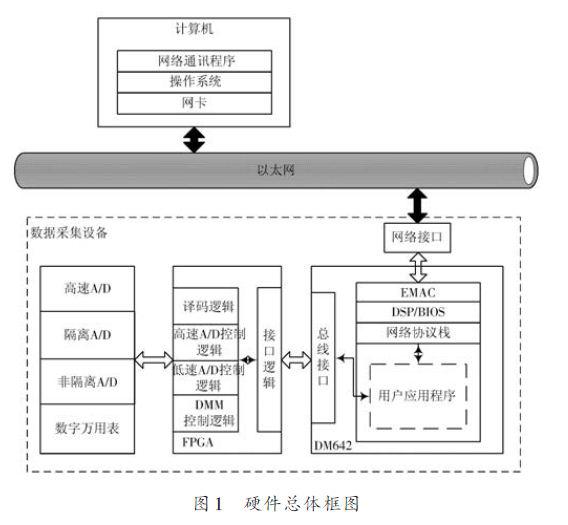

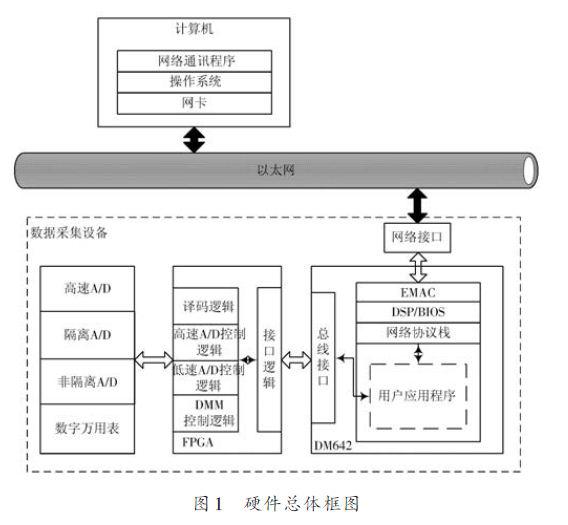

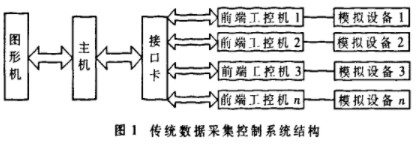

數據采集設備是測試系統中不可缺少的一部分,數據采集需要針對不同類型的需求,需要有高速A/D、低速A/D、數字多用表等功能,傳統數據采集設備是用一種儀器進行一類測試,通過多種儀器組合實現一組完整測試,這種由多種儀器堆疊起來的數據采集系統具有體積和重量較大、成本較高、維護困難等諸多問題。

2019-01-10 09:13:00 4117

4117

,介紹了altera的可編程器件的高級設計工具與系統級設計技巧。十天學會CPLD/FPGA 系統設計全集:這是一部針對初學可編程邏輯器件者的教程,教程全部十講,講座從基本的預備知識開始講解,非常詳細的講解

2020-05-14 14:50:30

vhdl語言實現16位數據通信,求助!

2014-03-07 14:02:47

系統的設計提出兩個方面的要求:一方面,要求接口簡單靈活且有較高的數據傳輸率;另一方面,由于數據量通常都較大,要求主機能夠對數據做出快速反應,并及時分析和處理。實現數據采集與傳輸,可選擇如下3種方法

2020-01-07 07:00:00

他CPU系統之間的數據通信提到日程上,得到人們的急切關注。本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。整個設計采用模塊化的設計思想,可分為四個模塊:FPGA數據發送模塊,FPGA

2011-11-24 16:10:01

設計RISC微處理器需要遵循哪些原則?基于FPGA技術用VHDL語言實現的8位RISC微處理器

2021-04-13 06:11:51

,舉例說明了利用VHDL語言實現數字系統的過程。 整個數字電壓表的硬件結構如圖1所示。 工作時,系統按一定的速率采集輸入的模擬電壓,經ADC0804轉換為8位數字量,此8位數字量經FPGA處理

2012-10-26 15:46:00

請教大家怎么用VHDL語言實現減法運算?在FPGA設計時又該怎么操作呢?

2012-05-17 20:07:12

vhdl語言實例大全下載

2008-05-20 09:36:01

DSP28335+FPGA+AD7606的數據采集系統,DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設計的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數據采集系統,DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設計的過程中遇到

2016-07-18 17:13:01

`勇敢的芯伴你玩轉Altera FPGA連載4:Verilog與VHDL特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD Verilog

2017-09-26 21:07:34

面向用戶需求,根據系統的行為和功能要求,自上至下地逐層完成相應的描述、綜合、優化、仿真和驗證,直到生成器件。本文介紹了使用VHDL語言實現CPLD設計的方法,并以此方法在ALTERA公司的CPLD器件

2016-05-08 06:18:34

基于FPGA 的DSP 數據采集分析系統設計

2012-08-20 15:35:41

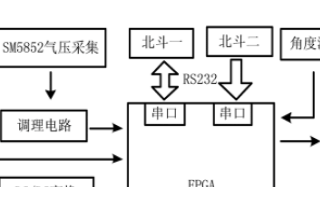

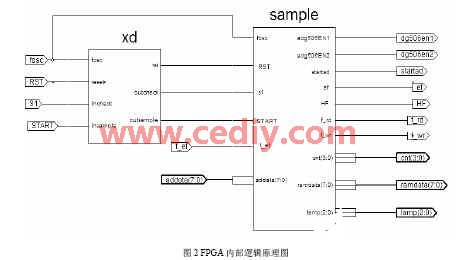

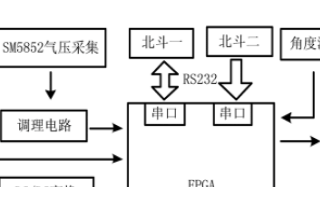

FPGA模塊為整個系統的核心控制部分,使用硬件描述語言Verilog HDL對FPGA進行程序設計,以實現系統的整體功能要求。2.1.2 數據采集模塊AD7609AD7609是一款18位、8通道、真差分

2018-08-09 14:28:00

24期摘 要:傳統的數據采集系統大都是由ARM+DSP實現的,雖然DSP的優勢在于數據處理,但是隨著FPGA技術的發展,很多FPGA已經可以取代DSP的作用了。尤其是在高速實時的數據采集領域,采集

2018-05-09 12:09:43

基于FPGA的數據采集系統IEE ... 介紹了數據采集系統中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設計,給出了系統硬件設計和FPGA邏輯設計,討論了IEEE1394總線

2012-08-11 15:43:47

新手一枚,本人畢設要做一個基于FPGA的GNSS數據采集系統。目前已經擬定開發方案,大致思路是這樣的:通過射頻前端獲取L1頻段的GNSS信號,經帶通采樣下變頻到中頻,把采樣后的信號送入FPGA進行

2015-04-28 09:56:02

設計高溫環境下(最高120°)基于FPGA的數據采集存儲系統,就是通過傳感器采集數據,通過FPGA來控制,把數據存儲到存儲芯片上,回頭可以通過接口讀取數據顯示在計算機上,求大師給我指導,我急需整個系統的protel原理圖,請各位幫忙,我將感激不盡。最好有附件畫出整個原理圖,謝謝!

2012-10-29 21:37:12

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

不知道有沒有大神做過:基于FPGA的圖像邊緣檢測系統設計,用VHDL語言實現

2018-05-10 00:22:07

目前,在數據采集系統的硬件設計方案中,有采用通用單片機和USB相結合的方案,也有采用DSP和USB相結合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數據采集系統對速度要求;后者雖然可以實現

2019-09-05 07:22:57

1. 計價器數據采集模塊。 2.Verilog和VHDL語言程序編寫正確,能夠通過編譯、綜合和下片。 3.使用Quartus II軟件仿真結果正確。 求大神解決私聊重謝!

2016-05-11 00:45:33

,FPGA邏輯電路控制A/D采集和FIFO緩存模塊,實現長時間不間斷的數據采集與數據轉換;同時系統具有豐富的外圍控制接口和通信接口,可以實現數據的存儲、顯示,完成RS485/RS232或高速以太網

2010-08-31 09:14:55

,一般情況下,速度指標是首要的,在滿足速度要求的前提下,盡可能實現面積優化。因此,本文結合在設計超聲探傷數據采集卡過程中的CPLD編程經驗,提出串行設計、防止不必要鎖存器的產生、使用狀態機簡化電路描述、資源共享,利用E2PROM芯片節省片內資源等方法對VHDL電路進行優化。

2019-06-18 07:45:03

),利用短消息傳輸來實現遠程數據采集系統的方案。全文由GPRS 業務的概述、遠程數據采集系統的功能設計、數據采集終端的硬件設計、軟件的設計四部分組成。介紹了系統的發展背景、單片機技術、GSM/GPRS

2009-12-08 09:57:10

摘要: 介紹了一種由PCI 9054 和EP1C6Q240C8 構成的高速數據采集系統, 詳細地敘述了系統設計原理與軟硬件的實現方法。該系統具有結構簡單、工作可靠、經濟實用等特點。關鍵詞:PCI

2010-09-22 08:51:09

本文介紹應用美國ALTERA公司的MAX+PLUSⅡ平臺,使用VHDL硬件描述語言實現的十六路彩燈控制系統。

2021-04-19 07:43:57

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

利用現場可編程門陣列(FPGA)和VHDL 語言實現了PCM碼的解調,這樣在不改變硬件電路的情況下,能夠適應PCM碼傳輸速率和幀結構變化,從而正確解調數據。

2021-05-07 06:58:37

本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。

2021-04-29 06:34:57

幀同步是什么工作原理?如何用VHDL語言實現幀同步的設計?

2021-04-08 06:33:59

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

最近在做個課題,需要用FPGA中的verilog語言實現BPSK調制,fpga不是很會,望大神指導下,急求代碼啊!謝謝

2013-03-06 18:12:36

我正在學習基于FPGA的數據采集系統的設計,請各位大神提供些有關這方面的資料,最好是Verilog HDL代碼!謝謝!

2015-07-16 09:23:32

`求基于XILINX的FPGA數據采集系統,感激不盡!`

2015-06-29 22:13:07

近年來,隨著可編程邏輯器件(CPLD/FPGA)的迅猛發展,可編程邏輯器件在數據采集、邏輯接口設計、電平接口轉換和高性能數字信號處理等領域取得越來越廣泛的應用。CPLD/FPGAD不僅可以解決電子系統

2020-03-05 06:20:45

用易語言實現的串口控制設備和從外部采集數據的范例

2016-10-06 13:14:37

用易語言實現的串口控制設備和從外部采集數據的范例

2016-10-06 17:04:00

綜合考慮到圖像采集系統所要求的實時性,可靠性,以及FPGA在數字電路的設計中的優勢,為此本文討論如何利用FPGA設計基于LVDS的圖像數據采集傳輸系統?

2021-04-08 06:48:28

介紹高速圖像采集系統的硬件結構及工作原理, 講述FPGA 在圖像采集與數據存儲部分的VHDL 模塊設計, 給出采集同步模塊的VHDL 源程序。

2009-04-16 10:45:55 15

15

介紹了用VHDL 語言在硬件芯片上實現浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產品為硬件平臺,以Maxplus II 為軟件工具,實現了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 設計了以CPLD 為核心處理芯片的多路數據采集系統,按照正確的時序直接控制AD676和雙端口RAM的工作, 所有這些功能都采用VHDL語言進行描述。關鍵詞:CPLD, AD676, VHDL語言, 雙端口R

2009-09-01 10:26:41 25

25 網絡測量對網絡研究和發展十分重要,是研究網絡行為基礎。數據采集是網絡性能監測基礎,介紹了數據采集系統的設計與實現,并基于WinPcap 設計實現了網絡數據采集系統,系統較

2009-09-21 10:15:06 16

16 本文介紹了一種基于FPGA 的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA 的實現方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現A/D 轉換器的控制電路、多路

2009-12-19 16:02:33 50

50 本文采用ALTERA 公司Cyclone 系列的FPGA 芯片和IP 核PCI_t32,設計了可應用于LSA 系列激光粒度測試儀的數據采集系統,并在FPGA 內部實現了系統的控制邏輯和PCI總線接口。該系統利用AD73

2009-12-28 11:11:03 22

22 提出了一種利用ARM 和FPGA 架構實現對多通道微應變信號進行數據采集的系統設計方案。通過FPGA 輸出模擬量調節和內部數字量調節的方法,實現了對微應變傳感器的零點校準。可

2009-12-31 14:49:32 27

27 介紹了基于單片機、FPGA的網絡數據加密實現。整個系統由單片機,FPGA和E1通信接口組成。流密碼加密算法采用A5/1和W7算法。采用VHDL硬件語言實現FPGA功能。該硬件加密系統具有較好

2010-12-24 16:26:54 27

27 設計一種基于FPGA的多通道同步數據采集存儲系統,分為多通道同步數據采集模塊和數據存儲模塊。系統設計采用多通道數據的同步實時采集以及壞塊檢測技術。多通道同步數據采集

2010-12-27 15:31:33 70

70 用VHDL語言實現3分頻電路

標簽/分類:

眾所周知,分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 摘要:介紹高速圖像采集系統的硬件結構及工作原理,講述FPGA在圖像采集與數據存儲部分的VHDL模塊設計,給出采集同步模塊的VHDL源程序。

關鍵

2009-06-20 14:35:02 663

663

用VHDL語言實現3分頻電路(占空比為2比1)

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 基于CPLD/FPGA高速數據采集系統的設計

0 引 言 傳統的數據采集系統一般采用單片機,系統大多通過PCI總線完成數據的傳輸。其缺點是數學運算能力差;

2010-01-27 09:35:01 508

508

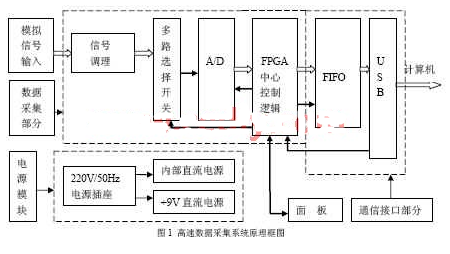

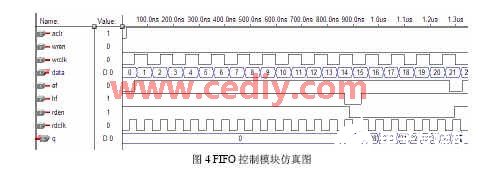

針對膜式氧合器測試中多傳感器數據采集的特性,設計了一種醫用膜式氧合器氧擴散滲透率檢測的多路數據采集系統;系統以FPGA為主控制模塊,對FPGA硬件資源進行功能劃分,分別實現A/D轉換控制、FIFO數據緩存、時鐘分頻等功能,最后通過USB接口實現了數據傳輸;

2011-03-15 15:16:08 21

21 文章介紹了一種基于DSP爭FPGA結構的高精度測井數據采集系統的設計方法,包括信號調理、數據采集、數據處理等。整個系統使用16位高精度A/D轉換芯片AD974。數字電路部分采用Xilinx公司

2011-09-08 17:46:55 70

70 介紹了一種利用標準V HDL (硬件描述語言) 編寫驅動程序的光信號采集系統的實現方法,給出了采用這種方法設計的電路框圖, 并給出了該設計的CPLD (復雜可編程邏輯器件) 實現方法,最后用

2011-11-07 14:56:28 90

90 為解決現有采集存儲系統不能同時滿足高速率采集,大容量脫機且長時間持續存儲的問題,設計了一種基于SATA硬盤和FPGA的數據采集和存儲方案。本設計由AD9627轉換芯片,Altera Cyclone系列

2011-11-15 11:35:19 169

169 CPLD在高速數據采集系統中的應用! 介紹了高速數據采集系統的整體框架分析了其中的通用部分CPLD系列產品的特點及其開發軟件.CPLD根據高速數據采集系統的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 設計了一個基于FPGA的數據采集系統,并用Verilog HDL語言作為描述語言實現了對TLC0820的采樣控制和FPGA的數據處理等過程的控制,以Xilinx ISE 9.1i軟件為平臺,進行了設計輸入、分析與綜合、

2012-05-08 15:17:06 80

80 為了提高大型實驗設備的利用率,在此提出利用Matlab、數據庫、FPGA和服務器等軟硬件設施,實現遠程實驗系統數據采集的方案。該方案中設計了基于FPGA的數據采集箱,利用數據采集箱將

2012-05-17 09:41:19 2031

2031

為了實現某生產線上MCU的數據采集,設計了一種基于FPGA和UART的數據采集系統,并完成系統的軟硬件設計。整個設計完全采用硬件邏輯VHDL語言,集成在一枚Altera的cyclone芯片內,設計了單

2012-09-25 14:24:15 41

41 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 的多通道數據采集系統。所設計的系統通過PCI9054 橋接芯片實現FPGA 局部總線到PMC/PCI總線的轉換,而后再通過PMC/PCI總線完成數據采集系統與上層母板的連接和通訊。

2015-12-18 15:48:43 138

138 高速數據采集系統中的FPGA的設計,下來看看

2016-05-10 11:24:33 15

15 基于FPGA的PXI數據采集系統設計,下來看看

2016-05-10 13:45:28 35

35 基于FPGA的多通道數據采集系統設計,下來看看。

2016-05-10 13:45:28 59

59 基于FPGA的高速數據采集硬件系統設計.

2016-05-10 17:06:40 43

43 基于FPGA的高速數據采集系統接口設計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數據采集系統的設計,下來看看

2016-05-10 17:06:40 19

19 基于FPGA的數據采集板設計與實現,下來看看

2016-05-10 17:46:07 31

31 基于FPGA的高速數據采集系統設計,用ad芯片和sdram構成高速數據采集系統。

2016-05-17 09:49:51 35

35 Xilinx FPGA工程例子源碼:FM收音機的解碼及控制器VHDL語言實現

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:VHDL實現對圖像的采集和壓縮

2016-06-07 14:54:57 6

6 目前許多FPGA的邏輯資源(LE)都已超過1萬門,使得片上可編程系統SOPC已經成為可能。算術邏輯單元ALU應用廣泛,是片上可編程系統不可或缺的一部分。利用VHDL語言在FPGA芯片上設計ALU的研究較少,文中選用FPGA來設計32位算術邏輯單元ALU,通過VHDL語言實現ALU的功能。

2018-07-22 11:22:00 6949

6949

為解決不同性能指標數據采集系統開發時間較長的問題,提出了一種將FPGA軟核技術應用于高速數據采集系統設計的方法。系統以Xilinx公司的FPGA為例設計軟核,使用VHDL語言對軟核進行模塊化

2017-11-24 17:00:12 694

694

本文主要介紹了一種基于STM32+FPGA的數據采集系統的設計與實現,利用STM32硬件中的FSMC、ETHERNETMAC、定時器等外設功能,以及FPGA靈活的邏輯可操控性,解決了系統接口

2017-12-23 15:43:29 36759

36759

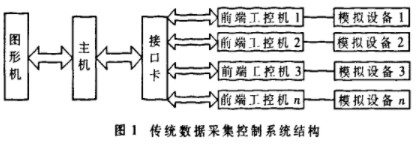

時,數據采集控制的復雜程度愈加惡劣。通過改進數據采集控制器的結構,提高數據采集控制器的自動化和集成化程度,可以有效地提高大型模擬仿真設備數據采集和控制的效率。

2019-05-03 08:28:00 2076

2076

本文介紹了基于FPGA的數據采集系統電路的工作原理和設計過程。根據數據采集技術原理,以Altera公司的EP2C8Q208C8N芯片為核心器件,通過ADC0809采集數據,并用DAC0832輸出數據

2018-09-06 14:25:50 24

24 多片Nandflmh流水線數據存儲模式對高速采集的數據進行存儲。搭建硬件電路,并在FPGA內部通過編寫VHDL語言實現了采集模塊、控制與存儲模塊和Nandflmh存儲功能。調試結果表明,芯片的讀寫時序信號對應的位置準確無誤,沒有出現時序混亂,且采集速度能保持在10

2018-10-12 16:14:48 13

13 介紹了1種基于FPGA和DSP的高速數據采集系統的設計和實現,其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 18

18 設計了以FPGA器件XCSVIXS0為核心處理芯片的高速數據采集存儲系統。在XCSVLXS0內部實現的高速狀態機和相位延遲時鐘作用下,采用4片高速A/D器件流水工作來提高數據采集速度。同時

2018-12-10 16:47:01 22

22 結合數據采集在往復式壓縮機在線監測系統中的應用, 設計了以FPGA(現場可編程門陣列)為核心的邏輯控制模塊的多通道數據采集系統。整個采集系統可實現16 路最大工作頻率為100kHz 的模擬信號的采集

2018-12-18 19:09:43 21

21 核心,比較容易實現復雜的算法[1],但是它們受到信息吞吐量和帶寬的限制,不能實現并行化處理,在高速大批量數據采集時有些乏力。而有極強并行處理數據能力的現場可編程門陣列器件(Field

2020-01-27 16:02:00 768

768

本文介紹了基于FPGA 的數據采集系統電路的工作原理和設計過程。根據數據采集技術原理,以Altera 公司的EP2C8Q208C8N 芯片為核心器件,通過ADC0809數據采集,并用DAC0832

2020-07-29 17:56:14 8

8 FPGA是一種可編程邏輯器件,它具有良好性能、極高的密度和極大的靈活性,外圍電路簡單可靠等特性。因此,該系統設計是由MCU、FPGA、按鍵等部分組成。60路按鍵信號進入FPGA單元,以供數據采集

2020-08-11 14:40:36 655

655

本文檔的主要內容詳細介紹的是使用Quartus和VHDL語言實現的LPC時序的工程文件免費下載。

2020-09-18 16:49:00 20

20 本文檔的主要內容詳細介紹的是基于VHDL硬件描述語言實現CPSK調制的程序及仿真。

2021-01-19 14:34:15 11

11 本文檔的主要內容詳細介紹的是如何使用VHDL硬件描述語言實現基帶信號的MPSK調制。

2021-01-19 14:34:21 2

2 介紹一種基于Actel公司Fusion StartKit FPGA的線陣CCD圖像數據采集系統。以FPGA作為圖像數據的控制和處理核心,通過采用高速A/D、異步FIFO、UART以及電平轉換、放大

2021-02-02 17:12:32 5

5 電子發燒友網站提供《基于VHDL語言實現遠程防盜報警設計.pdf》資料免費下載

2023-11-08 14:33:11 0

0

電子發燒友App

電子發燒友App

評論