1、 概述

隨著信息社會的發展,數據交換,網上交易等活動日益頻繁,從而網絡安全成為人們關注的重要問題。隨著信息技術的發展與應用,信息安全的內涵也在不斷延伸,從最初的信息保密性發展到信息完整性、可用性、可控性和不可否認性,進而又發展為攻(攻擊)、防(防范)、測(檢測)、控(控制)、管(管理)、評(評估)等多方面的基礎理論和實施技術。目前對于安全性有以下三個指標:身份驗證、數據完整性和機密性。

HMAC_SHA1算法在身份驗證和數據完整性方面可以得到很好的應用,在目前網絡安全也得到較好的實現。然而大多數應用通過軟件實現,但其安全性很難得到真正的保障,于是研究安全算法的硬件實現已成為熱點。本文通過對算法和現場可編程芯片特點的分析,優化設計和實現了硬件系統的HMAC_SHA1_96算法應用方案。

2、 SHA1函數

SHA1函數是由美國國家標準和技術局和美國國家安全局設計的與DSS一起使用的安全散列算法SHA,并作為安全散列標準(SHS)的聯邦信息處理標準(FIPS)而公布,SHA1是SHA的修訂版。當輸入長度小于2 64bit消息時,輸出160bit的摘要,其算法步驟如下:

步驟一:填充附加位。一般經過填充使報文長度512取模余64bit。該步驟通常是需要的,即使報文長度已經是所希望的長度。因此填充長度范圍為1到512,最高位為1,其余為0。

步驟二:附加報文長度值。即把一個64bit的報文長度數附加在上述報文之后(高字節優先),從而達到512bit的倍數。

步驟三:初始化變量。可以使用160bit的緩存(即160bit寄存器)來存放該散列函數的初始變量、中間摘要及最終摘要,但首先必須初始化, 給初始變量賦值,即:

A=0x67452301,B=0xefcdab98, C=0x98badcfe,D=0x10325476,E=0xc3d2e1f0

步驟四:處理512bit報文分組。在該步驟中包括四個循環,每個循環有20個處理步驟,而每個循環對 B﹑C﹑D所用的非線性函數不同,并且所用的常數也不同:

對于t=0~19,

ft (B,C,D)=(B∧C )∨((¬B)∧D),

Kt=0x5a827999

對于t=20~39,

ft (B,C,D)=B⊕C ⊕D,

Kt=0x6ed9eba1

對于t=40~59,

ft (B,C,D)=(B∧C )∨(B∧D)∨(C∧D),

Kt=0x8f1bbcdc

對于t=60~79,

ft (B,C,D)=B⊕C ⊕D,

Kt=0xca62c1d6

注:∧表示“與”;∨表示“或”;⊕表示“異或”;¬表示“取反”。

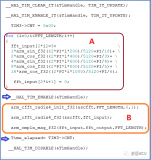

在每一步驟中都將執行如下的算法過程(圖1)。

歸納為以下形式﹐其中 《《《 表示循環左移: A’, B’, C’, D’, E’← ((A《《《5) + ft (B,C,D)+Et +Wt +Kt ), A, (B《《《30), C, D 由于我們輸入的是16個32bit消息,而SHA1運算需要80個32bit數據,所以存在一個由512bit 消息生成2560bit數據的轉換過程(即生成W運算) ,其轉換機制如下:

對于t=0~15, W t=Mt;

對于t=16~79,

Wt=(M t-3⊕Mt-8⊕Mt-14 ⊕Mt-16)《《《1。

步驟五:結果輸出。512bit報文運算完就輸出 160bit的報文摘要。

3、HMAC_SHA1_96算法

HMAC_SHA1_96算法[2,3,6] 是基于單向散列函數SHA1和以密鑰為基礎的完整性檢查驗證機制,它是從生成的160bit摘要中選擇從高到低的96bit作為最終輸出。在該算法中主要就是SHA1函數和HMAC算法。它的作用在于生成摘要放在消息后面以驗證消息在傳輸時是否受到修改或變動,保證消息的完整性。根據HMAC的定義,本設計的HMAC_SHA1_96算法原理圖如圖2。

圖2算法的幾點說明:① _ipad表示補位后的密鑰與ipad 異或的結果,K_opad表示補位后的密鑰與opad異或的結果;② 次SHA1運算包括生成W運算;③ 由SHA1運算輸出的結果是經過加法處理的結果;④ 虛線部分表示圖上忽略的信息分組和相應的SHA1運算部分;⑤ 如果只有512bit消息,則第一輪只需進行兩次SAH1運算,就轉到第二輪。圖2又可寫成如下的表達式:

SHA1( K XOR opad, SHA1(K XOR ipad, M) )

其中 K是密鑰補位后的新值,即在密鑰后補0使之為512bit;ipad是0×36重復16次的一個數組;opad是0×5c重復16次的一個數組;M是消息;XOR表示異或運算;SHA1是安全散列函數。

4、 硬件設計

針對以上算法分析和實現流程特點,結合 FPGA芯片的硬件結構,進行如下的硬件系統設計和優化。

4.1使用RAM結構

在HMAC_SHA1_96算法體系中,有大位數的數據存儲,如果要用寄存器來實現,需要大約7000左右的寄存器,占用大量的FPGA芯片資源,這是因為FPGA芯片上,每個LE(邏輯單元)單元只有一個寄存器,這樣每個LE單元上其它硬件資源將會浪費。然而FPGA芯片上大量的ESB(嵌入式系統塊)資源沒有充分利用,而ESB可以用來實現各種類型的存儲模塊,如RAM、ROM、FIFO和CAM等,在這種情況下,可以采用ESB實現RAM來代替寄存器,從而節省LE硬件資源,并且RAM存儲數據,控制起來比寄存器方便很多。

4.2 重復利用相同模塊

正如前面算法所述,SHA1算法是由80次運算組成的,而每次運算的結構又是一樣的,如果采用水線形式的運算模式,利用80個同樣的模塊,會占用很多的硬件資源,不符合優化設計的要求,因此可以先優化設計出一個模塊,再對該模塊復用80 次,每一次運算的結果需存入寄存器,以便送入下一次運算,這樣可極大地優化利用FPGA硬件資源。

4.3 模塊劃分

HMAC_SHA1_96算法體系的硬件實現,必會存在與外圍電路的數據握手傳輸。由于外圍電路(8255或CPU)的工作時鐘頻率與所設計的芯片工作時鐘頻率不一樣,要讓設計芯片與外圍電路協調工作,就必須專門設計輸入輸出接口電路,再設計出核心處理模塊,從而不受外界電路工作環境影響。由此,可以將本設計分為三個部分:輸入模塊、算法實現模塊和輸出模塊。

4.3.1 輸入模塊

由于輸入模塊會跟外圍電路(如8255)連接進行信號或數據傳輸,根據握手信號ACK和OBF,每次輸入8bit數據寫到64×8bit的RAM,需要64 次,而外圍電路什么時候輸入數據由內部信號sha_end控制,該模塊的輸出一次為32bit,所以相當于一次讀4×8bit數據。

4.3.2 算法實現模塊

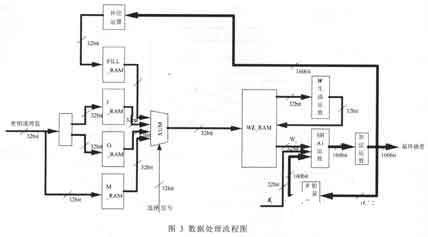

該模塊主要進行HAMC_SHA運算,輸出160bit摘要,其數據處理流程圖見圖3(圖中 M_RAM用來存儲消息),其中又可以分為以下幾個主要部分:

① 密鑰輸入處理部分。處理密鑰時需要先對其進行異或運算,然后把其寫入兩個32×16bit的 RAM,假設分別為I_RAM和O_RAM。I_RAM里數據在第一輪SHA1算法首先運算,而O_RAM 里的數據要到第二輪才開始運算。

② 生成W處理部分。 由于SHA1函數中要進行80次運算,每次運算采用不同的32bit W值,而輸入的只有16個32bit數據,于是該算法采用四個不同的W值進行異或運算生成新的W值。這四個W值是從80×32bit的W_RAM讀出的,而生成新的 W值再依次寫入該RAM中沒有使用的位置。

③ SHA1運算部分。是設計的核心部分,需要完成80次運算,每次從32×80bit RAM讀出一個32bit W值,最終生成160bit摘要。

④ 摘要處理部分。主要對每一次SHA1運算后生成的摘要與本次的初始密鑰進行加法運算,作為下次SHA1運算的初始密鑰,或者作為最終輸出摘要,或者作為下一輪SHA1運算的消息輸入。

⑤ 摘要補位部分[6] 。對第一輪生成的160bit摘要進行補位,方法為:[160]~[190] 0[191] 1 [192]~[479] 0 [480]~[511]=1010100000,將此值寫入一個16×32bit的FILL_RAM。

4.3.3 輸出模塊

同輸入模塊一樣,由于同外圍電路進行信號或數據傳輸,根據握手信號STB和IBF,每次輸出8bit數據到外圍電路,但該部分主要是一個8×12bit RAM,可以一次寫入96bit數據。

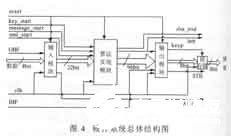

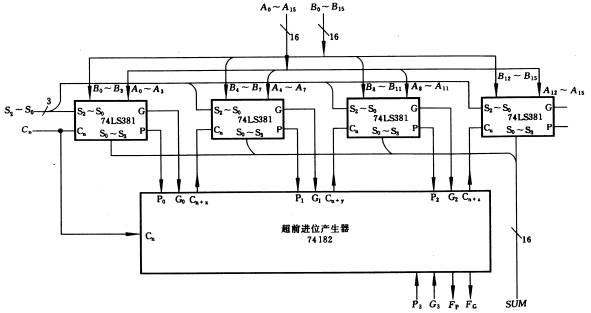

4.4 硬件系統總體結構

在數據輸出端加鎖存器是為了保證輸出數據被外圍電路采樣之前始終有效,從而達到本設計與外圍電路協調工作的目的。結構圖如圖4。

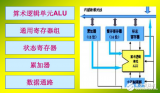

5、 FPGA實現

我們知道,FPGA芯片內部結構是由邏輯陣列塊(LAB)、嵌入式系統塊(ESB)、快速通道互聯和輸入輸出單元(IOE)組成。LAB是由10個LE、LE 間關聯的進位鏈﹑級連鏈﹑LAB控制信號和LAB局部互連構成,可以實現快速運算通道,特別適合本設計算術運算單元的硬件實現。ESB如前所說,可以用來實現不同的存儲模塊,特別適合于大位數的數據存儲。快速通道是用來實現LE之間,ESB 與I/O之間的快速互連,并且具有高扇出能力,它是一系列縱橫交錯的連續式分布通道,能夠得到高性能和快速的信號傳輸,提高本設計運算效率和信號的穩定性。I/O單元由一個雙向緩沖器和一個寄存器組成,含有可編程延時,可確保零保持時間或最小的時鐘到輸出時間,減少設計數據輸出的毛刺現象。另外FPGA可以重復使用,以方便修改代碼或參數時再重新配置FPGA。

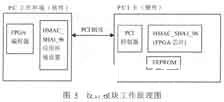

本設計采用Altera的APEX20KE160EQC240_1X 芯片實現,其功能模塊及PC接口原理圖見圖5。

圖中FPGA編程器采用QuartusⅡ2.0軟件, HMAC_SHA1_96應用環境設置主要配置軟件控制HMAC_SHA1_96的運行機制,PCI控制器用來控制FPGA芯片與PCI BUS的通訊。先通過QuartusⅡ2.0軟件對代碼布局布線生成pof文件或sof文件, pof文件可直接用來配置FPGA,但每次使用時必須重新配置;而sof文件可以先存入EEPROM,再由 EEPROM對FPGA配置,每次上電前由EEPROM配置,這樣可以直接應用于信息安全硬件系統中。

責任編輯:gt

電子發燒友App

電子發燒友App

評論