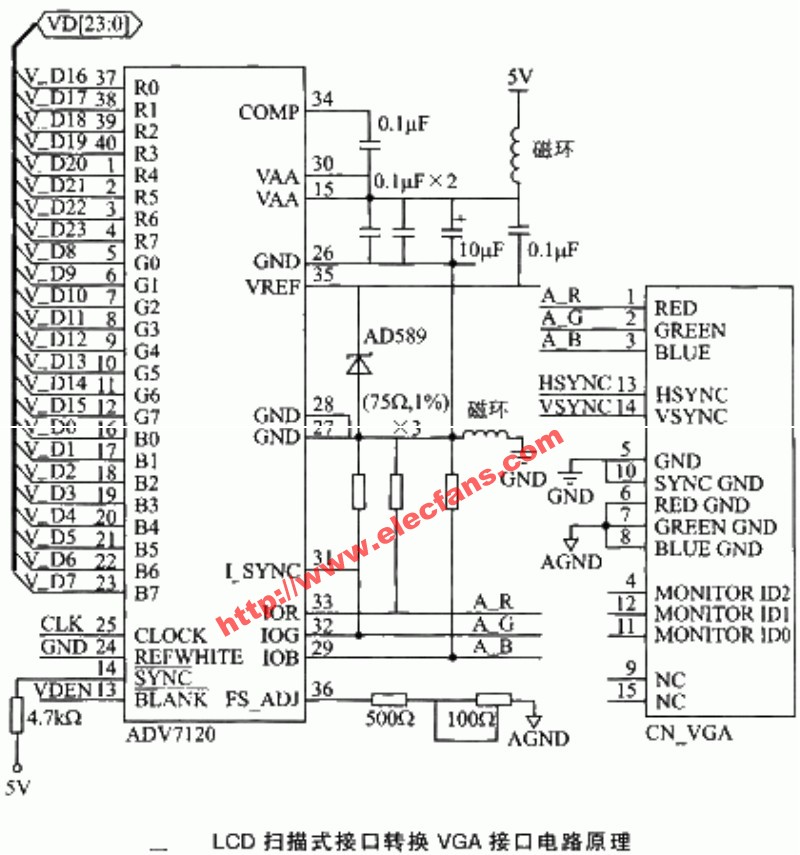

VGA 作為通用的顯示接口,其可使用的設備非常多。根據 VGA 的文檔,我們了解到使用 VGA,只需要在給定的時鐘頻率下,向 VGA 線發出不同的信號即可。

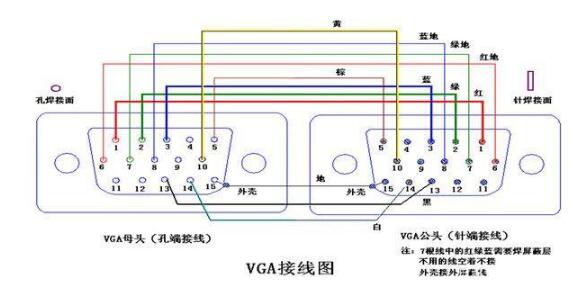

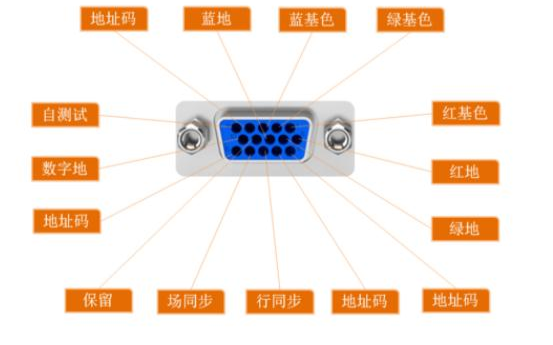

VGA 輸出的信號一共有 5 個有效信號,分別是:

VGA_RED(紅色端子),VGA_BLUE(藍色端子),VGA_GREEN(綠色端子),VGA_HSYNC(水平同步端子),VGA_VSYNC(垂直同步端子)。

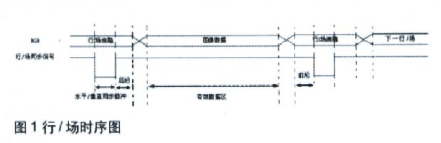

如果采用水平掃描的方法,且為 640 x 480 的分辨率,我們需要:

時鐘頻率為 25MHz(或者也可以采用 28.3MHz,參考 VGA 文檔)。

水平同步端子輸出信號包含 4 個階段,每個周期共占用 800 個時鐘周期。

脈沖周期(用于同步):96 周期,輸出低電平

前端周期(用于緩沖):48 周期,輸出高電平

顯示周期(用于顯示):640 周期,每一個時鐘周期顯示一個像素點的內容,讀取紅、藍、綠色端子的信息作出顯示。同步端子輸出高電平。

后端周期(用于緩沖):16 周期,輸出高電平

垂直同步端子輸出信號也包含 4 個階段,由于是水平掃描,所以在垂直同步中的顯示周期中,水平同步端子將對其正確的進行顯示,它包含了 480 個水平同步周期,掃描 480 行的內容。也可以說一個垂直同步周期中,顯示出一個屏幕的內容。

垂直同步端子的脈沖周期為 2 個水平同步周期;后端周期為 29 個水平同步周期;顯示周期為 480 個水平同步周期;前端周期為 10 個水平同步周期,故總周期數為

[latex]T=(480+2+10+29) * (96+16+640+48) = 416800[/latex]cycles

刷新頻率為

[latex]f = frac {25MHz} {416800} = 59.98 Hz[/latex]

即屏幕的刷新頻率約為 60Hz。若需采用其它的分辨率,只需改變顯示周期長度以及為該模塊提供不同的時鐘周期即可。顯示周期等參數都在 vga_header.v 文件中定義。編寫過程中,如果出現屏幕提示類似于“顯示超出范圍”的提示語,則說明同步周期不正確,改正同步周期長度即可。

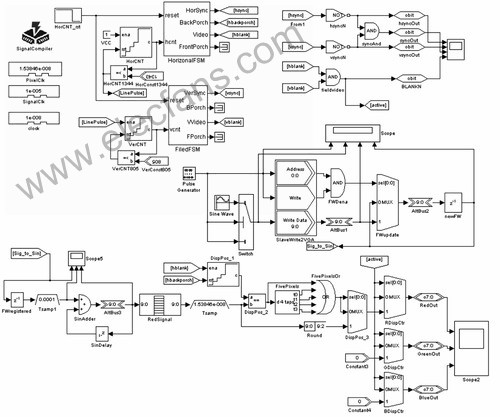

為了實現同步信號的準確計時,我們采用了有限狀態機對它進行控制。以下源代碼可供參考:

always @ (negedge clk)

begin

? ? /* Ver

tical Sync. Signal */

? ? case (v_state)

? ? ? ? 0:? begin? ? ? ?/* TPW 同步脈沖周期*/

? ? ? ? ? ? ? ? if (cv_thres == 0) begin

? ? ? ? ? ? ? ? ? ? v_sync? ? ? <= 0;? ? ? ? ?/* 信號置低*/

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ?<= 0;? ? ? ? /* 計數器繼續計數 */

? ? ? ? ? ? ? ? end else begin

? ? ? ? ? ? ? ? ? ? v_state? ? ?<= 1;? ? ? ? /* 進入下一狀態*/

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ?<= 1;? ? ? ? /* 計數器清零 */

? ? ? ? ? ? ? ? ? ? cv_value? ? <= `VGA_SYNC_V_POR_BACK-1;? ? ? ? /* 計數器置位 */

? ? ? ? ? ? ? ? ? ? v_sync? ? ? <=? 1;? ? ? ? /* 同步信號置高 */

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

? ? ? ? 1: begin? ? ? ? /*

TFP 前端周期 */

? ? ? ? ? ? ? ? if (cv_thres == 0) begin

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <=? 1;? ? ? ? /* 同步信號置高 */

? ? ? ? ? ? ? ? ? ? v_addr? ? ? ? ? ? ? ? <=? 0;? ? ? ? /* 垂直地址清零 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? <=? 0;? ? ? ? /* 計數器計數*/

? ? ? ? ? ? ? ? end else begin

? ? ? ? ? ? ? ? ? ? v_state? ? ? ? ? ? ? ? <=? 2;? ? ? ? /* 進入下一狀態 */

? ? ? ? ? ? ? ? ? ? cv_value? ? ? ? <=? `VGA_SYNC_V_DISPLAY-1;? ? ? ? /* 計數器置位 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? <=? 1;? ? ? ? /* 計數器清零 */

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <=? 1;? ? ? ? /* 垂直同步信號置高 */

? ? ? ? ? ? ? ? ? ? h_state? ? ?<=? 0;? ? ? ? /* 置水平同步狀態 */

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

? ? ? ? 2: begin? ? /* TDISP顯示周期 */

? ? ? ? ? ? ? ? if (cv_thres == 0) begin

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <= 1;? ? ? ? /* 垂直同步信號置高 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? <= 0;? ? ? ? ?/* 計數器計數 */

? ? ? ? ? ? ? ? end else begin

? ? ? ? ? ? ? ? ? ? v_state? ? ? ? ? ? ? ? <=? 3;? ? ? ? ?/* 進入下一狀態 */

? ? ? ? ? ? ? ? ? ? cv_value? ? ? ? <=? `VGA_SYNC_V_POR_FRONT-1; /* 計數器置位 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? <=? 1;? ? ? ? /* 計數器清零 */

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <=? 1;? ? ? ? /* 垂直同步信號置高 */

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

? ? ? ? 3: begin? ? ? ? /* TBP后端周期 */

? ? ? ? ? ? ? ? if (cv_thres == 0) begin

? ? ? ? ? ? ? ? ? ? v_addr? ? ? ? ? ? ? ? <=? 0;? ? ? ? /* 垂直地址清零 */

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <=? 1;? ? ? ? ?/* 垂直同步信號置高 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? ?<=? 0;? ? ? ? ?/* 計數器計數 */

? ? ? ? ? ? ? ? end else begin

? ? ? ? ? ? ? ? ? ? v_state? ? ? ? ? ? ? ? <=? 0;? ? ? ? /* 進入下一狀態,即狀態0 */

? ? ? ? ? ? ? ? ? ? cv_value? ? ? ? <=? `VGA_SYNC_V_PUL_WIDTH-1; /* 計數器置位 */

? ? ? ? ? ? ? ? ? ? cv_en? ? ? ? ? ? ? ? <=? 1;? ? ? ? ?/* 計數器清零 */

? ? ? ? ? ? ? ? ? ? v_sync? ? ? ? ? ? ? ? <=? 0;? ? ? ? ?/* 垂直同步信號置低 */

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

?

? ? /* ...... *

通過該模塊生成了水平、垂直同步信號和對應的水平地址和垂直地址后,使用垂直地址和水平地址讀取對應的像素點信息,分為兩種:

a. 圖形模式:圖形模式是一個一個的像素點,我們采用了 BlockRAM 來保存這些像素點信息。由于空間有限,我們只能保存 320 x 240 個像素點,并擴大輸出范圍,進行單色 640 x 480 輸出,否則將因為空間不夠而編譯不通過。如果我們可以采用板上內置的 DDR 模塊就可以拓展其規模,而且板上的 DDR SDRAM 具有 64M,是鎂光生產的模塊,在 Xilinx 提供的 IPCore 中有對應的模塊,只需要提供建立后提供相對應的管腳即可完成輸出。由于 D/A 模塊無法做到(見下面),這個修改并沒有太大的意義,所以我們沒有做到這個工程中去。

b. 文字模式:文字模式支持的是 80 x 30 個文字的顯示,我們依然采用了 BlockRAM 來保存這些文字,每個文字占用 3 個字節,分別表示其 ASCII 碼(1 B)和 16位 RGB 信息(5-6-5格式,2B),文字后,再通過字庫 TextFontROM 模塊生成對應的像素點信息。讀出某一行中應該顯示的字符,而后顯示在屏幕上。由于內存占用并不像圖形模式那么大,我們采用了 640 x 480 格式的輸出。

電子發燒友App

電子發燒友App

評論