VGA(視頻圖形陣列)作為一種標準的顯示接口得到廣泛的應用。依據VGA顯示原理,介紹了利用FPGA實現對VGA圖形控制器的Verilog設計方法。詳細描述了各硬件模塊的工作原理及實現途徑,并給出了軟件設計思路。

隨著可編程邏輯器件的不斷發展及其價格的不斷下降,EDA開發軟件的不斷完善,可編程邏輯設計的應用優勢逐漸顯示出來,特別是大規模可編程器件。而FPGA具有功能強大,開發過程投資小、周期短等特點,成為當今硬件設計的首選方式之一。VGA(視頻圖形陣列)作為一種標準的顯示接口得到廣泛地應用。利用FPGA芯片和EDA設計方法,可以靈活地根據用戶需求,設計出針對性強的VGA顯示控制器,不僅降低了生產成本也可以方便快速地對產品進行升級換代。設計采用 Quartus II 軟件工具,并以 Altera公司的Cyclone系列FPGA的器件為主實現硬件平臺的設計。

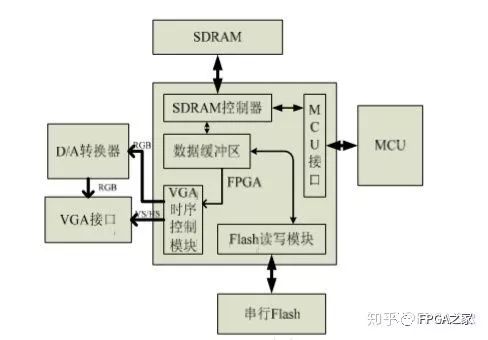

1. 硬件系統框圖采用模塊化設計方法。

本設計的VGA控制器主要由以下模塊組成:VGA 時序控制模塊、內部時鐘產生模塊、SDRAM控制模塊、串行Flash讀取模塊等,如圖1所示。

圖1 系統框圖

2. 主要模塊設計

2.1 VGA 時序控制模塊

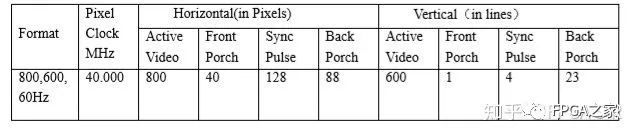

VGA時序控制模塊是整個顯示控制器的關鍵部分,其實質就是完成VGA顯示卡的功能。主要作用就是在一定的工作頻率下,產生準確的時序關系(VS-垂直同步信號,HS-水平同步信號,消隱信號之間的關系)。及其在準確的時序下對數據緩存區對數據進行讀取,讀完數據后使 SDRAM 控制器及時的刷新緩存區的數據。其中產生準確的時序關系為此模塊重點,在VGA顯示過程中,完成一行掃描所需要的時間稱為水平掃描時間,完成一幀掃描所需要的時間稱為垂直掃描時間。每掃描完一行用行同步信號進行同步;掃描完所有行后用場同步信號進行同步。本設計采用的是800Hz x 600Hz x 60Hz模式。依據時序標準,每顯示行包含1056點,其中800點為有效顯示區,256點為消隱區,每行的行同步脈沖低電平寬度為128個像素點;同理每場有628行,有效行為600行,其中場同步脈沖低電平寬度為4行。其行、場時序如表 1 。

表 1 行掃描、場掃描時序

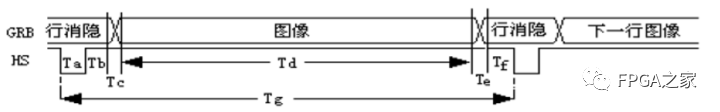

圖2 HS時序

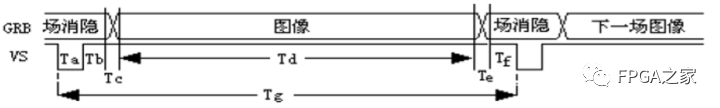

圖3 VS時序

其中圖2,td=800,tg=1056,ta=80,te+tf=80,tb+tc=128,單位為一個像素時鐘周期。

其中圖3,td=600,tg=628,ta=1,te+tf=23,tb+tc=4,單位為一個line時間。

依據這個標準,外部50MHz時鐘經過FPGA內部PLL得到所需要的40MHz像素時鐘,并進行對應的像素點數和掃描行數進行分頻處理,可以得到符合要求的行頻率、場頻率和消隱信號。

2.2 SDRAM控制模塊及動態數字顯示方法

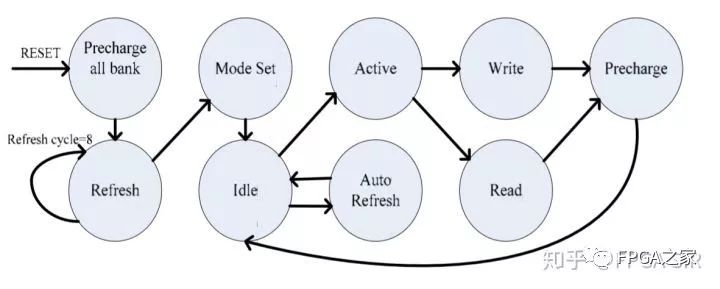

在基于FPGA的圖像顯示系統中,常常需要用到大容量、高速度的存儲器。而在各種隨機存儲器件中,SDRAM的價格低、速度快、容量大是比較理想的器件。但SDRAM控制邏輯較為復雜,要采用狀態機的設計方法來實現 SDRAM 的控制模塊(也可以使用SDRAM IP核實現)。其 SDRAM控制狀態機如圖 4 。

圖4 SDRAM狀態機

其中包含了9個狀態,其中從Precharge到ModeSet為SDRAM上電后的初始化過程,其余狀態為SDRAM的正常讀寫及刷新操作過程。對于SDRAM自身的操作本文不做詳細介紹,下面具體介紹動態顯示數字的方法。

系統上電后,SDRAM上電后的初始化完成后。先通過Flash讀寫控制模塊,把Flash中的靜態圖片讀取出來,然后寫入SDRAM中直到Flash中的圖片完全存入SDRAM。此時啟動VGA時序控制模塊進行圖片的顯示。

對于動態顯示數字方法,可以先利用字模提取軟件把字模信息提取出來。而 Altera公司的FPGA器件內均內置了嵌入式陣列塊,通過調用其中的LPM_ROM模塊。可以任意設置參數,構成內置的ROM存儲器,存儲所摘要的字模信息。本系統的字模為16pixels長 x 16pixels寬 x 16位色(R5G6B5),所以利用LPM_ROM模塊,占用了將近10個 M4K(FPGA內置 塊ram)。

本系統通過接受外部 MCU 發來的命令來確定顯示數字的區域及要顯示的數字。因為VGA時序中存在較長的消隱期間,其期間是沒有顯示數據傳遞的。所以可以通過消隱期間實行對SDRAM的寫操作,對圖片固定地址寫入字模信息。其具體步驟:

(1)、確定要顯示數字的圖像區域首地址;

(2)、確定要顯示數字信息位于ROM中的地址;

(3)、啟動 SDRAM 寫操作;

(4)、SDRAM 寫操作地址增加16后,地址繼續增加800(即一行),而 ROM地址每次增加 1;

(5)、如此循環16 次(字模為 16 x16)后,如果還有要寫的數字則繼續(1)步驟,否則停止寫操作。

因為只是動態的改變數字,所以對原圖像改動的數據量不是很大,所以不會造成圖像閃爍現象。此方法缺點就是字模占用的 塊RAM 資源較多,如果字模只是固定顏色的情況,則 塊RAM 資源只用到 1 個 M4K,所以在資源緊張的情況下還得需要各方面比較,得到最合適的顏色分配。

2.3 Flash 的讀寫模塊

現在數字電路設計中,經常需要保存大量數據,Flash Memory 以其集成度高、低成本、使用方便等優點,因此也成為設計人員的首選。

Flash可以分兩類:并行和串行。并行存儲量大,速度快;而串行存儲量相對較小,但體積小連線簡單,可減少電路面積,節約成本,二者各有優缺點,根據實際需要選取。本系統對速度要求不是很高,所以選用了串行 Flash,為意法半導體推出的 M25P32。M25P32為SPI 接口,具有 4MB 容量,對與本設計每幅圖片接近 1MB,則可以存儲 4 副圖片,可以進行 4 個界面的切換顯示。

其模塊設計必須嚴格按照 Flash 的時序控制信號。對于首次使用 Flash,先需要進行擦除操作,編程指令可以將 1 變成 0。往 Flash 寫入圖片數據時,還是需要調用 FPGA 中的宏模塊制作一個 ROM,但是由于 Flash 容量較大,一般FPGA沒有這么大的存儲空間,所以數據需要分多次寫入。FPGA的ROM數據保存在.mif文中,.mif 由 Matlab 直接生成.mif文件,也可以在 Quartus II 中生成。

在對 M25P32 的操作中,需要注意的是一些指令在操作完成后,需要留出一段時間 Flash進行數據處理,比如寫寄存器為 5ms~15ms等,如果沒有等待這段處理過程,則會出現一些誤操作。

FLASH操作步驟:

(1)、FLASH擦除,一般通過SPI發FLASH擦除命令,等待結束。

(2)、FLASH寫,發送寫命令,寫地址,數據。一般FLASH保存一些參數,或者數據存儲用,如果FLASH內已經有可用的數據,可以根據實際情況,也可以先讀FLASH。

(3)、FLASH讀,發送讀命令,讀地址。

3、驗證

利用可編程邏輯器件(FPGA)可以很方便地實現數字系統設計,而在Altera的QuartusII軟件平臺下,FPGA 設計的各個階段都得到了很好的支持,兩者有效結合使得數字系統的設計更加方便快捷。

通過硬件平臺的驗證,基于 FPGA 的VGA圖形顯示器已達到設計要求,可以穩定地實現界面的顯示,并可以在界面上根據需要進行數字的動態改變顯示,對于一些工業監控場合的應用,尤其數據量不是很大的場合尤為適合,不僅可以及時顯示當前狀態,還可以保存關機時狀態。

-

FPGA

+關注

關注

1637文章

21842瀏覽量

608529 -

圖形控制器

+關注

關注

0文章

8瀏覽量

11306

原文標題:基于FPGA的VGA圖形控制器的設計

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PIC32MZDA圖形控制器問題

如何使用Verilog實現基于FPGA的SDRAM控制器?

基于FPGA的LCD&VGA控制器設計

VGA圖形控制器的FPGA實現

基于FPGA的VGA圖形控制器設計

基于FPGA的圖形式AMLCD控制器的設計

采用FPGA對VGA圖形控制器的Verilog設計方法

采用FPGA對VGA圖形控制器的Verilog設計方法

評論