美國賽靈思(Xilinx)2012年4月5日使用28nm工藝制造的FPGA “Virtex-7 X690T”演示了有線通信系統(tǒng)(背板)。該FPGA配備有80個以最大13.1Gbit/秒的速度工作的高速串行收發(fā)器“GTH”,已于2012年

2012-04-09 11:13:59 2848

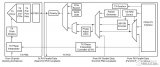

2848 xilinx的7系列FPGA根據(jù)不同的器件類型,集成了GTP、GTX、GTH以及GTZ四種串行高速收發(fā)器,四種收發(fā)器主要區(qū)別是支持的線速率不同,圖一可以說明在7系列里面器件類型和支持的收發(fā)器類型以及

2020-11-20 12:08:15 17712

17712

本來寫了一篇關于高速收發(fā)器的初步調(diào)試方案的介紹,給出一些遇到問題時初步的調(diào)試建議。但是發(fā)現(xiàn)其中涉及到很多概念。逐一解釋會導致文章過于冗長。所以單獨寫一篇基本概念的介紹,基于Xilinx 7系列

2020-12-15 17:18:16 4531

4531

FPGA收發(fā)器GTX/GTH參考時鐘接口提供兩種連接方式:LVDS(如圖1所示)和LVPECL(如圖2所示)。我們在選擇晶振時,至少要支持其中一種接口輸出電平標準。圖2所示的電阻值為一般推薦值,實際

2022-08-09 12:28:24 1703

1703 輸入輸出端口 從Implemented Design中可以看到FPGA中資源大致分布如下。中間藍色是CLB可編程邏輯塊、DSP或BRAM,兩側(cè)的彩色矩形塊是I/O接口和收發(fā)器,劃分的方塊是不同的時鐘域 Configurable Logic Block (CLB)可編程邏

2022-12-27 15:54:52 1788

1788 你好我嘗試使用xilinx 7系列收發(fā)器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收發(fā)器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

你好我將生成一個7系列收發(fā)器的示例設計,在我的設計中有20位計數(shù)器發(fā)生器數(shù)據(jù)到7系列GTX。但運行工具流程,報告時間違規(guī)。怎么解決?時間約束:create_clock -name

2018-11-01 16:12:04

FPGA高速收發(fā)器設計原則高速FPGA設計收發(fā)器選擇需要考慮的因素

2021-04-09 06:53:02

高速收發(fā)器(SERDES)的運用范圍十分廣泛,包括通訊、計算機、工業(yè)和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數(shù)據(jù)的系統(tǒng)。但普通高速收發(fā)器的并行總線設計已無法滿足現(xiàn)在的要求。將收發(fā)器整合在FPGA中,成為解決這一問題的選擇辦法。FPGA高速收發(fā)器設計時,我們需要注意哪些事項呢?

2019-08-07 06:26:42

_XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)電壓主要有VCCINT(內(nèi)核電壓),VCCRAM(RAM塊電壓),VCCAUX(輔助電壓),VCCO(IO電壓)以及高速串行收發(fā)器GTX Transceiver的供電電壓。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2021-12-28 06:38:44

我正在研究使用高速收發(fā)器接收部分的定制電路板。所有四個接收器的參考時鐘相同,為125 MHz。我從焦平面陣列(FPA)接收數(shù)據(jù)并使用8 / 10b編碼。我可以讓FPA重復顯示空白行(字符1FFD

2020-05-05 11:39:41

/O管腳分析,可以參考表1-1管腳定義說明。2.Xilinx7系列FPGA管腳Pinout文件下載我們在進行原理圖庫設計時,如何獲得FPGA每個管腳定義呢?在UG475官方文檔第二章7 Series

2021-05-28 09:23:25

/O管腳分析,可以參考表1-1管腳定義說明。2.Xilinx7系列FPGA管腳Pinout文件下載我們在進行原理圖庫設計時,如何獲得FPGA每個管腳定義呢?在UG475官方文檔第二章7 Series

2021-07-08 08:00:00

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2022-09-27 06:46:35

? Zynq? 7000 series (XC7Z045)FPGA.This design uses several LMZ3 series modules, LDOs, and a DDR

2018-11-05 16:42:31

RocketIO收發(fā)器怎么實現(xiàn)高速通信?

2021-05-26 06:28:57

`描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現(xiàn)電流

2015-05-11 10:30:22

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2018-09-10 09:02:14

你好我想用7系列收發(fā)器IP,但我不知道為什么GTX可以高速運行?為什么GTX收發(fā)器的速度比基本的IOB快?

2020-08-13 10:31:42

引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述GTX/GTH收發(fā)器時鐘

2021-11-11 07:42:37

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發(fā)器。請問我能直接把FPGA的引腳直接連在CAN收發(fā)器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:25:39

分享無線收發(fā)器使用到的石英晶振a,工業(yè)級-40~85度,頻率點:32.768KHz 、12.5pF,20PPM; 12MHz/16MHz/24MHz/25MHz,27MHz/20pF,20ppm b

2011-05-30 21:26:29

基于FPGA的通用異步收發(fā)器設計

2012-08-18 00:03:20

,pin_to_pin兼容FPGAXC7K410T-2FFG900,支持8-Lane PCIe、64bit DDR3、四路SFP+連接器、四路SATA接口、內(nèi)嵌16個高速串行收發(fā)器RocketIO GTX,軟件

2015-01-28 15:48:55

基于XC7K325T的四路萬兆PCIe光纖收發(fā)卡一、板卡概述 本板卡基于Xilinx公司的FPGA XC7K325T-2FFG900 芯片,pin_to_pin兼容

2014-11-24 15:31:02

大家好,我正著手開發(fā)我的第一個真正的FPGA PCB。沒有更簡單的開發(fā)板:)我正在試圖弄清楚如何使用帶有FPGA的1000BASE-T 1.25 GBd小型可插拔收發(fā)器。我告訴我需要終止FPGA上

2019-01-22 10:22:55

嗨,我正在嘗試在XC7k325t-2 FPGA中實現(xiàn)6G-SDI的參考設計。https://www.xilinx.com/support/documentation

2020-08-14 10:05:53

這是我的第一個涉及FPGA的項目,我正在尋找更有經(jīng)驗的用戶的好建議,指出我正確的方向。我想實現(xiàn)一個通過以太網(wǎng)端口連接到源的2.4GHz,15Mbps獨立通信收發(fā)器。我一直在檢查SDR系統(tǒng)的實現(xiàn),但

2019-08-19 10:17:23

驗證以下時鐘策略的人是否可以對XC7A15T-2CPG236C有效?我是一名PCB設計師,尚未完全熟悉Xilinx工具套件。我正在提供一個帶有相應ref時鐘輸入的5GHz收發(fā)器。在收發(fā)器模塊之外

2020-05-11 09:06:46

`FPGA 的全稱是“現(xiàn)場可編程門陣列”,而能夠以較低的功耗、將信號高速引入或推出的收發(fā)器,將是該領域在未來很長一段時間內(nèi)的一個主戰(zhàn)場。據(jù)悉,FPGA 有望迎來一個可充編輯邏輯的終極功能世界,通過

2020-09-02 18:55:07

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數(shù)據(jù)傳輸系統(tǒng)的設計與實現(xiàn),系統(tǒng)包含AXI DMA和GTX串行收發(fā)器,系統(tǒng)增加了流量控制機制來保證高速數(shù)據(jù)傳輸?shù)目煽啃浴W詈筮M行了仿真測試,測試結(jié)果顯示系統(tǒng)可以高速可靠地傳輸數(shù)據(jù)。

2021-05-25 06:45:36

有時間在3G-SDI視頻輸出中出錯。我想知道有沒有辦法將一個收發(fā)器同步到另一個收發(fā)器?以上來自于谷歌翻譯以下為原文Hi,How to Snyc one 7 Series Transceiver

2018-10-30 18:03:36

和 Kintex-7 均可認為其定位為高性價比,用戶可根據(jù)自己的需要自行選擇,官方的說法是,Artix-7 系列提供了最高性能功耗比結(jié)構(gòu)、 收發(fā)器線速、DSP 處理能力以及 AMS 集成,Kintex-7 系列

2020-12-23 17:21:03

描述PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2018-08-31 08:59:25

有沒有辦法用7系列收發(fā)器接收數(shù)據(jù)并將這些數(shù)據(jù)保存到BRAM,同時在填充時將其讀出?如果是這樣,除了來自IP目錄的收發(fā)器IP和BRAM IP的收發(fā)器向?qū)е猓€需要什么? AXI從BRAM讀出到PC

2019-04-26 11:18:18

求助FPGA高速串行收發(fā)器,輸出12.5Gbps的信號要用什么電平輸出28.5Gbps的信號要用什么電平?

2014-11-10 09:12:51

本帖最后由 scratdqy 于 2015-8-17 11:06 編輯

向各位大神求助GTX問題!!用xilinx的Vivado中的7 Series FPGAs Transceivers

2015-07-28 18:54:12

描述PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現(xiàn)電流和電壓

2018-08-10 09:36:45

賽靈思 Artix-7 FPGA 是業(yè)界唯一的在低端器件上整合了高速收發(fā)器的方案,該方案提供了自適應均衡、2D 眼圖以及IBIS-AMI仿真模型來簡化針對成本敏感型應用的高速串行設計,觀看視頻,4分鐘教您搞定高速SerDes端口設計。

2016-07-27 17:29:59

什么是解復用電路?解復用電路在高速收發(fā)器中的應用是什么?

2021-05-19 06:24:03

你好我試圖在KC705板上使用收發(fā)器來生成比特流。我正在使用Vivado 2012.3和7系列FPGA收發(fā)器向?qū)2.3。我之前使用過具有不同傳輸者名稱的IBERT核心。IBERT收發(fā)器名稱類似于

2020-07-28 10:29:31

我是FPGA設計的新手,但我已經(jīng)閱讀了數(shù)據(jù)表,應用筆記......幾周以來我仍然無法使用收發(fā)器。但絕望之后,我只是按照這個示例/教程:http://china.xilinx.com/support

2020-07-24 14:35:18

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發(fā)器。請問我能直接把FPGA的引腳直接連在CAN收發(fā)器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:05:37

GX-FPGA-XC7A100T-SOM是北京革新創(chuàng)展科技有限公司開發(fā)的一款基于XILINX ARTIX-7系列FGG484封裝類型的芯片而開發(fā)的高性能核心板。核心板具有高速度、高帶寬、高容量等特點

2022-03-09 11:33:24

FPGA, Artix-7, MMCM, PLL, 400 I/O, 628 MHz, 215360單元, 950 mV至1.05 V, FCBGA-676XILINX Artix?-7

2022-11-10 15:13:15

關鍵詞 TJA1042、高速、低功耗、CAN 收發(fā)器摘 要TJA1042 是一款高速CAN 收發(fā)器,是CAN 控制器和物理總線之間的接口,為CAN 控制器提供差動發(fā)送和接收功能

2009-11-10 13:50:18 364

364 FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

FPGA高速收發(fā)器設計原則

高速收發(fā)器(SERDES)的運用范圍十分廣泛, 包括通訊、計算機、工業(yè)和儲存,以及必須在芯片與

2009-04-07 22:26:14 986

986 Omate1100光纖收發(fā)器使用說明書

2016-12-23 02:24:58 0

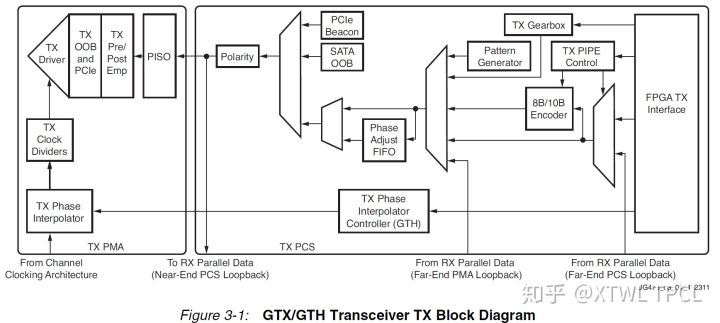

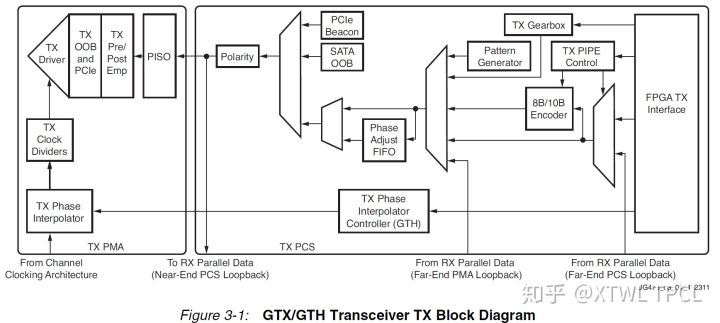

0 GTX RX接收端的結(jié)構(gòu)和TX發(fā)送端類似,數(shù)據(jù)流方向相反,不過和發(fā)送端也有一些區(qū)別,GTX的RX接收端結(jié)構(gòu)圖如圖1所示: 圖1 下面將根據(jù)數(shù)據(jù)流方向介紹一下RX接收端各個電路部分的功能。 RX Equalizer (DFE and LPM):RX信號從AFE(模擬前端)進來之后,首先經(jīng)過RX均衡器,均衡器的主要作用是用于補償信號在信道傳輸過程中的高頻損失,因為信道是帶寬受限的,所以信號經(jīng)過它必將造成衰減甚至遭到破壞。

2017-11-10 14:49:02 5516

5516

PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有

2017-02-08 09:14:00 671

671 PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發(fā)器 (MGT) 供電時所需的所有電源軌。 它利用一個 PMBus 接口來實現(xiàn)電流和電壓

2017-02-08 09:22:11 419

419 了解如何在您的 ?UltraScale? FPGA? 設計中部署串行收發(fā)器。了解并利用串行收發(fā)器模塊的特性,如 ?8B/10B? 和 ?64B/66B? 編碼、通道綁定、時鐘校正和逗點檢測。其它專題

2017-02-09 08:04:41 327

327 賽靈思(Xilinx)公司FPGA器件的高速串行收發(fā)器類別如下

2017-02-11 11:11:30 5958

5958

(Xilinx)FPGA中LVDS差分高速傳輸?shù)膶崿F(xiàn)

2017-03-01 13:12:04 64

64 提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收發(fā)器設計的一個高速串行傳輸實現(xiàn)方案,詳細闡述了硬件設計要點和軟件實現(xiàn)概要,系統(tǒng)實測表明,該方案能在某信號處理系統(tǒng)兩個板卡之間穩(wěn)定地進行1.6 Gb/s的數(shù)據(jù)傳輸,誤碼率優(yōu)于10e-12,傳輸距離大于1米。

2017-11-21 10:16:00 7689

7689 Xilinx公司業(yè)界首款28 nm FPGA Kintex-7 10Gbps 收發(fā)器性能演示。

2018-06-01 15:50:00 3960

3960 Xilinx7系列GTZ(高達28.05Gb_s)高速串行收發(fā)器性能與兼容性演示。

2018-05-24 17:54:00 4900

4900 設計人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴接收機均衡來補償信號失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發(fā)器 和 Altera Stratix V GX 收發(fā)器的均衡能力。

2018-05-23 15:47:00 3974

3974

經(jīng)理。我從事FPGA工作已經(jīng)有12年了。他們中后5人的主要工作是高速串行收發(fā)器應用。

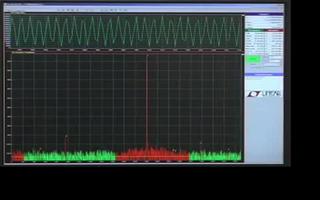

我們今天在這里演示新的Linear Technology LTC2274模數(shù)轉(zhuǎn)換器怎樣與具有嵌入式串行收發(fā)器

2018-06-20 05:28:00 4215

4215

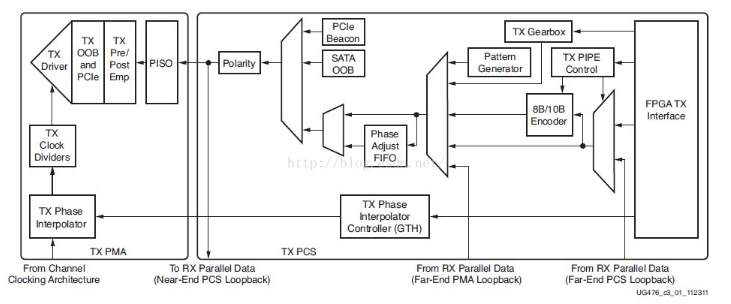

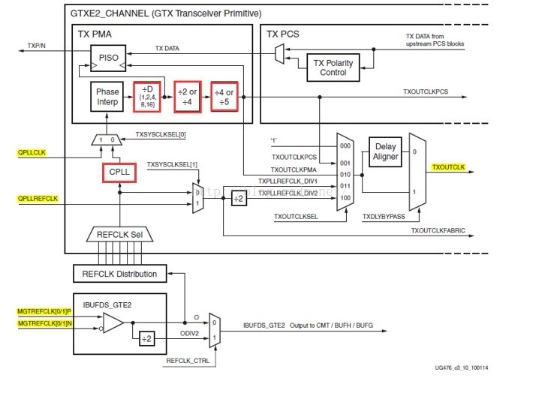

每一個收發(fā)器擁有一個獨立的發(fā)送端,發(fā)送端有PMA(Physical Media Attachment,物理媒介適配層)和PCS(Physical Coding Sublayer,物理編碼子層)組成

2018-06-20 13:48:00 2709

2709

首次演示新型Xilinx 7系列GTH收發(fā)器,通過背板以13.1 Gb / s的速度運行。

2019-01-03 13:25:38 4048

4048 該演示展示了Xilinx SERDES開發(fā)的最新成果,首次公開展示了Xilinx 58Gb / s PAM4收發(fā)器。

2018-11-29 06:21:00 2048

2048 該視頻演示了具有32.75G背板功能的Virtex?UltraScale+?FPGA,功率優(yōu)化的收發(fā)器。

該收發(fā)器具有同類最佳的發(fā)送抖動和第三代客戶驗證的自適應接收器均衡功能......

2018-11-28 06:39:00 2161

2161 Xilinx推出全球首款28nm FPGA,展示10Gbps SERDES功能

Xilinx在Kintex-7 K325T FPGA上展示了10Gbps收發(fā)器,這是有史以來第一款28nm FPGA。

2018-11-28 06:30:00 3785

3785 憑借Kintex?-7 FPGA系列,Xilinx可實現(xiàn)每瓦性價比的理想平衡。

通過提供具有競爭力的價位的高端功能,如尖端收發(fā)器和高速集成IP,Kintex-7 FPGA是理想的選擇。

2018-11-28 06:25:00 2822

2822 Xilinx GTX(12.5 Gb / s)收發(fā)器與SFP +和10G背板一起運行。

2018-11-30 06:36:00 9807

9807 展示7系列GTZ(高達28.05Gb / s)高速串行收發(fā)器的性能;

與Luxtera公司的不重定時光模塊進行四路26G對接,實現(xiàn)100G應用。

2018-11-23 06:20:00 3057

3057 通過Virtex-7 2000T FPGA中的GTX收發(fā)器實現(xiàn)高速串行性能。

2018-11-22 06:27:00 3461

3461 本章介紹virtex-6 FPGA GTH收發(fā)器向?qū)В⑻峁┫嚓P信息,包括其他資源、技術支持和向xilinx提交反饋。向?qū)ё詣訄?zhí)行創(chuàng)建HDL包裝器的任務,以配置virtex-6設備中的高速串行GTH收發(fā)器。

2019-02-20 09:35:45 4

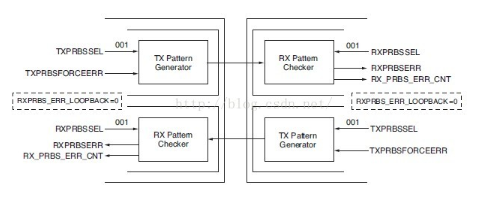

4 7系列FPGA GTP收發(fā)器的可定制Logicore?IP Chipscope?Pro集成誤碼率測試(IBert)內(nèi)核用于評估和監(jiān)控GTP收發(fā)器。該核心包括在FPGA邏輯中實現(xiàn)的模式生成器和校驗

2019-02-20 14:30:00 25

25 光纖收發(fā)器使用說明

2020-07-20 08:00:00 19

19 和AFCT-701SDZ 10 Gbs以太網(wǎng)SFP +收發(fā)器產(chǎn)品與具有自適應DFE的XilinxVirtex?-6FPGA 11.18 Gbps收發(fā)器的高速互操作性。 Xilinx產(chǎn)品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

本文檔的主要內(nèi)容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現(xiàn)優(yōu)化設計。

2021-01-13 17:00:59 25

25 IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發(fā)器設計的,用于評估和監(jiān)控GTX收發(fā)器。IBERT包括在FPGA邏輯中實現(xiàn)的模式生成器和檢查器,以及對端口的訪問和GTX收發(fā)器的動態(tài)重新配置端口屬性,還包括通信邏輯,以允許設計在運行時通過JTAG進行訪問。

2021-05-02 22:10:00 5587

5587

晶振是數(shù)字電路設計中非常重要的器件,時鐘的相位噪聲、頻率穩(wěn)定性等特性對產(chǎn)品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發(fā)器輸入?yún)⒖紩r鐘的硬件設計及FPGA軟件設計給出設計案例,供大家參考。

2021-04-07 12:00:44 3914

3914

Virtex-5 RocketIOTM GTP收發(fā)器的串行高速系統(tǒng)接口開發(fā)過程中位寬轉(zhuǎn)換的幾個技術問題提出了解決方案,并以SATA2.0開發(fā)為例,通過Xilinx Virtex-5 XC5VLX50T FPGA驗證方案進行了可行性驗證。

2021-06-24 16:10:42 2510

2510

引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述 GTX/GTH收發(fā)器時鐘

2021-11-06 19:51:00 35

35 _XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)電壓主要有VCCINT(內(nèi)核電壓),VCCRAM(RAM塊電壓),VCCAUX(輔助電壓),VCCO(IO電壓)以及高速串行收發(fā)器GTX Transceiver的供電電壓。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2022-01-06 11:20:19 11

11 xilinx的7系列FPGA根據(jù)不同的器件類型,集成了GTP、GTX、GTH、GTZ四種串行高速收發(fā)器,可以支持多種協(xié)議如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

收發(fā)器使用背對背三態(tài)緩沖器將不同設備連接到共享雙向雙向數(shù)據(jù)的公共通信總線。

2022-04-18 15:54:54 4355

4355

電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA高速串行收發(fā)器(HSST)用戶指南.pdf》資料免費下載

2022-09-26 10:25:17 22

22 AMIS-42700 雙路高速 CAN 收發(fā)器

2022-11-14 21:08:27 1

1 本文開源一個FPGA高速串行通信項目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收發(fā)器,本工程主要是圍繞該IP核采用Vivado提供的例程創(chuàng)建。

2023-10-01 09:48:00 2604

2604

如何計算高速RS485收發(fā)器的功耗? 高速RS485收發(fā)器是一種常見的通信設備,用于對串口數(shù)據(jù)進行收發(fā)。對于高速RS485收發(fā)器,我們需要了解它的功耗計算方法,以便在使用過程中合理計劃電源供應

2023-10-31 14:37:15 554

554

電子發(fā)燒友App

電子發(fā)燒友App

評論