外延工藝是指在襯底上生長完全排列有序的單晶體層的工藝。一般來講,外延工藝是在單晶襯底上生長一層與原襯底相同晶格取向的晶體層。外延工藝廣泛用于半導體制造,如集成電路工業的外延硅片。MOS 晶體管

2023-02-13 14:35:47 10447

10447 工藝設計與優化應用領域:集成電路(硅柵、鋁柵CMOS、BiCMOS)、分立器件(DIODE、TRANSISTOR、MOS)、功率器件(DMOS、VDMOS、LDMOS、BCD、IGBT)、特種器件、光電子器件、半導體傳感器、MEMS等`

2015-01-07 16:15:47

MEMS器件等工藝咨詢,謝謝!北京方華佳瑞科技有限公司

2016-11-08 14:25:07

,熱量是不能及時傳導,易形成局部高溫,進而可能損傷元器件、組件,從而影響系統的可靠性及正常工作周期 。所以慎重選擇電源灌封膠非常重要,可以使用有機硅材質的電源灌封膠,因其優良的物理化學性能和工藝性能成為灌

2019-02-27 17:19:23

硅-硅直接鍵合技術主要應用于SOI、MEMS和大功率器件,按照結構又可以分為兩大類:一類是鍵合襯底材料,包括用于高頻、抗輻射和VSIL的SOI襯底和用于大功率高壓器件的類外延的疏水鍵合N+-N-或

2018-11-23 11:05:56

?是提高性能和降低價值。硅襯底倒裝波LED芯片,效率會更高、工藝會更好。6英寸硅襯底上氮化鎵基大功率LED研發,有望降低成本50%以上。 目前已開發出6寸硅襯底氮化鎵基LED的外延及先進工藝技術,光效

2014-01-24 16:08:55

,特別是近年來碳納米管的發展令人注目,在速度、集成度、特別是功耗方面都將有重大突破,但離開實際應用可能比硅基量子器件要更遠一些。原文見王陽元院士在“納米CMOS器件”書中寫的序(2004年1月科學出版社出版)。 :

2018-08-24 16:30:27

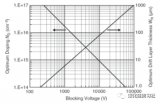

`硅瞬態抑制器件可分為兩大類:具有固定電壓的硅瞬態抑制二極管(TVS)和非固定電壓的晶閘管結構瞬態抑制器件(TSS)。瞬態抑制器件選用一般遵循以下原則:1)器件反向轉折電壓不低于電路的正常工作電壓

2017-06-27 09:30:27

采用印刷臺手工印刷焊膏的工藝看完你就懂了

2021-04-25 07:06:44

%以上的良品率。雙臺面的方片可控制硅、觸發管采用雙臺面GPP工藝,正背面兩個對應的溝道內均有鈍化玻璃。刀片切割很難兼顧上、下兩層鈍化玻璃,切割成品電性良率低。目前廠商采取降低切割速度來提高切割成品率,刀片

2008-05-26 11:29:13

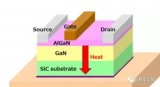

不同,MACOM氮化鎵工藝的襯底采用硅基。硅基氮化鎵器件既具備了氮化鎵工藝能量密度高、可靠性高等優點,又比碳化硅基氮化鎵器件在成本上更具有優勢,采用硅來做氮化鎵襯底,與碳化硅基氮化鎵相比,硅基氮化鎵晶元尺寸

2017-09-04 15:02:41

和控制電路、直至接口、通信和電源等集成于一塊或多塊芯片上的微型器件或系統。而MEMS傳感器就是采用微電子和微機械加工技術制造出來的新型傳感器。MEMS是用傳統的半導體工藝和材料,以半導體制造技術為

2016-12-09 17:46:21

與硅相比,SiC有哪些優勢?SiC器件與硅器件相比有哪些優越的性能?碳化硅器件的缺點有哪些?

2021-07-12 08:07:35

Verilog設計內外延時

2012-08-15 16:31:14

各位大俠,小女子在做半導體退火的工藝,不知道哪位做過有n型單晶硅退火?具體參數是什么?任何經驗都可以提,請照顧一下新手,謝謝!:handshake

2011-03-01 09:37:32

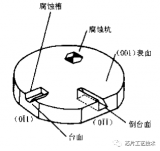

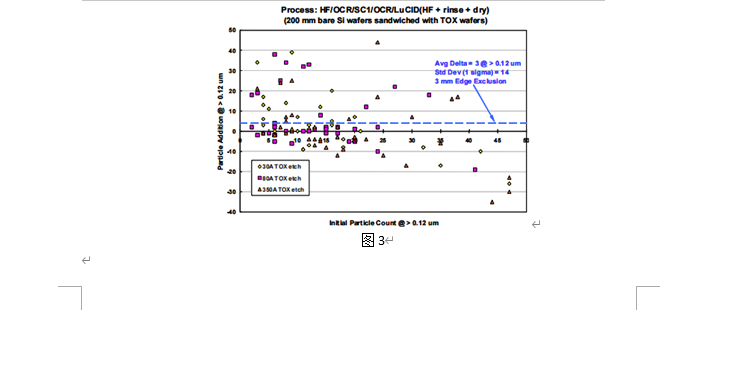

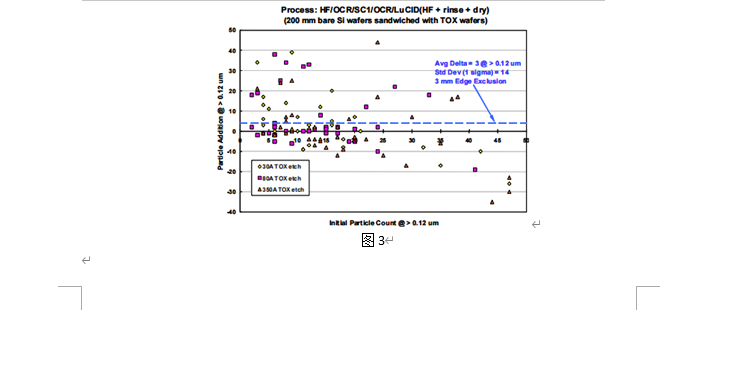

清潔 - 表面問題:金屬污染的起源:來源:設備、工藝、材料和人力,Si表面的過渡金屬沉淀是關鍵。去污:可以對一些暴露于堿或其他金屬污染物的基材進行去污。晶片不得含有任何污染薄膜。這通常在硅的 KOH

2021-07-01 09:42:27

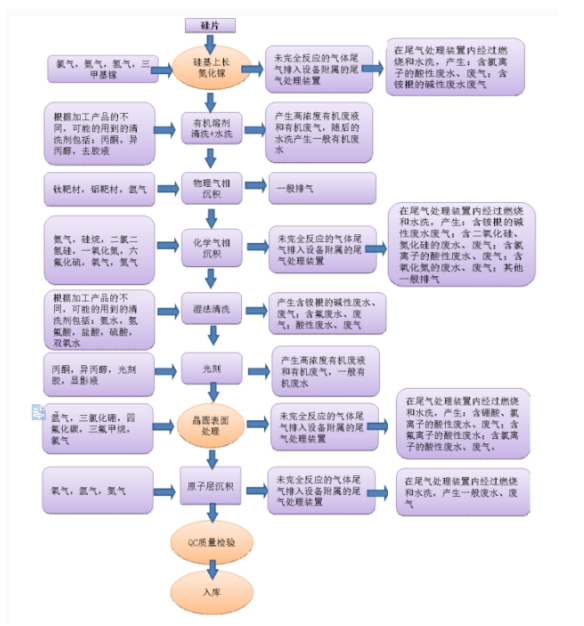

書籍:《炬豐科技-半導體工藝》文章:CMOS 單元工藝編號:JFSJ-21-027作者:炬豐科技網址:http://www.wetsemi.com/index.html晶圓生產需要三個一般過程:硅

2021-07-06 09:32:40

GaN 襯底上獲得高性能的薄膜器件,必須使 GaN 襯底的表面沒有劃痕和損壞。因此,晶圓工藝的最后一步 CMP 對后續同質外延 GaN 薄膜和相關器件的質量起著極其重要的作用。CMP 和干蝕刻似乎

2021-07-07 10:26:01

一種用于制造非常薄的 BCB 鍵合層的可靠且可重復的工藝,不僅將為緊湊型混合硅激光器鋪平道路,還將為其他有前景的光子器件的開發鋪平道路,例如基于漸逝光的光隔離器或放大器耦合。在以下部分中,我們將介紹

2021-07-08 13:14:11

MOS器件的幾何尺寸已經不能滿足器件性能的提高,需要一些額外的工藝技術來提高器件的電學性能,例如應變硅技術。應變硅技術是通過外延生長在源漏區嵌入應變材料使溝道發生應變,從而提高載流子遷移率,最終提高器件

2018-09-06 20:50:07

本電路如下圖所示,該逆變電路采用了TL494脈寬調制集成電路,TL494是一款廣泛用于開關電源的集成元件,在本電路中用作可控硅的開關驅動器件,可控硅采用30A/100V的單向可控硅,以獲得足夠的功率輸出,變壓器圖中給出了具體的繞制參數供參考。

2021-04-23 06:13:41

可控硅是中頻電源 的心臟,它的正確使用對中頻電源的運行至關重要。一臺中頻電源一年損壞三五只可控硅尚屬正常,如果經常燒硅,電爐停擺,影響生產,就要引起警覺了。可控硅的工作電流從幾百安到幾千安,電壓

2013-10-17 09:37:47

可控硅是中頻電源的心臟,它的正確使用對中頻電源的運行至關重要。一臺中頻電源一年損壞三五只可控硅尚屬正常,如果經常燒硅,電爐停擺,影響生產,就要引起警覺了。可控硅的工作電流從幾百安到幾千安,電壓通常在

2013-10-14 10:26:02

)、氮化鎵(GaN)、碳化硅(SiC)、雙極硅、絕緣硅(SoI)和藍寶石硅(SoS)等工藝技術給業界提供了豐富的選擇。雖然半導體器件的集成度越來越高,但分立器件同樣在用這些工藝制造。隨著全球電信網絡向

2019-08-02 08:23:59

材料,將常規集成電路工藝和微機械加工獨有的特殊工藝相結合,全面繼承了氧化、光刻、擴散、薄膜、外延等微電技術,還發展了平面加『[技術、體硅腐蝕技術、固相鍵合技術、LIGA技術等,應用這些技術手段制造出層

2019-08-01 06:17:43

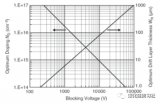

本文將討論瑞能半導體的高壓可控硅及其應用和工藝技術。 威能高壓可控硅 SCR 或可控硅整流器被定義為具有四層 p-n-p-n 結構的開關器件,導致雙穩態行為,可以在高阻抗、低電流關斷狀態和低

2023-02-24 15:34:46

級設計、器件級仿真、工藝模擬和版圖設計。在工藝模擬功能方面,目前的商業軟件,雖然都支持三維工藝模擬,但是工藝的模擬和實現都是比較簡單和理想化的,并且缺乏工藝設計能力。而目前很多MEMS研究人員對工藝

2019-06-25 06:41:25

我想了解關于LED關于外延片生長的結構,謝謝

2013-12-11 12:50:27

半導體器件與工藝

2012-08-20 08:39:08

)、氮化鎵(GaN)、碳化硅(SiC)、雙極硅、絕緣硅(SoI)和藍寶石硅(SoS)等工藝技術給業界提供了豐富的選擇。雖然半導體器件的集成度越來越高,但分立器件同樣在用這些工藝制造。隨著全球電信網絡向

2019-07-05 08:13:58

)、氮化鎵(GaN)、碳化硅(SiC)、雙極硅、絕緣硅(SoI)和藍寶石硅(SoS)等工藝技術給業界提供了豐富的選擇。雖然半導體器件的集成度越來越高,但分立器件同樣在用這些工藝制造。隨著全球電信網絡向長期

2019-08-20 08:01:20

`智興豐科技是一家專業的電子元器件供應商,與配套方案提供商。驅動IC主要應用于吸頂燈,筒燈,球泡燈等LED照明行業可控硅又叫做晶閘管,是一種常用的半導體器件,是一種能像閘門一樣控制電流大小的半導體

2020-05-08 10:39:14

可控硅電源采用的串聯諧振,即電壓型諧振頻率跟蹤。因此效率較高、功率因數較高。所以有明顯的節電效果,加熱每噸棒料用電341度。 可控硅電源前級不可控全橋整流,不會在整流段引起波形的變形,沒有關斷角

2014-02-27 11:53:46

通俗的說,可控硅是一個控制電壓的器件,由于可控硅的導通角是可以用電路來控制的,固此隨著輸出電壓Uo的大小變化,可控硅的導通角也隨著變化。加在主變壓器初級的電壓Ui也隨之變化。

2019-10-16 09:01:04

裝置具有相當高的變換效率(90-95%),輸出功率低時,電源轉換效率并不降低,特別是在熱處理行業中,有些被加熱工件需要分段加熱,頻繁開機和停機,在停機狀態下無損耗。因此,在感應加熱行業中采用可控硅中頻

2013-12-27 09:11:10

梁上在10 000gn加速度作用下壓阻元件所受的平均應力,如表2所示。 4 壓阻式硅微型加速度傳感器加工工藝 壓阻式傳感器的懸臂梁常采用CVD工藝在硅片上外延生長一層外延層刻蝕而成,文中試用鍵合

2018-11-01 17:23:05

本文采用0.18 μm CMOS工藝設計了一種適用于TI-ADC的高速、低功耗開環T&H電路。

2021-04-20 06:58:59

IR2132驅動芯片的特點是什么 IR2132內部結構及其工作原理采用IR2132器件實現單芯片電源供電的三相逆變器的驅動

2021-04-12 06:07:00

中元器件的介質隔離,徹底消除了體硅CMOS電路中的寄生閂鎖效應;采用這種材料制成的集成電路還具有寄生電容小、集成密度高、速度快、工藝簡單、短溝道效應小及特別適用于低壓低功耗電路等優勢,因此可以說SOI

2012-01-12 10:47:00

增加效率(PAE:poweraddedefficiency),非常的適用于高層(hightier)的無線通訊中長距離、長通信時間的需求。砷化鎵元件因電子遷移率比硅高很多,因此采用特殊的工藝,早期為

2016-09-15 11:28:41

,優化退火工藝,可一次性成膜一次性退火完成。 平面光波導器件 平面光波導器件是采用平面光波導技術制造而成的器件,分為無源器件、有源器件以及有源/無源混合集成器件。無源平面光波導器件,顧名思義,無需能

2018-02-22 10:06:53

` 有誰用過SEMILAB的SRP-2000外延片厚度測試儀,關于測試儀的機構和控制部分,尤其是精度部分希望交流,資料可發g-optics@163.com,多謝!`

2018-11-20 20:25:37

最近在做一個用晶閘管或者可控硅做電源開關的項目,請問在這個電路里可控硅怎么實現開通和關斷?非常感謝!

2017-07-11 22:41:13

這種工藝技術的芯片并不常見,但是只要這種將硅基芯片與載體PCB直接連接的IC存在:并且在設計方案中可行,那么采用這樣的IC器件就是較好的選擇。 一般來說,在匯封裝設計中,降低電感并且增大信號與對應回路

2017-09-19 10:59:22

電子器件制備工藝

2012-08-20 22:23:29

大家好,有沒有人看到過,半導體器件按照工藝進行分類的資料,比如像CMOS/SOI CMOS/SOS 體硅CMOS NMOS TTL等這樣的分類。先謝謝了

2012-07-02 10:09:49

突破工藝對器件最小尺寸的限制

2021-01-06 06:30:08

幾個問題:一是硅的缺陷比較多,它的發光效率比較差。二是用硅做外延成長時,由于硅本身會吸收光線,因此必須把硅拿掉,用別的基材(不管是用金屬還是其他基材)來做光源的承載體。這里必須做一個基板的轉換,這個工藝本身

2012-03-15 10:20:43

1995年希臘科學家A.G.Nassiopuoulos等人用高分辨率的紫外線照相技術,各向異性的反應離子刻蝕和高溫氧化的后處理工藝,首次在硅平面上刻劃了尺寸小于20nm的硅柱和 硅線的表面結構,觀察到了類似于多孔硅的光激發光現象。

2019-09-26 09:10:15

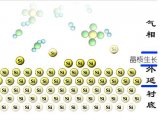

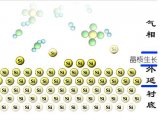

外延生長法(LPE)外延生長法(epitaxial growth)能生長出和單晶襯底的原子排列同樣的單晶薄膜。在雙極型集成電路中,為了將襯底和器件區域隔離(電絕緣),在P型襯底上外延生長N型單晶硅層

2019-08-16 11:09:49

的標準表面工藝發展:由于機械結構的復雜性,僅采用單層結構往往不能制備出所需構件,多層化是表面硅MEMS工藝必然的發展趨勢。美國的MUMPs是典型的民用標準表面工藝線,該工藝可以實現多達4層的犧牲層和多晶硅層

2018-11-05 15:42:42

請問各大神硅光電池在AD里有現有的元器件庫嗎

2016-05-08 21:08:45

硅技術的迅猛發展使工程師們能夠設計和創建出新型電路,這些電路的速度和性能以前只有用基于GaAs和InP的HBT(異質結雙極晶體管)和PHEMT技術才能達到,電路的核心就是鍺化硅(SiGe)工藝

2019-07-30 07:56:50

采用EEPROM 工藝設計通用陣列邏輯器件——遇到的問題與解決方案深圳市國微電子股份有限公司 裴國旭電可擦除只讀存儲器(EEPROM)工藝可廣泛運用于各種消費產品中,像微

2009-12-14 11:41:35 51

51 VDMOS功率器件用硅外延片:1973 年美國IR 公司推出VDMOS 結構,將器件耐壓、導通電阻和電流處理能力提高到一個新水平。功率VDMOS 管是在外延片上制作的,由于一個管芯包括幾千個元胞

2009-12-21 10:52:24 40

40 LED 外延片--襯底材料襯底材料是半導體照明產業技術發展的基石。不同的襯底材料,需要不同的外延生長技術、芯片加工技術和器件封裝技術,襯底材料決定了半導體照明技

2010-12-21 16:39:29 0

0 啟用PowerFill外延硅工藝的電源設備

ASM International推出了其PowerFill的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。 PoweRFill是一個精

2010-01-23 08:35:54 539

539 ASM啟用功新的PowerFill外延技術的電源設備

ASM今天推出了其PowerFill(TM)的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。 PowerFill是一個精

2010-01-23 09:32:32 795

795 ASM啟用新的PowerFill外延技術的電源設備

ASM International近日推出了其PowerFillTM的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。owerFill是

2010-01-27 08:39:29 1820

1820 濟寧高新區聯電科技園核心企業冠銓(山東)光電科技有限公司成功研制出4寸LED 外延片,并生產出第一爐。此次研制成功的4寸外延片,每片產出的芯片數量約為2寸工藝的4倍。

2012-11-26 09:25:46 1043

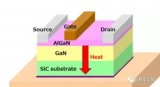

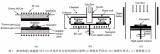

1043 典型的GaN射頻器件的加工工藝主要包括如下環節:外延生長-器件隔離-歐姆接觸(制作源極、漏極)-氮化物鈍化-柵極制作-場板制作-襯底減薄-襯底通孔等環節。

2018-10-26 17:33:06 10616

10616 LED的波長、亮度、正向電壓等主要光電參數基本上取決于外延片材料,因此,外延片材料作為LED工作原理中的核心部分,了解LED外延片技術的發展及工藝非常重要。

2018-11-01 16:41:12 4524

4524 1月9日晚間,國星光電(002449)發布公告,宣布投資10億擴產新一代LED封裝器件及配套外延芯片。

2019-01-14 15:05:40 3112

3112 看到一些新聞,表示某國高科技企業開發了一種新型襯底材料,與GaN晶格匹配,可以良好生長GaN。(備注:GaN體單晶制備難度非常大,因此此處所提的GaN是外延層,此處暴露了外延層存在的意義之一

2021-01-11 11:18:08 23512

23512 最近做芯片和外延的研究,發現同樣的外延工藝和芯片工藝做出來的芯片性能差別很大,大到改變試驗設計的“世界觀”。基板襯底的質量好壞很關鍵。

2021-08-12 10:55:58 4302

4302

控制外延層的摻雜類型和濃度對 SiC 功率器件的性能至關重要,它直接決定了后續器件的比導通電阻,阻斷電壓等重要的電學參數。

2022-04-11 13:44:44 4802

4802 本文研究了外延沉積前原位工藝清洗的效果,該過程包括使用溶解的臭氧來去除晶片表面的有機物,此外,該過程是在原位進行的,沒有像傳統上那樣將晶圓從工藝轉移到沖洗罐。結果表明,與不使用溶解臭氧作為表面處理

2022-04-12 13:25:49 559

559

通過圖形化硅氧化或氮化硅掩蔽薄膜生長,可以在掩蔽膜和硅暴露的位置生長外延層。這個過程稱為選擇性外延生長(SEG)。

2022-09-30 15:00:38 5892

5892 本文聊一下GaN芯片的制備工藝。

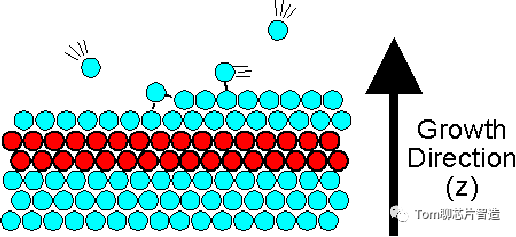

GaN-般都是用外延技術制備出來。GaN的外延工藝大家可以看看中村修二的書。

2022-10-19 11:53:40 1459

1459 固相外延,是指固體源在襯底上生長一層單晶層,如離子注入后的熱退火實際上就是一種固相外延過程。離于注入加工時,硅片的硅原子受到高能注入離子的轟擊

2022-11-09 09:33:52 10250

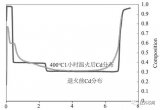

10250 氮化鎵外延片生長工藝較為復雜,多采用兩步生長法,需經過高溫烘烤、緩沖層生長、重結晶、退火處理等流程。兩步生長法通過控制溫度,以防止氮化鎵外延片因晶格失配或應力而產生翹曲,為目前全球氮化鎵外延片主流制備方法。

2023-02-05 14:50:00 4345

4345 氮化鎵外延片指采用外延方法,使單晶襯底上生長一層或多層氮化鎵薄膜而制成的產品。近年來,在國家政策支持下,我國氮化鎵外延片行業規模不斷擴大。

2023-02-06 17:14:35 3012

3012 硅基氮化鎵外延生長是在硅片上經過各種氣體反應在硅片上層積幾層氮化鎵外延層,為中間產物。氮化鎵功率器件是把特定電路所需的各種電子組件及線路,縮小并制作在極小面積上的一種電子產品。氮化鎵功率器件制造主要

2023-02-11 11:31:42 6159

6159

通常是指的在藍寶石襯底上用外延的方法(MOCVD)生長的GaN。外延片上面一般都已經做有u-GaN,n-GaN,量子阱,p-GaN。

2023-02-12 14:31:25 2100

2100 氮化鎵外延片工藝是一種用于制備氮化鎵外延片的工藝,主要包括表面清洗、氮化處理、清洗處理、干燥處理和檢測處理等步驟。

2023-02-20 15:50:32 10569

10569 功率半導體分立器件的主要工藝流程包括:在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),進行芯片封裝,對加工完畢的芯片進行技術性能指標測試,其中主要生產工藝有外延工藝、光刻工藝、刻蝕工藝、離子注入工藝和擴散工藝等。

2023-02-24 15:34:13 3185

3185 在半導體科學技術的發展中,氣相外延發揮了重要作用,該技術已廣泛用于Si半導體器件和集成電路的工業化生產。

2023-05-19 09:06:46 2467

2467

外延層是在晶圓的基礎上,經過外延工藝生長出特定單晶薄膜,襯底晶圓和外延薄膜合稱外延片。其中在導電型碳化硅襯底上生長碳化硅外延層制得碳化硅同質外延片,可進一步制成肖特基二極管、MOSFET、 IGBT 等功率器件,其中應用最多的是4H-SiC 型襯底。

2023-05-31 09:27:09 2827

2827

金剛石異質外延已發展 30 年有余,而基于 Ir 襯底的大面積、高質量的異質外延單晶金剛石已取得較大進展。本文主要從關于異質外延單晶金剛石及其電子器件兩個方面對異質外延單晶金剛石的發展進行了闡述。

2023-07-12 15:22:23 843

843

碳化硅功率器件與傳統硅功率器件制作工藝不同,不能直接制作在碳化硅單晶材料上,必須在導通型單晶襯底上額外生長高質量的外延材料,并在外延層上制造各類器件。

2023-08-03 11:21:03 286

286

碳化硅功率器件與傳統硅功率器件制作工藝不同,不能直接制作在碳化硅單晶材料上,必須在導通型單晶襯底上額外生長高質量的外延材料,并在外延層上制造各類器件。

2023-08-15 14:43:34 1001

1001

氮化鎵功率器件與硅基功率器件的特性不同本質是外延結構的不同,本文通過深入對比氮化鎵HEMT與硅基MOS管的外延結構

2023-09-19 14:50:34 2703

2703

列陣探測器引起了人們的廣泛關注。為了滿足高性能、雙多色紅外焦平面器件制備的要求,需要對碲鎘汞p型摻雜與激活進行專項研究。使用分子束外延方法直接在碲鎘汞工藝中進行摻雜,As很難占據Te位,一般作為間隙原子或者占據金屬位,

2023-09-26 09:18:14 284

284

電子發燒友網站提供《LED外延芯片工藝流程及晶片分類.doc》資料免費下載

2023-11-03 09:42:54 0

0 半導體器件為什么要有襯底及外延層之分呢?外延層的存在有何意義? 半導體器件往往由襯底和外延層組成,這兩個部分在制造過程中起著重要的作用,并且在器件的性能和功能方面具有重要意義。 首先,襯底是半導體

2023-11-22 17:21:28 1513

1513 外延工藝的介紹,單晶和多晶以及外延生長的方法介紹。

2023-11-30 18:18:16 878

878

碳化硅襯底有諸多缺陷無法直接加工,需要在其上經過外延工藝生長出特定單晶薄膜才能制作芯片晶圓,這層薄膜便是外延層。幾乎所有的碳化硅器件均在外延材料上實現,高質量的碳化硅同質外延材料是碳化硅器件研制的基礎,外延材料的性能直接決定了碳化硅器件性能的實現。

2023-12-15 09:45:53 607

607

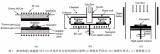

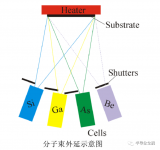

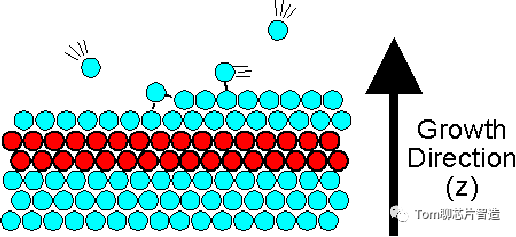

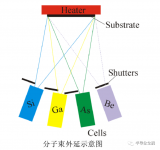

分子束外延(Molecular beam epitaxy,MBE)是一種在超高真空狀態下,進行材料外延技術,下圖為分子束外延的核心組成,包括受熱的襯底和釋放到襯底上的多種元素的分子束。

2024-01-15 18:12:10 963

963

只有體單晶材料難以滿足日益發展的各種半導體器件制作的需要。因此,1959年末開發了薄層單晶材料生長技外延生長。那外延技術到底對材料的進步有了什么具體的幫助呢?

2024-02-23 11:43:59 300

300

襯底(substrate)是由半導體單晶材料制造而成的晶圓片,襯底可以直接進入晶圓制造環節生產半導體器件,也可以進行外延工藝加工生產外延片。

2024-03-08 11:07:41 161

161

電子發燒友App

電子發燒友App

評論