您的位置:電子發燒友網 > 電子技術應用 > 行業新聞 > 國外電子 >

深入賽靈思Kintex-7 FPGA內部 - 深入賽靈思Kintex-7 FPGA內部:透視HKMG技術

2012年04月13日 16:09 來源:電子發燒友網原創 作者:電子大兵 我要評論(0)

深入賽靈思Kintex-7 FPGA內部

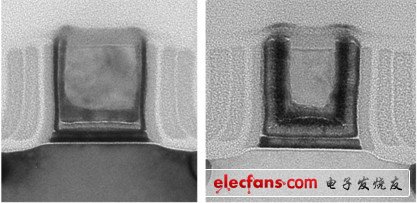

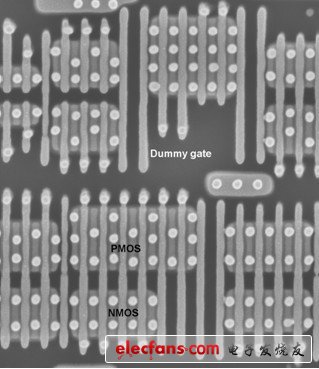

臺積電的HPL NMOS 和 PMOS晶體三極管在Kintex-7 FPGA中,如下圖所示。兩個晶體管被用作后柵極工藝,TiN/HfO2/oxide柵極絕緣層被堆積在第一層。

臺積電HPL NMOS (左) PMOS (右)

多晶硅被剝離,不同的金屬門被堆積到NMOS和PMOS門區域。

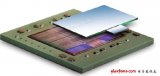

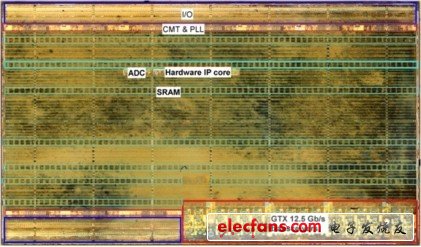

Kintec-7 FPGA門布局設計

高邏輯密度為Kintex-7 FPGAs設計的一大特色,內部設計為478,000個邏輯單元。其他特色包括:三十二個串行傳輸速度高達12.5 Gb/s高性能連接收發器,34Mb RAM和1,920 個DSP分割區,DSP性能高達2,845 GMACS以及16通道雙通道12位多相串行ADC。

——電子發燒友網版權所有,轉載請注明出處!

本文導航

- 第 1 頁:深入賽靈思Kintex-7 FPGA內部:透視HKMG技術

- 第 2 頁:深入賽靈思Kintex-7 FPGA內部