您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 行業(yè)新聞 > 國外電子 >

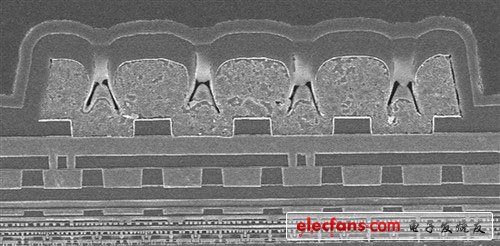

深入賽靈思Kintex-7 FPGA內(nèi)部:透視HKMG技術(shù)

2012年04月13日 16:09 來源:電子發(fā)燒友網(wǎng)原創(chuàng) 作者:電子大兵 我要評論(0)

電子發(fā)燒友網(wǎng)訊:終于逮到機會評估前沿高端新技術(shù)。在眾多的革新性工藝技術(shù)中,賽靈思和臺積電首次將高K金屬柵極(HKMG)技術(shù)應(yīng)用到FPGA中尤其是其中的佼佼者。現(xiàn)在就讓電子發(fā)燒友網(wǎng)帶領(lǐng)大家從賽靈思的工藝革新發(fā)展歷史到目前代表行業(yè)領(lǐng)域最高科技的Kintex-7 FPGA內(nèi)部架構(gòu),這是令人興奮的一次高科技之旅。

賽靈思的工藝革新史

賽靈思早在1984年就利用無晶圓商業(yè)模式制造出賽靈思首顆芯片,代工廠商為Seiko 和 Monolith。當(dāng)他們從65nm工藝節(jié)點轉(zhuǎn)入較低節(jié)點時,賽靈思和UMC, Samsung 及Toshiba 尋求合作生產(chǎn) FPGAs。直到現(xiàn)在,賽靈思采用臺積電的HKMG工藝不但用于領(lǐng)先的FPGAs的Kintex-7系列產(chǎn)品,也囊括了很多其他即將來臨的產(chǎn)品設(shè)備,包括Artix-7和 Virtex-7 FPGA系列和Zynq-7000 EPP系列。這一決定將賽靈思所有產(chǎn)品推向進入到28nm節(jié)點時代。

FPGAs 產(chǎn)品家族的Kintex-7系列采用了臺積電28nm高性能低功耗(HPL)工藝節(jié)點技術(shù)來進行設(shè)計封裝制造,為客戶提供低功耗和高性能體驗。它的市場戰(zhàn)略目標(biāo)為下一代廣播電視點播系統(tǒng)和下一代無線網(wǎng)絡(luò)等等應(yīng)用領(lǐng)域。

Kintex-7組件能被配置到支持多空中接口,如LTE, WiMAX, WCDMA以及為PCI Express (Gen1/Gen2)提供八通道內(nèi)置設(shè)計需求。Kintex-7 FPGA家族擁有領(lǐng)先的可擴展賽靈思架構(gòu),可對前一代產(chǎn)品(40-nm) Virtex-6 FPGAs進行簡便地移植使用。

談及到移植的問題,眾多的晶圓廠從65-nm節(jié)點的主要基于多晶硅門和應(yīng)變工程過渡到到高K金屬門柵極絕緣層,伴隨著技術(shù)難度的加大和高成本,每次過渡都充滿著潛在性危險。

回首HKMG工藝技術(shù),Intel憑借45-nm后柵極工藝最先進入到金屬門。臺積電是第二個晶圓代工廠能提供后柵極金屬門工藝的廠商。Intel的競爭者——AMD,直到現(xiàn)在才為其32-nm工藝節(jié)點引進后柵極金屬門工藝,據(jù)信,這是因為日本松下公司為其首次金屬門工藝采用金屬門重疊多硅結(jié)構(gòu)。

賽靈思選擇較為簡單的HKMG工藝降低來自高功耗(HP)或低功耗(LP)28nm工藝所帶來的風(fēng)險。選擇高性能,低功耗(HPL)HKMG技術(shù)可有效規(guī)避產(chǎn)量和漏電等異常事件發(fā)生。

選擇HPL方案,賽靈思可以更好的在進行FPGA設(shè)計時處理復(fù)雜和昂貴的靜態(tài)電源管理方案,使得能專注于開發(fā)具有統(tǒng)一標(biāo)準(zhǔn)的7 系列 FPGAs架構(gòu)(如Artix-7 和 Virtex-7)。這些統(tǒng)一的架構(gòu)為開發(fā)者帶來了許多好處,在FPGAs家族中不同的產(chǎn)品中可向上或向下移植兼容,客戶代碼和IP及普通模塊(RAM, DSP, I/O,時鐘,互連邏輯,存儲器接口)復(fù)用。

本文導(dǎo)航

- 第 1 頁:深入賽靈思Kintex-7 FPGA內(nèi)部:透視HKMG技術(shù)

- 第 2 頁:深入賽靈思Kintex-7 FPGA內(nèi)部