在人們的日常工作生活中,靜電放電(ESD)現象可謂無處不在,瞬間產生的上升時間低于納秒(ns)、持續時間可達數百納秒且高達數十安培的電流,會對手機、筆記本電腦等電子系統造成損傷。

對于電子系統設計人員而言,如果沒有采取適當的ESD保護措施,所設計的電子產品就會有遭到損傷的可能。因此,電子系統設計中的一項重要課題便是確保使其能夠承受ESD的沖擊,并繼續正常工作。

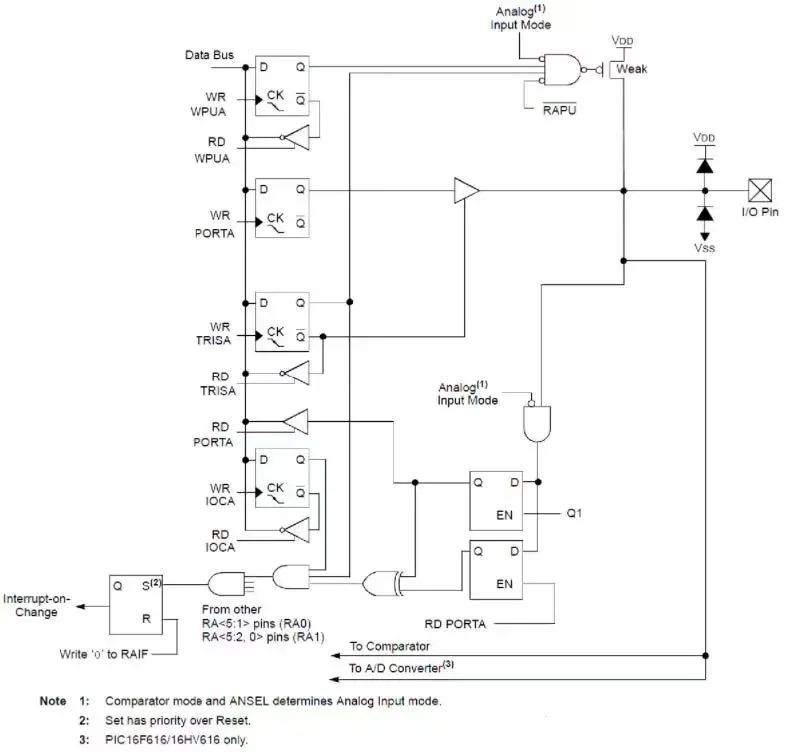

為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行內部2 kV等級的ESD保護所需要的面積。真正有效的ESD保護是不能完全集成到CMOS芯片之中的!

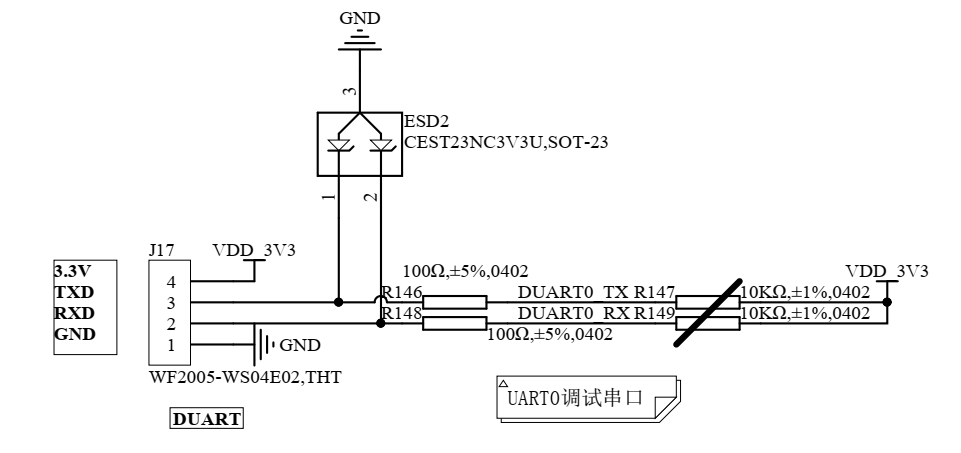

其次,也可以在物理電路設計方面下功夫,較敏感的電路元件應該盡量遠離通孔或接縫處,如果可能的話,線纜連接器的接地應該要在系統信號引腳接觸前先連接到系統的接地,通過這樣的方式,線纜上所發生的放電事件就比較不會造成干擾或破壞。

此外,軟件也能夠為ESD設計作出貢獻。系統連接的感測器比較容易受到ESD的沖擊,造成接口電路的鎖住情況,而能夠感測鎖住情況的軟件則可以用來重置接口電路且無須操作人員的接入。

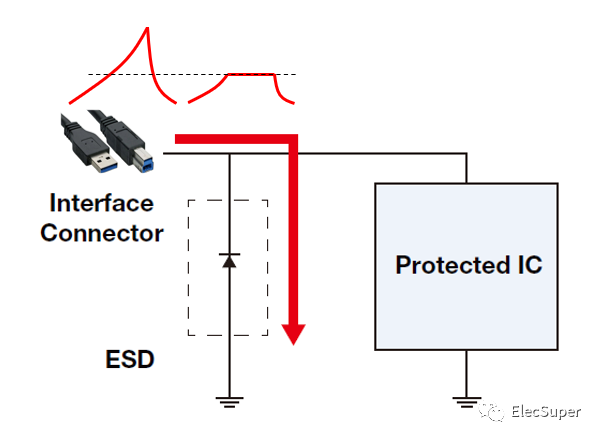

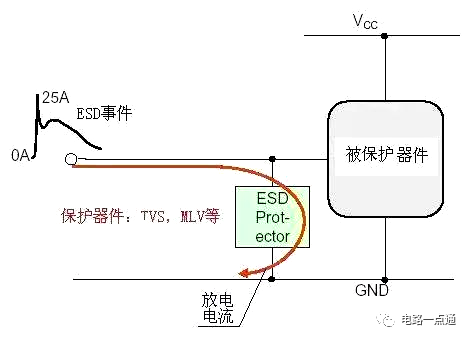

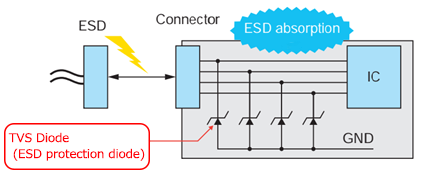

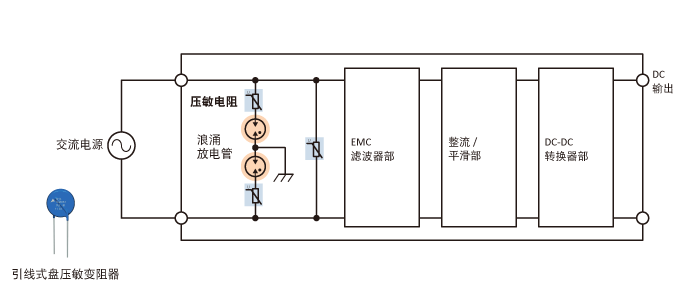

不過,總是有部分電路點較為敏感,同時也很難與外部隔離。因此,最有效的方法是使用保護元件來將電流導離較敏感的元件。也就是在電子系統的連接器或端口處放置ESD保護元件,使得電流流經保護元件,且不流經敏感元件,以維持敏感元件的低電壓,使其免受ESD應力影響,進入有效控制ESD事件的發生。當然,合格的ESD元件必須具有低泄漏和低電容,且在多重應力作用下功能不下降,從而不降低電路的功能。

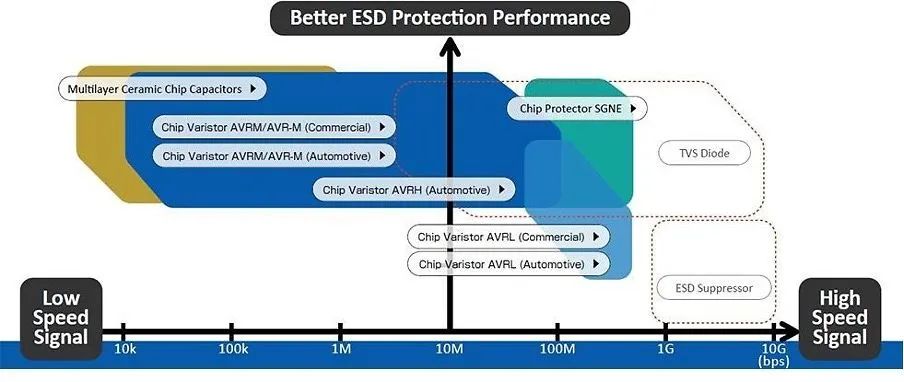

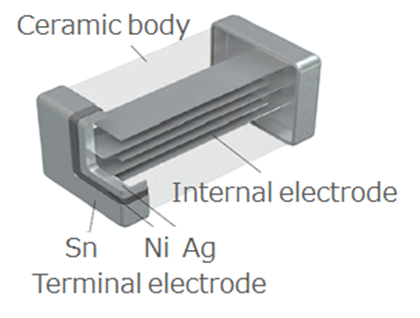

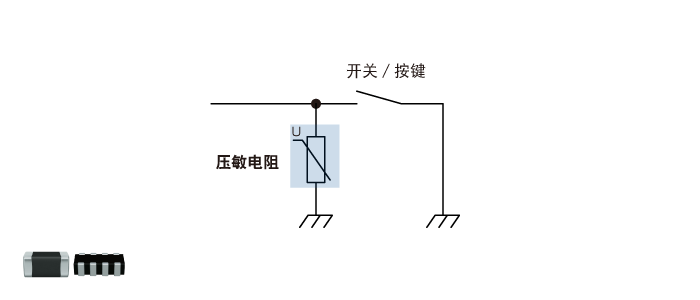

一般而言,ESD保護元件的分類可以通過其保護策略與方向性來進行,主要包括壓敏電阻、聚合物和瞬態電壓抑制器(TVS)等。在這幾種保護元件中,壓敏電阻在低電壓時,呈現出高電阻,其中的每個小型二極管兩端的電壓都相當低,同時電流也相當小;而在較高電壓時,其中的獨立二極管開始導通,同時壓敏電阻的電阻會下降。而對于帶導電粒子的聚合物而言,在正常電壓下,這些材料擁有相當高的電阻,但當發生ESD沖擊時,導電粒子間的小間隙會成為突波音隙陣列,從而帶來低電阻路徑。

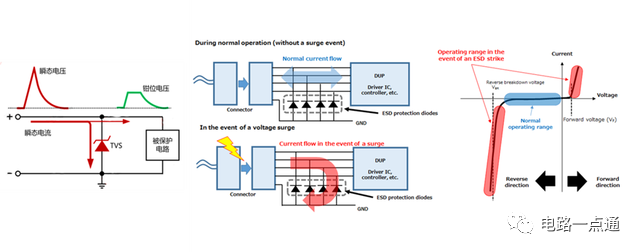

瞬態電壓抑制器(TVS)則為采用標準與齊納二極管特性設計的硅芯片元件。TVS元件主要針對能夠以低動態電阻承載大電流的要求進行優化,由于TVS元件通常采用集成電路(IC)方式生產,因此我們可以看到各種各樣的單向、雙向及以陣列方式排列的單芯片產品。

利用屏幕截圖和TLP進行ESD保護元件的大電流性能鑒定Ashton博士說在正常工作條件下,ESD保護元件應該保持在不動作狀態,同時不會對電子系統的功能造成任何影響,這可以通過維持低電流以及足以在特定數據傳輸速率下維持數據完整性的低電容值來達成。而在ESD應力沖擊或者說大電流沖擊條件下,ESD保護元件的第一個要求就是必須能夠正常工作,要有夠低的電阻以便能夠限制受保護點的電壓;其次,必須能夠快速動作,這樣才能使上升時間低于納秒的ESD沖擊上升時間。

眾所周知,對于電子系統而言,它必須能夠在IEC 61000-4-2標準測試條件下存續。雖然大部分的ESD保護元件都宣稱能夠承受IEC 61000-4-2所指定的應力沖擊等級,如8 kV或第四級(Class 4),但業界卻沒有公認的ESD保護元件大電流抑制特性測試的合格標準。對此,雷卯電子給出了自己的定義,也就是在±10 kV應力電壓 (高于8 kV)測試下,被測器件仍然符合其數據表規范,且器件特性沒有顯著變化。

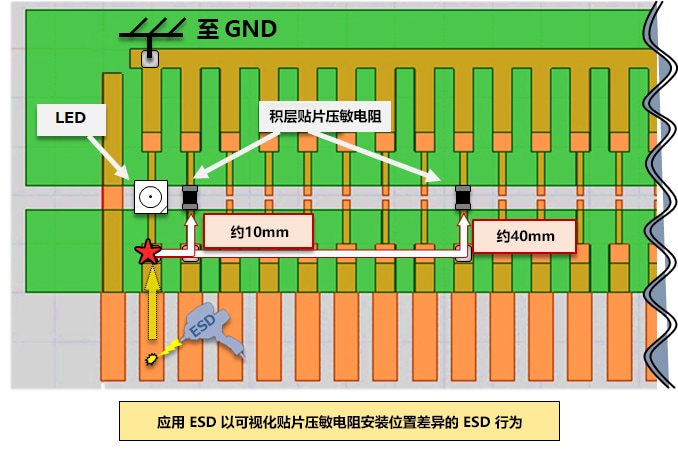

不過,要比較不同ESD保護元件的大電流抑制特性,還需要對其進行測試鑒定。而通過對不同ESD保護元件施加大電流沖擊所產生的波形的屏幕截圖對比,是重要的第一步。

半導體的TVS元件可以迅速將ESD應力降低,即從8 kV靜電電壓鉗位到5至6 V的水平;但壓敏電阻的曲線則下降得很慢,而且無法降到很低的水平。該曲線表明,TVS器件的恢復時間非常短,經過TVS器件泄漏到后面電路的能量也非常少,特別適合于便攜式設備的應用。

而在多重應力條件下,兩者的差別就表現得更為突出。由于TVS采用二極管工作原理,受到電擊后,會立即擊穿,然后關閉,對器件沒有損傷,因此可以說沒有壽命限制。對于壓敏電阻而言,它采用的是物理吸收原理,每經過一次ESD事件,材料就會受到一定的物理損傷,形成無法恢復的漏電通道;而且,要達到更好的吸收效果,就要使用更多的材料,使其體積增加,進而限制了在今天小型化產品當中的應用。

有鑒于此,雷卯電子打了一個比方,也就是在ESD保護方面,壓敏電阻保護施展的是“少林功夫”,用“身體(壓敏電阻)”去硬扛,會讓自己“很受傷”,而TVS耍的是“太極拳”,在ESD應力沖擊IC之前,就將沖擊力給“引導開”或“消減掉”。

兩相對比,其結果是在施加1,000次8kV IEC 61000-4-2 ESD脈沖條件下,半導體的TVS元件的漏電流小于0.1 μA,而壓敏電阻在少于20個ESD脈沖下漏電流就會超過100 μA。由此可見,在重復ESD應用作用下,TVS仍能維持極高的性能,而壓敏電阻的性能會隨之下降,聚合物也面臨著跟壓敏電阻類似的問題。

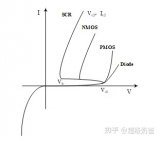

不過,用示波器對不同保護元件在ESD應力沖擊測試下的大電流抑制特性或者說是I-V曲線進行屏幕截圖對比也存在不足之處。首先便是這種屏幕截圖上的V(t)與I(t)的變化非常復雜,且并不能測量擊穿電壓、維持電壓、維持電流以及二次擊穿電流等基礎參數,而通過對這些參數的分析可以找到電路設計和工藝的弱點。

在這種情況下,采用傳輸線路脈沖(TLP)方法就是很好的下一步。所謂的TLP測試,就是一種利用矩形短脈沖(50~200 ns)來測量ESD保護元件的電流-電壓特性曲線的方法。這個短脈沖用來模擬作用于保護元件的短ESD脈沖,而恒定阻抗的傳輸線路可以生成恒定幅度的方波。TLP測試通過方波測試脈沖加到待測器件(DUT)的兩個引腳之間進行測試。TLP測試前要先對電路中的傳輸線路充電,測試時將被測器件接入,傳輸線路通過被測器件放電。改變電路和輸入電壓和傳輸線路的長度可以模擬在不同能量中的ESD脈沖,從而得到器件的ESD大電流抑制能力。TLP測試先從小電壓脈沖開始,隨后連續增加直到獲得足夠多的數據點,以作出完整的I-V曲線。通常測試脈沖的幅度會加大到使DUT徹底損傷為止,作而獲得其精確的允許最大脈沖電流。

總的來看,ESD保護元件的TLP測試方法優勢突出,不僅可以確認屏幕截圖數據,還可用于解析ESD保護元件的基礎參數,非常適用于對不同保護元件進行對比。

結合ESD脈沖測試和TLP測試,我們可以得出結論,在不同ESD保護元件中,TVS元件,特別是半導體的TVS元件的大電流導電率極佳,且在重復應力條件下仍能維持優異性能,不存在壓敏電阻或聚合物那樣的使用增多后會出現性能下降的問題;至于其在電容方面的不足,也隨著新的低電容設計的出現,而消除了早前的大電容問題。

fqj

電子發燒友App

電子發燒友App

評論