眾所周知,靜電放電(ESD)會對集成電路(IC)造成破壞性的能量沖擊,許多設計功能會影響到器件的ESD性能。本應用筆記討論了幾種保護IC免遭ESD破壞的電路設計方案。

概述

靜電放電(ESD)會對集成電路(IC)造成破壞性的能量沖擊,良好的IC設計能夠在IC裝配到應用電路的過程中保護IC免遭ESD沖擊的破壞。安裝后,IC還必須能夠承受ESD穿過靜電防護電路進入最終電路的沖擊。除此之外,機械防護、電源去耦電容都有助于提高ESD保護能力,但是,如果電容選擇不當將會造成IC更容易損壞。為了給IC提供合理的ESD保護,需要考慮以下內容。

沖擊IC的ESD傳遞模式

內部ESD保護

應用電路與IC內部ESD保護的相互配合

修改應用電路提高IC的ESD保護能力

ESD傳遞模式

靜電放電強度以電壓形式表示,該電壓由電容的儲能電荷產生,最終傳遞到IC。作用到IC的電壓和電流強度與IC和ESD源之間的阻抗有關。對電荷來源進行評估后建立了ESD測試模型。

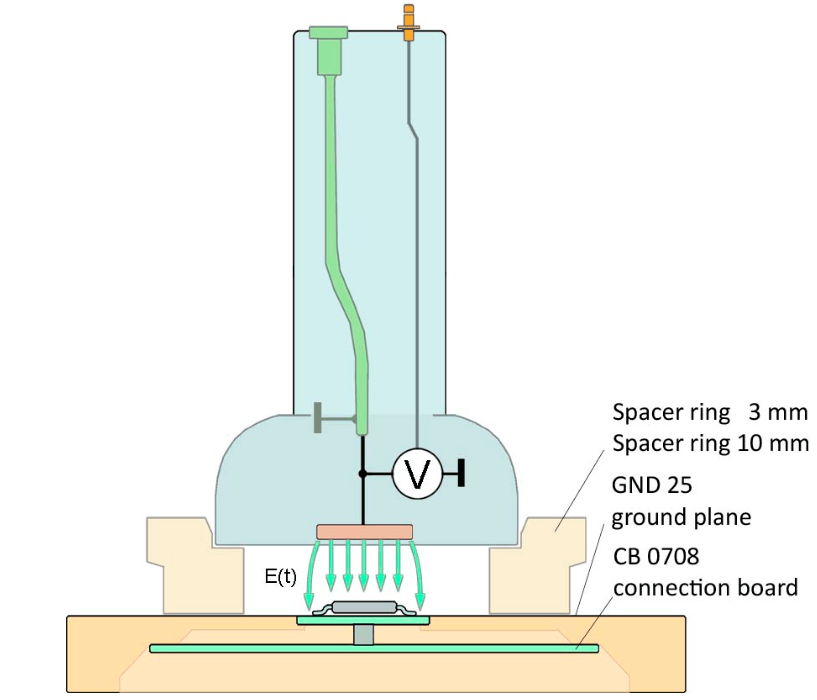

ESD測試中一般使用兩種充電模式(圖1),人體模式(HBM)下將電荷儲存在人體內(100pF等效電容),通過人體皮膚放電(1.5kΩ等效電阻)。機器模式(MM)下將電荷儲存在金屬物體,機器模式中的放電只受內部連接電感的限制。

圖1. ESD測試模型

以下概念對于評估ESD向IC的傳遞非常有用:

電壓高于標稱電源電壓時,IC阻抗較低。

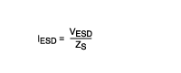

對于圖1中的HBM模式:ZS = ZHBM = 1.5kΩ

在MM模式下,電流受特征阻抗(約50Ω)的限制。

上述特征阻抗的計算可以從低阻L-C電路的能量(E)推導出來:

如果ESD電流主要流入電源去耦電容,IC電壓由儲存的電荷量決定:

Q = C x V和QFinal = QInitial

V1 x (C0 + C1) = VESD x C0 (見圖1)

能夠在瞬間導致IC損壞的能量相當于微焦級,有外部電源去耦電容時,考慮這一點非常重要,圖1中從電源電容(C1)傳遞到IC的能量是:

耗散功率(P)會產生一定熱量,假設能量經過一段較長的時間(t)釋放掉,熱量將隨之降低:

ESD能量傳遞到低阻電路時需要考慮其電流(上述第1、2條);對于高阻而言,能量以電壓形式通過電荷轉移傳遞到電源去耦電容和寄生電容(第3條)。對IC造成損壞的典型能量是在不到一個毫秒的時間內將微焦級能量釋放到IC (第4、5條)。

IC內部保護電路

標準保護方案是限制到達IC核心電路的電壓和電流。圖1所示保護器件包括:

ESD二極管—在信號引腳與電源或地之間提供一個低阻通道,與極性有關。

電源箝位—連接在電源之間,正常供電條件下不汲取電流,出現ESD沖擊時呈低阻。

ESD二極管

如果對IC引腳進行HBM測試,測試電路的初始電壓是2kV,通過ESD二極管的電流約為1.33A (圖2):

圖2. ESD二極管的電流和電壓(測量數據)

理論上,進行HBM測試時引腳電壓受限于二極管壓降。大電流會在ESD二極管和引線上產生I-R壓降,在信號引腳產生額外的電壓,如圖2所示。

為了確定IC是否能夠承受2kV的ESD沖擊,需要參考廠商提供的資料。IC的額定電壓由最大電壓決定,圖1中的VESD,這是IC能夠承受的一種特定的ESD源。Maxim IC所能承受的ESD指標在可靠性報告中可以查找到。

電源箝位

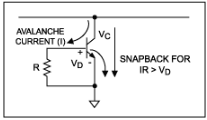

雙極型IC的箝位電路類似于在受保護核電路中提供一個受沖擊時擊穿的部件,圖3給出了圖1中箝位功能的詳細電路。箝位晶體管的過壓導致集電極-基極之間的雪崩電流,發射結的正向偏置會進一步提高集電極電流,導致一個“突變”過程。箝位時的V-I特性曲線如圖4所示。

圖3. 圖1中的箝位電路

圖4. V-I箝位特性

箝位二極管在IC其它電路遭到破壞之前導通,箝位管要有足夠的承受力,保證ESD電流不會導致二次擊穿。2kV HBM測試的箝位過程如圖5所示,圖5中的電壓包括I-R壓降和突變穩定后的箝位電壓。

圖5. 箝位工作過程(測量數據)

ESD保護與應用電路

箝位電壓從第一次擊穿變化到突變穩定后的導通電壓,如圖5所示。為保證箝位時關閉正常的工作條件,設計的箝位電壓一般要略高于IC的絕對最大電壓。

電源去耦電容會影響箝位操作,傳遞到去耦電容的電荷會產生高于IC絕對最大值的電壓,但還不足以使箝位電路導通。這時的電容相當于一個能源,迅速向器件注入能量。

對于一個給定的去耦電容,ESD測試中初始電壓的變化遵循電荷守恒原理。例如,使用一個0.01μF去耦電容,2kV HBM測試電壓可以達到20V:

或

圖6. 能量和電壓與電源耦合電容的關系

被保護引腳電容上的能量如圖6所示,對小的去耦電容,箝位二極管通過進入突變穩定模式限制電壓(V1)。突變穩定后的電壓所產生的能量近似地隨著電容的增大而成比例增大。電源去耦電容增大到一定程度后,電荷傳輸不會產生導致箝位電路擊穿的電壓。

箝位電壓高于IC所能承受的電壓(典型值6V),低于二極管的擊穿電壓(約10V)時,對于存在去耦電容的情況,因為電容儲能可能導致某些問題。如果IC在沒有外部電路的情況下進行測試,引腳上作用10V電壓是可以接受的,對器件不會構成威脅。

改善ESD保護

合理選擇去耦電容的大小有助于在電路中提高IC的保護,降低電容儲能,使ESD電荷不會產生擊穿箝位電路的電壓。我們可以考慮圖1中C1>>C0的情況:

最初:

將C1加倍,則會導致:

電容加倍,能量降低一倍。

對于小尺寸高速雙極型IC,HBM測試中吸收的最大能量是1μJ;2kV人體模式下,如果電容小于0.02μF (圖6), 箝位二極管會產生動作。為了使去耦電容的能量低于1μJ,去耦電容有兩種選擇:要么容值大于0.05μF,要么小于0.005μF。當使用更高的測試電壓時,要按比例增大0.05μF電容的尺寸。

實際應用中,通常不允許使用更大的去耦電容。浪涌電流的要求會限制電容尺寸。如果不控制電壓擺率,唯一限制浪涌電流的途徑就是限制去耦電容的尺寸:

去耦電容與電源間的引線總是存在一定量的電感,通常也會接入一個濾波電感。這種配置下,最大浪涌電流取決于濾波電感與去耦電容的特征阻抗,這個阻抗(圖7中的Zo)類似于MM測試中的電流限制。

圖7. C1較大時的電源阻抗

通過限制浪涌電流,可以使用較大的濾波電容(C1);發生ESD沖擊時,使得作用在IC上的電壓低于器件允許的最大額定電壓。

改善ESD保護的有效途徑有:

使用更大的濾波電容,使最大ESD電壓低于IC引腳所能承受的絕對最大電壓。

使用小的濾波電容,使得箝位二極管在低能量時提供保護。

增大串聯電感限制大電容產生的浪涌電流。

增加外部箝位二極管,如圖8所示的齊納二極管,使ESD電壓低于器件所能承受的絕對最大電壓(圖9)。

圖8. 齊納ESD保護二極管

圖9. 利用齊納保護二極管改善箝位(測量數據)

結論

IC及其周邊元件需要承受突破應用電路鏡電防護層的ESD能量,電源的去耦電容可能是降低作用到IC上的ESD強度的一條低成本解決途徑,諸多設計因素會影響ESD性能,具體可以歸納為:

確定應用場合的測試電壓(VESD),典型值為2kV的HBM或100V MM模式。

檢查IC的可靠性報告,確認二極管、鉗位二極管和傳導路徑適合的測試電壓。Maxim的可靠性報告中提供了IC的相關信息。

當使用外部電容,如電源濾波電容(C1)時,需檢查其產生的電壓,這個電壓最終作用到IC上。

如果出現ESD沖擊時,電壓介于IC的最大額定電壓(典型值為6V)與擊穿電壓(典型值在8V至10V),可以考慮使用較大尺寸的電容來替代電源濾波的方案。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18103瀏覽量

253817 -

集成電路

+關注

關注

5411文章

11816瀏覽量

365625 -

ESD

+關注

關注

49文章

2226瀏覽量

174458

發布評論請先 登錄

相關推薦

集成電路繼電保護(基本電路,距離保護,高頻保護,發電機失磁保護,接地保護)

雙極型集成電路的特點有哪些?

如何設計ESD保護電路?

雙極型集成電路的ESD保護

什么是雙極型集成電路

集成電路分為哪幾類 集成電路分類介紹

集成電路分類有哪些

集成電路電磁兼容性及應對措施相關分析(三)—集成電路ESD 測試與分析

評論