多軟件平臺FIR數字濾波器的協同設計

2012年11月13日 14:53 來源:本站整理 作者:灰色天空 我要評論(0)

摘要:提出了利用多軟件平臺進行FIR數字濾波器的協同設計,改變了傳統的只用硬件電路設計的方法,將整個數字濾波系統的硬件設計趨于軟件化,采用Lattice公司的可編程模擬器件ispPAC20和Altera公司的FPGA設計架構整個FIR濾波器實驗系統。由于ispPAC20和FPGA器件的高度集成化以及結構的可重構、可編程,使開發人員隨時可重復配置滿足各種性能要求的濾波器系統,將整個系統變得更小型化、更易于升級維護且更靈活。

0 引言

1992年美國Lattice公司發明了在系統可編程技術,徹底改變了傳統數字電子技術系統的設計和實現方法,開創了數字系統設計的革命性時代。在1999年,LatTIce公司又推出了在系統可編程模擬電路,為電子設計自動化技術的應用開拓了更為廣闊的前景。

隨著信息科學和計算機技術的迅速發展,數字信號處理在20世紀末期得到了飛躍式的發展。在數字信號處理中數字濾波是重要的環節,經典數字濾波器從實現的網絡結構或者單脈沖響應長度分類,主要分為有限脈沖響應(FIR)和無限脈沖響應(IIR)兩大類;與HR濾波器相比FIR濾波器的計算工作量稍大,但是在保證幅度特性滿足技術要求的同時,很容易做到嚴格的線性相位特性。

1 系統的總體結構設計

由于數字信號處理是用數值運算的方式實現對信號的處理,因此,相對于模擬信號處理,數字信號的處理具有靈活性、高精度和高穩定性、便于大規模集成、而且可以實現模擬系統無法實現的諸多功能。

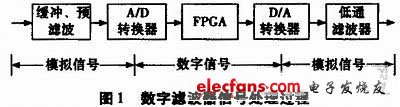

圖1所示為數字濾波器的信號處理過程。數字信號處理的對象諸如語音信號等它們本身也是模擬信號,所以一般先經過緩沖以及模擬信號預濾波,然后利用模-數轉換器(A/D轉換器)將模擬信號轉換成數字信號,再利用FPGA構成的FIR數字濾波器處理轉換后的信號。進一步利用數-模轉換器(D/A轉換器)將數字濾波器處理過的結果轉換為模擬信號供使用。

2 系統各部分功能的設計與實現

2.1 前端緩沖、預濾波以及模數轉換部分結構

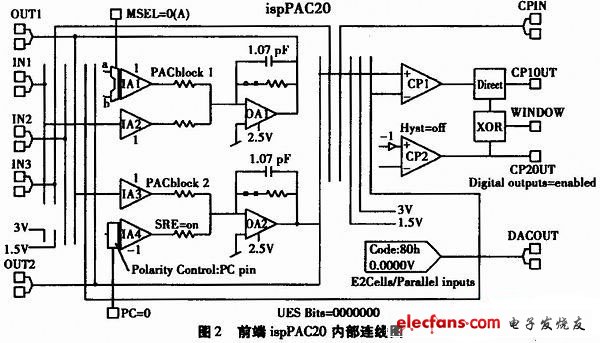

這部分的緩沖以及預濾波由ispPAC20來完成,然后利用FPGA以及ispPAC20中的D/A轉換器、比較器共同構成逐次逼近式A/D轉換器,其中ispPAC20中的電路結構圖如圖2所示。

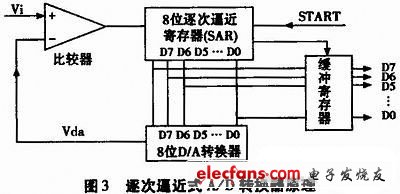

逐次逼近式A/D轉換器原理如圖3所示,當啟動信號START到來后,8位逐次逼近寄存器SAR(Successive ApproximariON Register)清零,轉換過程開始。第一個時鐘脈沖到來時,SAR最高位置1,其余位為0.SAR中鎖存的數據為10 000 000,經過DAC轉換后得到的輸出電壓Vda,與輸入電壓Vi進行比較,若Vi大于Vda,則SAR最高位的1被保留,否則清零。

第二個脈沖到來時,SAR次高位置1,所得的新值經過DAC轉換后得到的電壓Vda再與Vi進行比較,若Vda小于Vi則SAR次高位1被保留,否則清零。重復上述過程,依次類推,從D7~D0都比較完畢,轉換便結束,結束后SAR的數據輸出到輸出寄存器作為輸出數字量。從而經過ispPAC 20和FPGA共同完成從模擬量到數字量的轉換。

本文導航

- 第 1 頁:多軟件平臺FIR數字濾波器的協同設計

- 第 2 頁: 數字濾波部分

上周熱點文章排行榜

上周資料下載排行榜

創新實用技術專題

大家談:華為能否撬開美國市場?

熱評

- LM3S9B96開發板手冊及原理圖

- NI推出Single-Board RIO嵌入式介面

- STM32F103ZET6紅牛電路圖

- 高通發布全新設計DragonBoard板

- 3.15投訴:揭開天翼3G手機的“欺騙”

- 小米手機2工程機月底將上市

- protel99se正式漢化版免費下載

- 新款 Apple TV 將在3月8日出貨

- matlab 7.0軟件下載(免費破解版)

- hi3515海思原版原理圖

博文

- 新學習單片機,決心轉型技術宅

- 白巖松:青春該怎么過?不計后果的過

- 關于學電子的女生那點事

- 當你累了,準備放棄時,看看這個吧!!!

- 元芳,你怎么看cheer番茄

- 曬一曬“我的電子工程師之路”博文大賽【金獎】

- 模電基礎知識經典200問(上)

- 模電基礎知識經典200問(下)

- 大學那點事兒第二波:文科女生PK理科女生

- 菜鳥STM32初次制版

用戶評論

查看全部 條評論

查看全部 條評論>>