為了追求以更低功耗和成本實現更高性能的目標,超大規模集成電路產業向系統級芯片(SoC)集成方向發展,從而導致了多時鐘域設計的出現。最常見的是,當頻率關系是2的整數倍時,共享相同時鐘源的功能塊具有同步交互性。從時序的角度看,這些交互可能經常發生在設計的關鍵路徑。在這種情況下,你必須測試這些交互以查證過渡類型(transition-type)故障,以達到測試覆蓋率和DPPM(百萬分之一缺陷)目標。

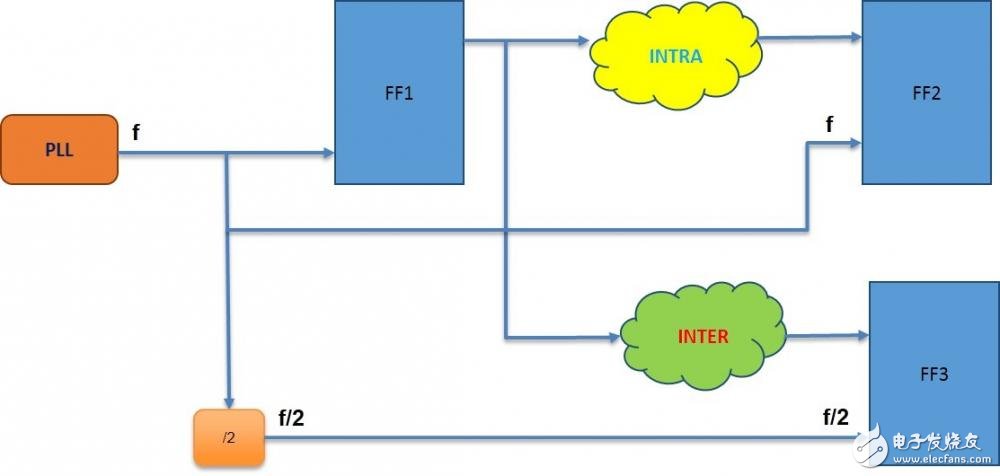

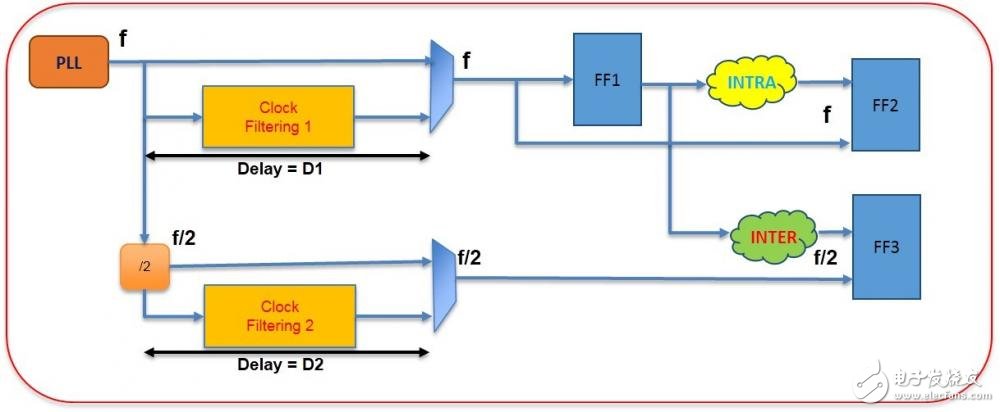

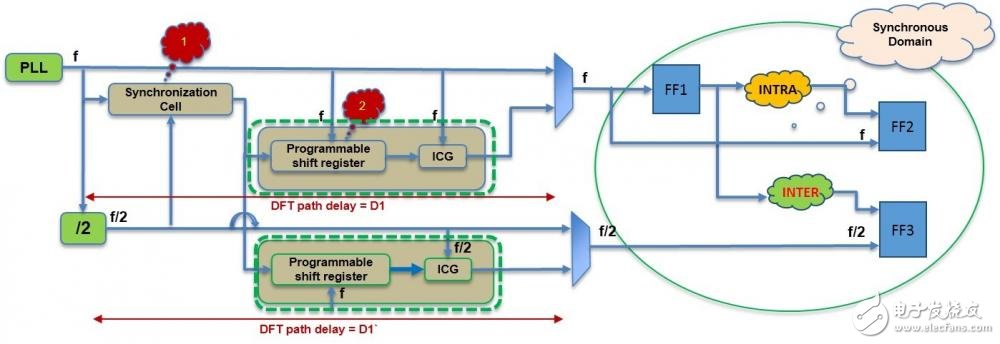

換句話說,在一個時鐘域中具有發射觸發器,并且在另一個同步時鐘域中具有捕獲觸發器的路徑被稱為同步跨時鐘域(SCCD)路徑。如圖1所示,FF1到FF2之間的組合云被稱為內部時鐘(intra-clock)域,而FF1到FF3之間的云被稱為跨時鐘(inter-clock)域。

圖1:內部時鐘域和跨時鐘域路徑可能會以延遲的形式引入故障。

用于過渡故障測試的時鐘濾波電路(CFC)從時鐘源濾除所需的時鐘脈沖。典型的CFC具有局限性,不能用于測試跨同步時鐘域的過渡故障。出現過渡錯誤時會出現什么問題?我們將解釋這些限制,并建議對CFC進行改進、以使對SCCD的測試(如圖1所示的跨時鐘域故障)可行。

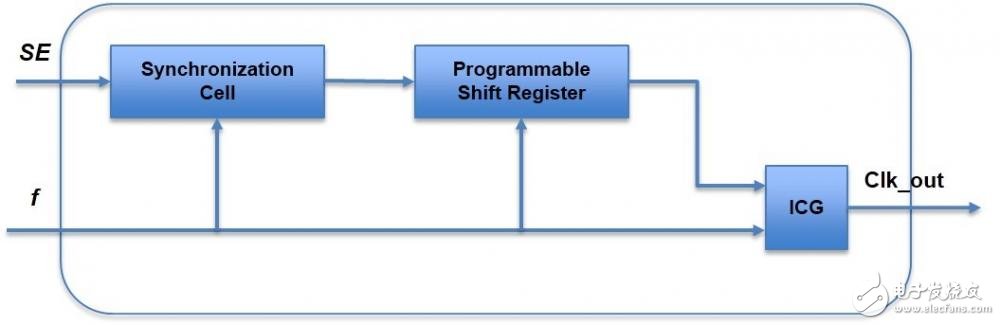

圖2表示一個典型的時鐘濾波電路,它有三個主要組件。

? 同步單元將掃描使能(SE)信號與工作時鐘域同步。

? 由同步SE信號觸發的可編程移位寄存器來控制集成時鐘門控(ICG)以生成所需數量的時鐘脈沖。

? ICG單元。

圖2:典型的時鐘濾波電路可能不足以測試跨同步時鐘域的時鐘故障。

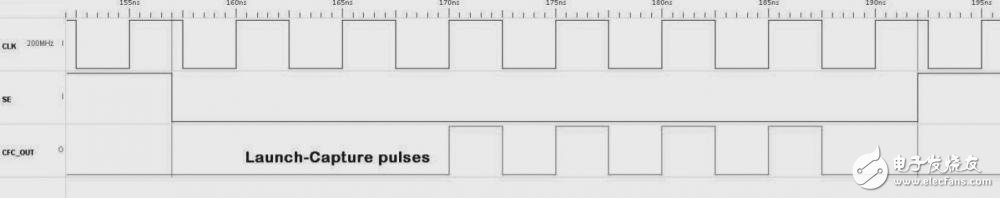

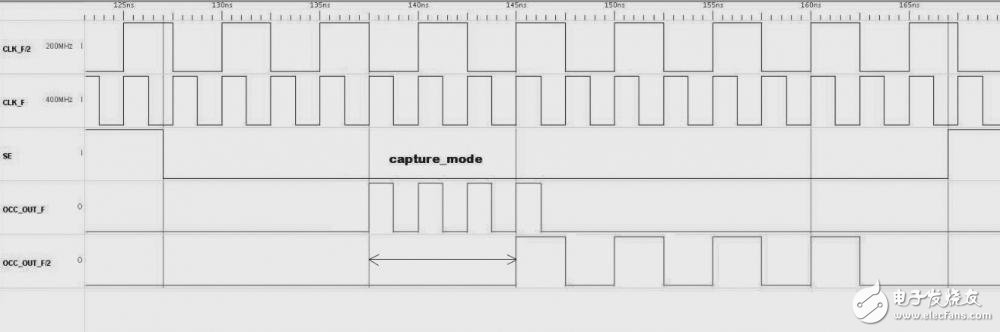

全速故障測試包括兩個步驟。第一步是移位模式,第二步是捕捉模式。在移位模式,當SE為高電平時,經由掃描鏈移位,寄存器被初始化為已知值。在捕捉模式,當SE為低時,功能路徑的響應被捕捉到寄存器中。

在捕捉模式,CFC用于產生所需的時鐘脈沖,用于全速測試的啟動和捕捉周期。

當SE被選通,經過一段延遲才到達CFC。然后在CFC中,與接收時鐘域的兩級同步單元同步。被SE同步的信號將觸發n級可編程寄存器給ICG提供使能信號,以濾除所需的時鐘脈沖。這意味著來自CFC的時鐘脈沖距離從SE到達CFC那一刻已有一定延遲。延遲主要由同步單元延遲造成。

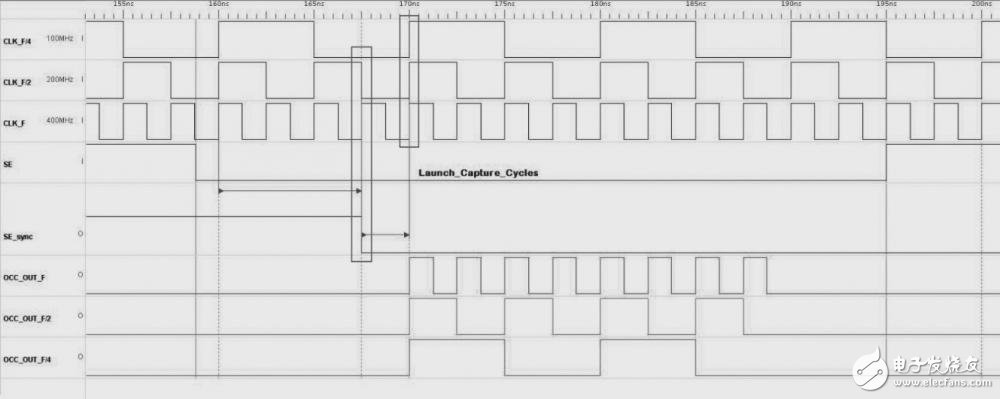

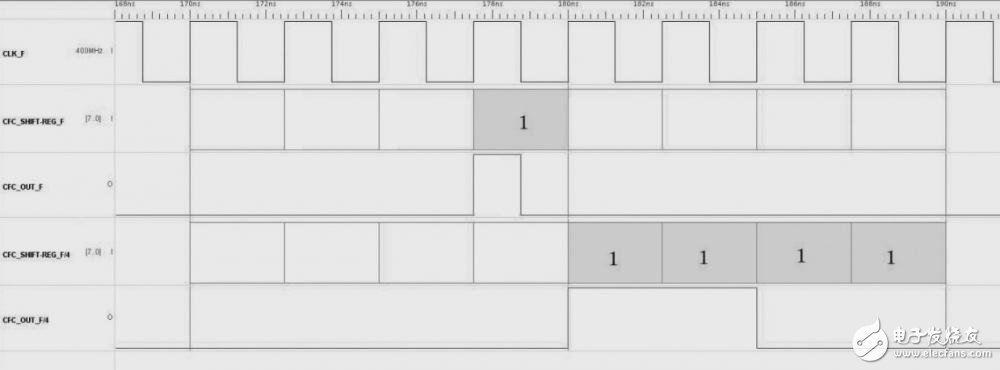

圖3:全速測試時鐘的典型CFC輸出波形。

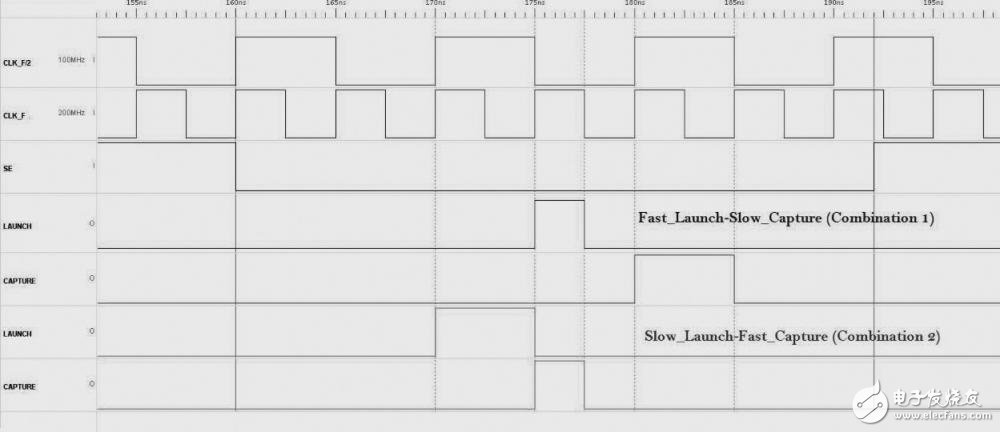

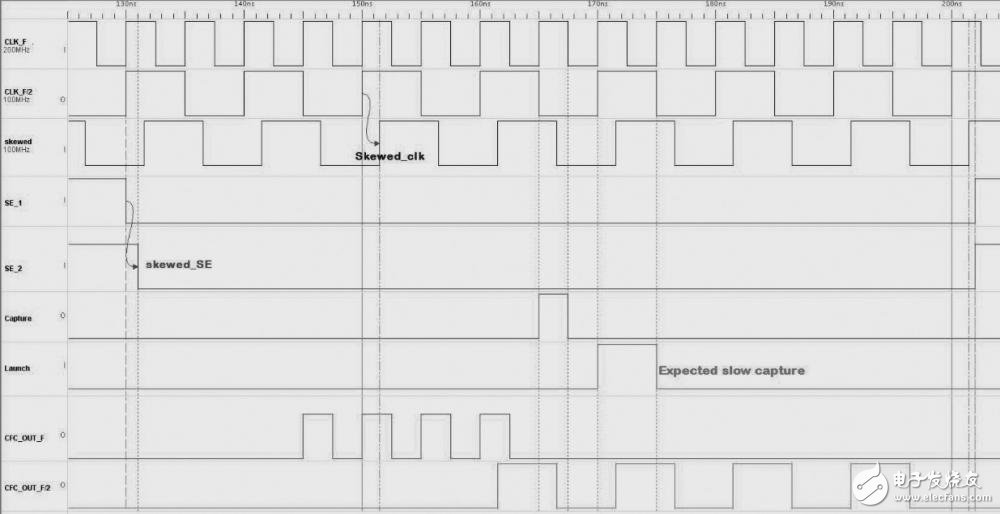

為測試時鐘域內的故障(內部時鐘域故障),該CFC盡職盡責,如圖3所示。但是,要測試SCCD過渡故障,需要產生啟動和捕獲脈沖,如圖4所示。為獲得這種波形,我們通常使用兩個獨立的CFC。每個時鐘域都需要自己的CFC,因為每個時鐘的脈沖寬度都不相同,因此需要從不同的CFC生成。圖4給出了你可以實現的不同啟動和捕獲條件的示例。

圖4:用于測試跨時鐘域故障的典型啟動和捕獲脈沖組合,包括快速啟動和慢速捕獲以及慢速啟動和快速捕獲脈沖。

當用于測試同步復時鐘域(圖1)中的故障時,同一個CFC遇到以下挑戰:

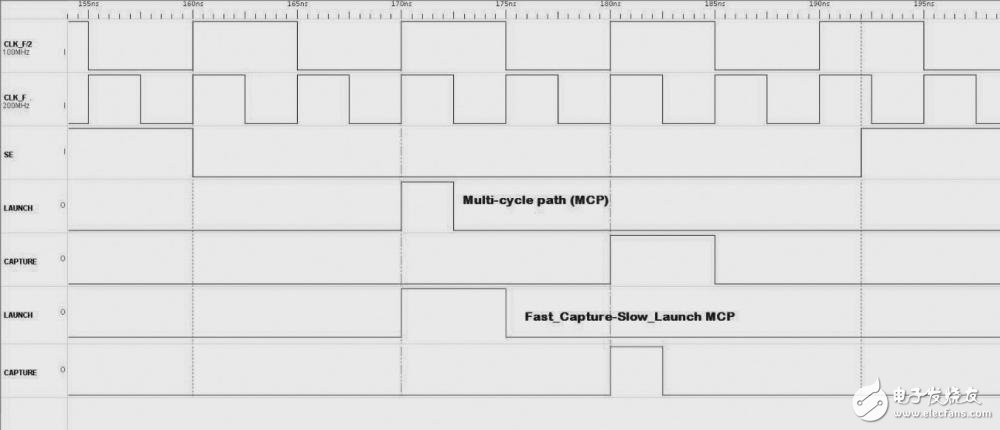

***邊緣失齊***:當測試兩個SCCD之間的故障時,每個時鐘域都有自己的CFC。而由于CFC固有的同步延遲會導致輸出錯位。產生的時鐘邊緣將不會是周期對齊的。例如,假定頻率為F和F/2的兩個同步時鐘,每個都具有移位寄存器長度為4的可編程CFC。可編程移位寄存器在不同時間被觸發,從而導致CFC輸出的不同延遲。假定為兩級同步器,則時鐘域F/2需要兩倍于時鐘域F的時間。圖5顯示了兩個CFC的時鐘輸出波形。需要注意的是,有兩種類型的錯位失齊。一種是由于同步本身的延遲,如圖5所示。

圖5:通用CFC輸出的時鐘波形,顯示失齊的邊沿。

失齊的另一個原因是時鐘偏斜(clock skew)。每個時鐘的偏斜都導致兩個CFC時鐘輸出失齊的進一步加劇。如圖6所示,CFC_OUT_F的輸出相對于CFC_OUT_F/2是偏斜的。正因為如此,捕獲發射信號的功能時序窗口被壓縮,損害了測試質量和有效性。

圖6:時鐘偏斜可導致邊緣失齊。

***丟失時鐘脈沖***:圖4顯示了在跨時鐘域故障的全速測試中所需的啟動和捕獲脈沖的子集。參考圖5,可以推斷,對于具有長度為4的可編程移位寄存器的CFC來說,它不能命中發射和捕獲脈沖的所有組合。例如,發射和捕獲脈沖的第一個組合(在圖4中)可以使用這兩個CFC來創建,但第二個組合不能。可通過增加移位寄存器的長度來解決該問題。

如圖4所示,為成功測試SCCD路徑,需要兩個啟動和捕捉脈沖組合。脈沖應該由時鐘時序窗口分開。但由于時鐘偏斜和同步單元延遲,這很難實現。

***多周期路徑(MCP)測試***:由于與時鐘脈沖丟失有關的問題,測試受移位寄存器長度的限制。移位寄存器的長度不足以捕獲所有的啟動和捕獲組合,并且這在MCP中變得更嚴重,因為你必須等待一個時鐘周期來脈啟(pulse)另一個。可編程的移位寄存器應該有足夠的寬度來創建所需的MCP啟動并捕獲脈沖和測試路徑。圖7顯示了MCP的兩種情況。同樣,對CFC來說,只有第一個條件是可能的,而第二個不行,因為它是基于通用CFC脈沖產生的。

圖7:多周期路徑需要足夠長的移位寄存器來產生有效啟動。

***物理實現和STA挑戰***:如圖8所示,D1和D2之間的延遲差異需要盡可能接近。小的差異確保兩個時鐘之間的時鐘偏斜在測試條件下與在功能條件下看到的時鐘偏斜相似。設計者應提供額外的物理和時序約束來實現小差異。例如,你可以使用SDC使能D1和D2路徑之間的時鐘平衡。

圖8:最小化D1和D2之間的差異以減少時鐘偏斜。

***范式生成***:即使對于可測條件,設計者也需要在可編程移位寄存器中找到正確的位序列來實施約束。基于這些值,CFC將為單周期路徑和多周期路徑生成正確的啟動和捕捉脈沖序列。

用于測試跨時鐘域過渡故障的時鐘濾波電路應確保以下幾點:

? 同步時鐘域的CFC應同時觸發,以產生對齊的時鐘脈沖。

? 電路應提供選擇所需精確脈沖對的靈活性,以實現啟動和捕獲的任意組合。

? 電路應該是時序友好和便于實現的。

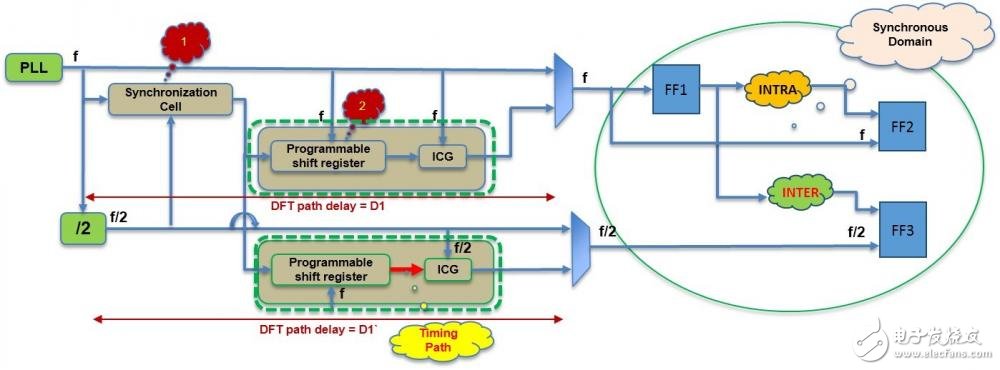

圖9顯示了我們在OpenSilicon中使用的一個修改后的CFC。

圖9:CFC修改包括可編程移位寄存器和一個分離同步單元。

***公用同步單元***:從CFC中取出同步單元,并與所有SCCD CFC公用。這樣做可以確保對可編程移位寄存器的觸發同時到達。單獨的單元消除了由于同步單元延遲差異而導致的邊緣失齊。

如圖10所示,要實現帶對齊上升沿的輸出時鐘脈沖,你應該在SCCD最快時鐘的前一個邊沿處生成同步SE。你可以通過同步單元中多個SCCD時鐘的組合來實現。為了以最小的邏輯來實現上面的對齊,在同步單元中使用最慢和最快的SCCD時鐘。

圖10:有效的SE同步沿產生所有SCCD時鐘的正確對齊。

***移位寄存器時鐘***:SCCD CFC的可編程移位寄存器被修改為以該SCCD的最快時鐘頻率工作。這在該SCCD的最快時鐘(f)和工作時鐘(f/2)之間創建了一條時序路徑,如圖11所凸顯。通過在時鐘樹綜合(CTS)階段嚴格地限制時鐘偏斜,該修改簡化了物理實現和靜態時序分析(STA)。它還使對物理實現和STA的額外限制不再必要。

圖11:SCCD時序路徑包含一個同步單元和可編程移位寄存器。

***移位寄存器寬度***:由于移位寄存器的工作頻率高于CFC的工作頻率,因此需要增加其寬度。例如,要產生四個f/2時鐘脈沖,移位寄存器的長度應為8,因為它工作在頻率f。移位寄存器的寬度取決于給定SCCD中最快時鐘與最慢時鐘頻率之比。下面的公式表示可改變移位寄存器寬度的參數:

例如,如果同步時鐘域的頻率為f、f/2和f/4,為最多實現四個時鐘脈沖,則移位寄存器寬度應該是:

因此,你需要一個以最快時鐘f工作的16位寬移位寄存器。

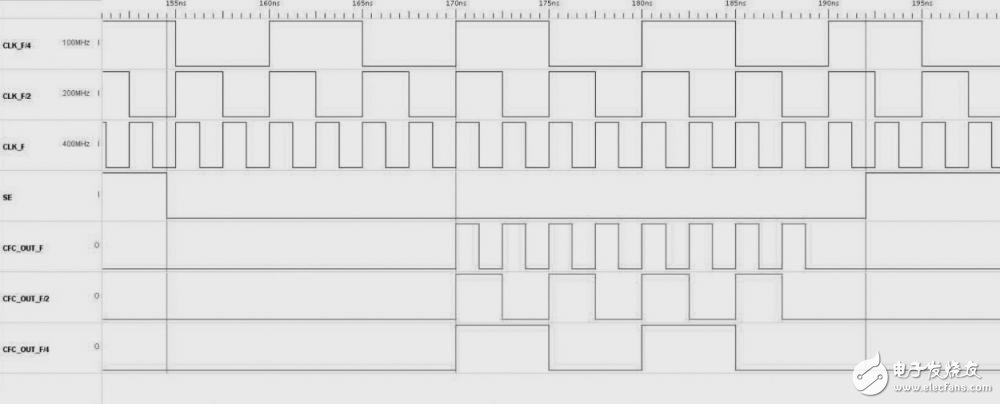

圖12描繪了F、F/2和F/4三個不同時鐘的SCCD CFC輸出時鐘脈沖。使用可編程移位寄存器,你可以配置CFC以生成所需的啟動和捕捉時鐘脈沖。

圖12:同步時鐘域中的CFC輸出顯示了所有時鐘沿都對齊、沒有任何延遲。

在圖5,我們表明,使用典型的CFC,不能產生用以測試跨時鐘域故障的啟動和捕獲時鐘脈沖的所有組合。使用增強型CFC,你可以生成所有可能的啟動和捕獲脈沖組合,包括MCP測試所需的組合。

***范式生成***:增強型CFC的范式生成涉及將移位寄存器的位編程為與所需的啟動和捕獲脈沖相對應的值。使用增強型CFC,可編程移位寄存器工作在最快的時鐘來獲得一個時鐘脈沖。因此,你需要約束移位寄存器內的多個位。

假定頻率為f/4的工作時鐘和頻率為f的可編程移位寄存器時鐘。需要對移位寄存器的四個位進行編程,以生成一個f/4工作時鐘頻率的脈沖(圖13)。此外,使用命名捕獲程序(NCP)自動測試范式生成(ATPG)方法來運行故障模擬。

圖13:兩個CFC的可編程移位寄存器位值可生成一個啟動和捕捉組合。

設計結果

在Open-Silicon,這種增強型CFC已經在設計中實現,實現了1.07%的全速覆蓋提升。雖然該數字本身可能看起來很小,但這些故障覆蓋了必須要測試的關鍵路徑。

結論

在包含多個時鐘的復雜SoC中測試SCCD故障并不容易,但對于提高良率非常重要。為克服這些挑戰,本文提出了一種修改現有CFC以實現更高覆蓋率的新方法。采用這種方法,可以在不影響任何設計進度和復雜性的前提下,只對原初的CFC進行微小更改、就實現了一款強健的CFC。測試這種同步跨時鐘域的故障可以讓設計人員實現更高的全速測試覆蓋率和低的DPPM目標。 這也有助于集成電路(IC)部件的篩選,并給速度分揀(speed binning)帶來額外好處。

電子發燒友App

電子發燒友App

評論