本資料的主要內容詳細介紹的說明15份描述CCD驅動的文獻資料合集免費下載,可以對CCD驅動的開發(fā)帶來幫助包括了:高精度線陣CCD的脈沖驅動與波形仿真基于51單片機的線陣CCD驅動設計,基于CPLD

2019-06-03 16:45:25

485集線器在總線型數(shù)據采集系統(tǒng)的應用是什么

2021-05-26 06:41:33

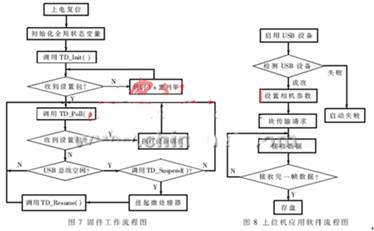

外接速率更高的外設,適合用于線陣CCD的數(shù)據采集。在USB2.0版本中,增加了一種高速模式,其數(shù)據傳輸率最高可以達到480Mb/s,完全可以滿足高速CCD數(shù)據采集系統(tǒng)的需要。2 接口硬件組成本系統(tǒng)選用高速

2018-12-03 15:18:20

請大家?guī)兔Γ蚁肜肈AQ編程數(shù)據采集系統(tǒng),并且利用數(shù)據庫存儲數(shù)據,請大家?guī)兔Γl有好的數(shù)據采集的實例請發(fā)一下編程vi至1538568180@qq.com。謝謝!

2015-03-13 20:23:14

最近在做線陣CCD的圖像顯示。CCD圖像信號已經成功采集,采集到的一行圖像數(shù)據緩存在FPGA內部RAM里面。現(xiàn)在想把多行圖像緩存在SDR SDRAM中,然后在VGA中顯示。SDRAM為海力士

2016-04-20 08:50:09

有沒哪位高手可以做線陣CCD測量開發(fā),可聯(lián)系。QQ:八五一五47九六九

2012-02-08 10:36:08

比如:紙張開卷過程中,紙邊會移動,我需要檢測紙邊的位置,便于糾偏。比較好的方式是用線陣CCD技術。是否有人做過類似的項目?

2014-05-06 13:18:51

本帖最后由 eehome 于 2013-1-5 09:47 編輯

線陣CCD驅動的幾種設計方法分享

2012-11-14 19:57:15

有木有做過線陣CCD驅動的,線陣CCD輸出經過AD轉換后,為什么被遮擋部分的輸出值大于光照區(qū)的值,不是應該相反嘛,求解答

2017-03-29 11:18:40

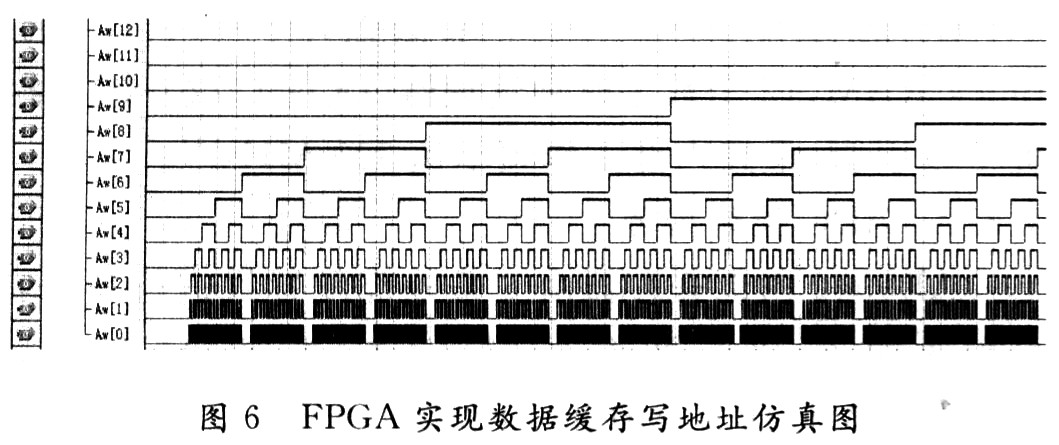

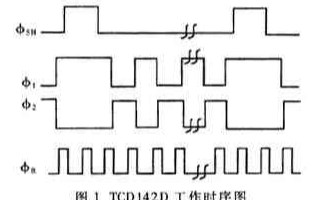

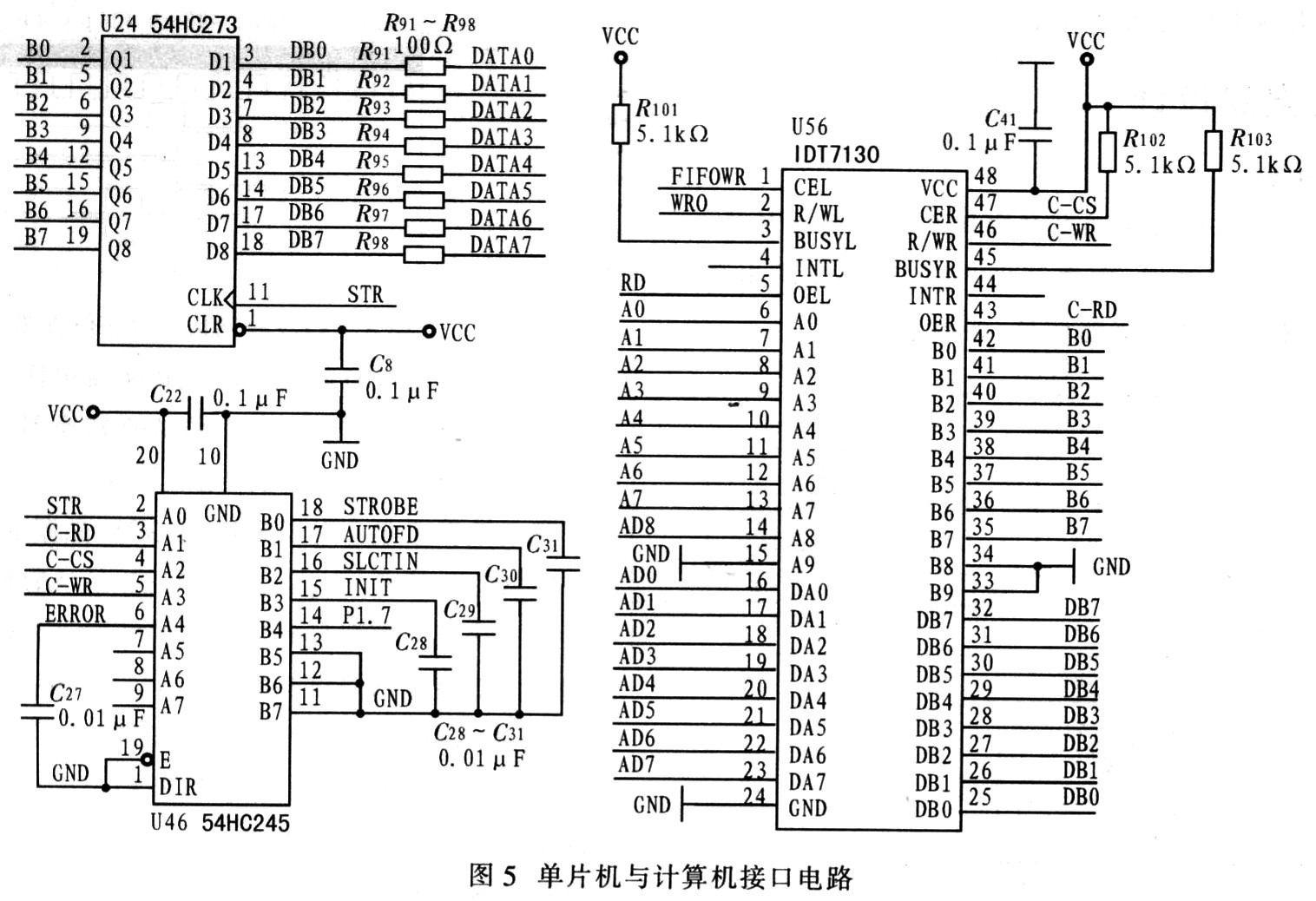

采樣的時序控制。最后,利用quartus7.2軟件平臺結合VHDL語言進行開發(fā),對所需驅動脈沖進行仿真設計。仿真結果表明,該驅動電路簡單、功耗小、成本低、抗干擾能力強,適用于設備小型化的要求。基于FPGA的線陣CCD驅動時序及模擬信號處理的設計.pdf

2020-09-01 14:50:25

LABVIEW開發(fā)汽車CAN總線數(shù)據采集系統(tǒng)

2012-08-20 19:25:45

單芯片12位數(shù)據采集系統(tǒng)

2023-03-28 18:28:42

單芯片12位數(shù)據采集系統(tǒng)

2023-03-23 07:59:40

TCD1304AP型號線陣CCD采集接收,由調理電路進行放大濾波處理輸送給A/D模數(shù)轉換器,將模擬信號轉換成數(shù)字信號,最后由PXI-6289采集到數(shù)據輸送給上位機,選擇LabVIEW接收數(shù)據、顯示及分析

2019-06-06 08:00:00

《基于ARM與線性CCD的高速數(shù)據采集系統(tǒng)》

2012-08-16 14:06:55

申請理由:本開發(fā)板為ARM系類,能移植Linux系統(tǒng),可以實現(xiàn)快速高效的系統(tǒng),并且能實現(xiàn)數(shù)據云共享。對于高速數(shù)據采集系統(tǒng),開發(fā)板的資源可以適用,并且非常實用。項目描述:高速數(shù)據采集系統(tǒng)原理:通過

2015-07-17 14:43:58

分享一款不錯的基于CPLD和ISA總線的數(shù)據采集系統(tǒng)設計

2021-05-06 09:53:44

各位大神,有沒有做過STM32驅動線陣CCD的啊?小弟求指教啊。

2014-05-12 16:22:41

TCD1304AP型號線陣CCD采集接收,由調理電路進行放大濾波處理輸送給A/D模數(shù)轉換器,將模擬信號轉換成數(shù)字信號,最后由PXI-6289采集到數(shù)據輸送給上位機,選擇LabVIEW接收數(shù)據、顯示及分析

2019-07-06 08:30:00

點擊學習>>《龍哥手把手教你學LabVIEW視覺設計》視頻教程摘 要:介紹了基于 PCI-6221DAQ 卡在LabVIEW 7 Express 開發(fā)環(huán)境下數(shù)據采集系統(tǒng)的開發(fā),證實了

2009-04-21 17:06:00

/模轉換器DAC0832構成一個數(shù)據采集系統(tǒng),并用CPLD/FPGA實現(xiàn)數(shù)據采樣、D/A轉換輸出、有關數(shù)據顯示的控制,單片機完成對A/D轉換數(shù)據運算。電路如圖1所示。系統(tǒng)功能如下:系統(tǒng)按一定速率采集輸入

2018-12-10 10:18:34

機交互軟件可以全自動地操作整個系統(tǒng),并對采集的數(shù)據進行分析、處理和一維模擬成像。 平行光通過單縫等光學元件時,會按照一定的光學規(guī)律分布,線陣CCD則能夠將一維的光信號轉化為模擬電信號,再通過一系列

2018-10-31 16:49:44

基于線陣CCD的尺寸測量裝置.pdf

2012-07-20 23:11:42

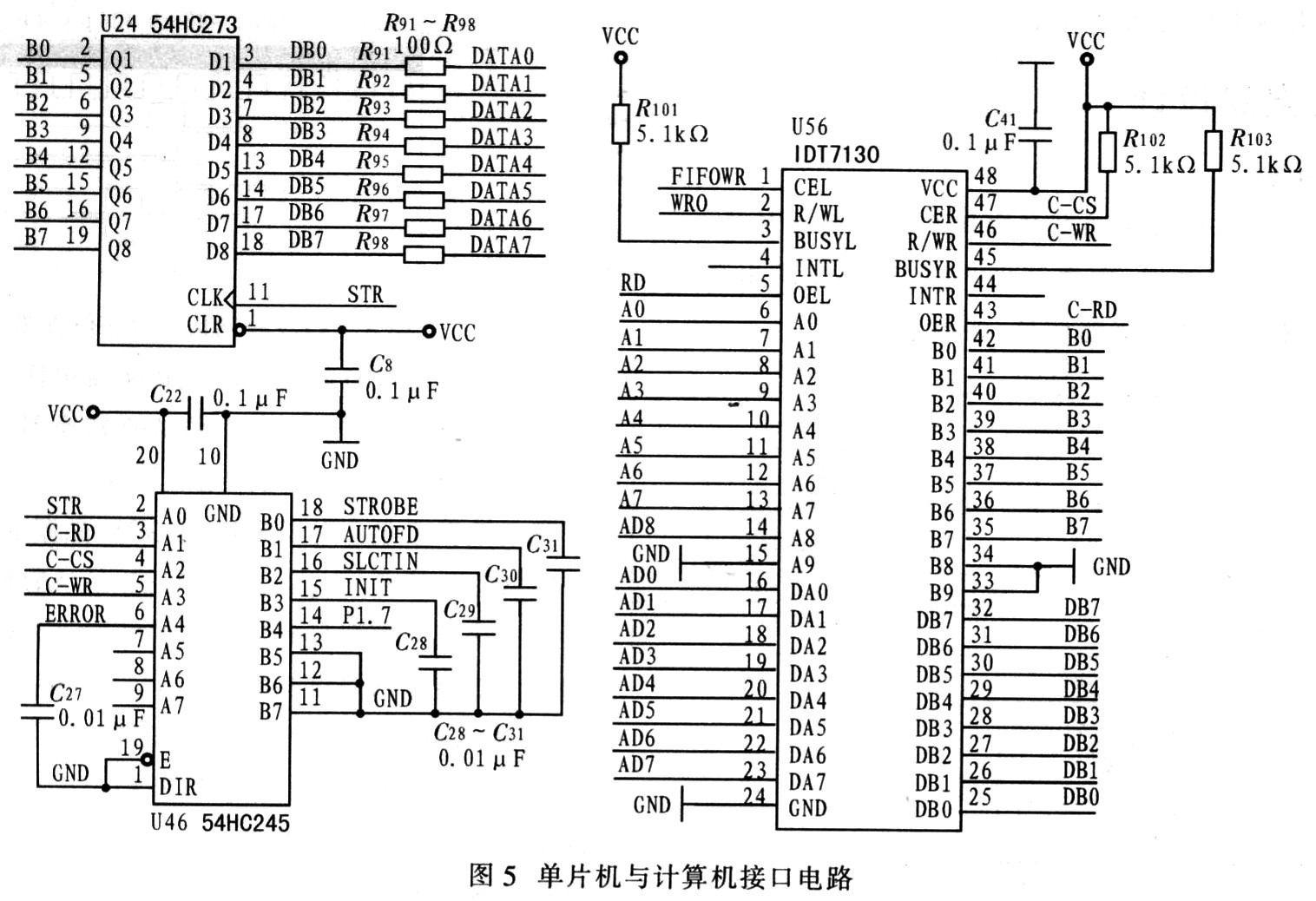

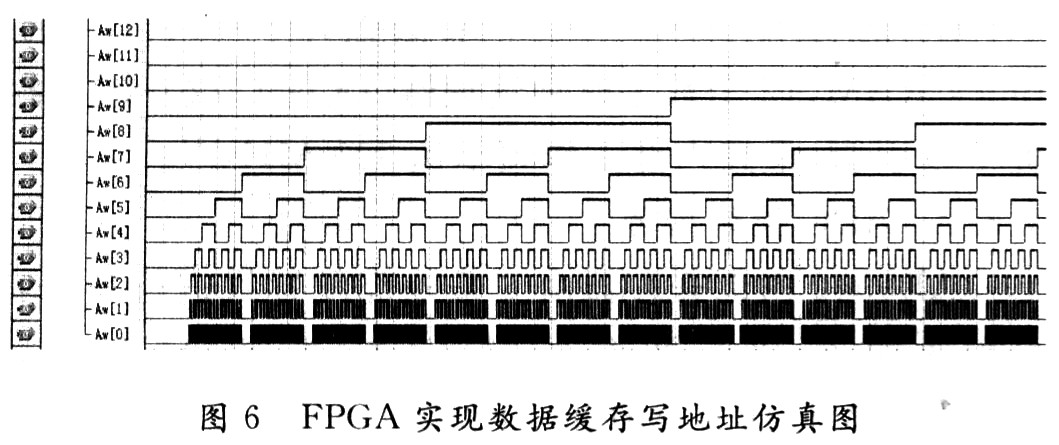

本文介紹了一個基于ARM的線性CCD高速采集系統(tǒng),系統(tǒng)中選擇了高速線性CCD和高速ADC,因為ADC的采祥速度相對ARM的工作時鐘頻率較慢,所以使用CPLD和FIFO作為A/D和ARM之間的1/0

2023-09-26 07:41:28

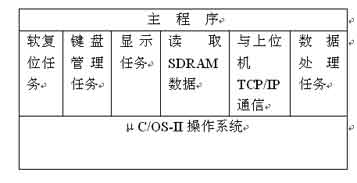

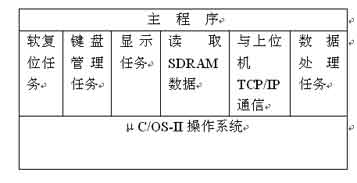

移動通信業(yè)務;綜合論述系統(tǒng)的要求和功能設計,并給出了系統(tǒng)整體構架;依據遠程數(shù)據采集系統(tǒng)的功能,對單片機系統(tǒng)進行了電路原理圖的設計,通過數(shù)據線連接單片機系統(tǒng)和G20 模塊串口,對其進行AT 指令控制,并設計軟件的流程框圖,用匯編語言編程。[hide][/hide]

2009-12-08 09:57:10

引言工程師在設計基于PC的數(shù)據采集系統(tǒng)時都認為,要想獲得比較好的性能,都需要使用PCI總線。其實并不是這樣,隨著USB通信技術的不斷發(fā)展,USB總線的傳輸速度和可靠性都在逐步提升。對于廣范

2019-06-11 05:00:06

基于USB數(shù)據采集系統(tǒng)的研究與設計--ResearchandDesignofDataAequisitio信息技術與電子技術的迅猛發(fā)展,使得計算機和外圍設備也得到飛速發(fā)展和應用,在科學研究領域和許多

2009-06-10 00:57:49

,分辨率等等。基于單片機的數(shù)據采集系統(tǒng)數(shù)據處理能力比較低,已經無法達到某些要求。科技的不斷創(chuàng)新及半導體工業(yè)的發(fā)展使得我們將可編程邏輯器件的技術應用到數(shù)據采集系統(tǒng)的研究上。同時利用CPLD 強大的數(shù)字

2021-07-20 06:23:22

本文設計一種基于CPLD的數(shù)據采集控制板。它能實現(xiàn)信號采集與控制、信號處理、通訊及輸出控制等功能。

2021-05-08 07:33:42

設計的基于CPLD與單片機的高速數(shù)據采集系統(tǒng)在QUARTUS II軟件中進行了仿真并達到了預期的控制邏輯。

2021-04-13 06:07:06

測井數(shù)據采集控制系統(tǒng)原理是什么?由哪些構成?數(shù)據采集有哪些方案設計?如何采用數(shù)據采集卡設計測井數(shù)據采集控制系統(tǒng)?

2021-04-13 06:25:12

EPP技術和CPLD技術介紹應用CPLD及EPP技術對CCD信號像素級的高速采集

2021-04-08 06:11:10

本文介紹了一種基于AD、CPLD、串行閃存來實現(xiàn)的小體積的數(shù)據采集系統(tǒng)。與其他數(shù)據采集系統(tǒng)相比,該系統(tǒng)體積小,存儲器便于控制,易于升級存儲器的容量,能夠滿足一般的信號采集。不足是系統(tǒng)的采樣頻率不夠高,只能達到250kHz/S,不適于高頻信號的采集。

2021-04-07 06:48:52

的通用性比較差。另一方面,早期數(shù)據采集系統(tǒng)多是基于復雜可編程邏輯器件(CPLD)設計的,數(shù)據的采樣速度和精度都不是很高。

2019-09-23 08:32:23

線陣CCD數(shù)據采集系統(tǒng)的特點有哪些?如何實現(xiàn)線陣CCD數(shù)據采集系統(tǒng)的硬件電路設計?如何實現(xiàn)線陣CCD數(shù)據采集系統(tǒng)軟件的設計?

2021-04-09 06:58:21

要制作一個無線數(shù)據采集系統(tǒng),要采集三種數(shù)據(溫度、濕度、光照;用的是DHT11模塊 和BH1750FVI),在lcd1602上顯示,并傳輸?shù)缴衔粰C,無線傳輸用到nFR24L01(+)模塊,請問stm32開發(fā)板用下面的可行嗎?

2017-03-10 15:37:29

求Labview采集線陣CCD數(shù)據的程序,我用的CCD是TCD1501C,類似的程序也參考一下啊

2016-10-10 20:26:55

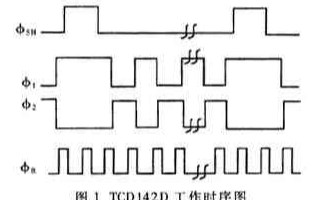

CD 1501D CCD工作參數(shù)及時序分析基于FPGA的線陣CCD驅動時序及模擬信號處理的設計

2021-04-22 06:13:19

高速數(shù)據采集系統(tǒng)的硬件結構MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據采集系統(tǒng)中的應用

2021-04-30 06:43:12

近年來,隨著可編程邏輯器件(CPLD/FPGA)的迅猛發(fā)展,可編程邏輯器件在數(shù)據采集、邏輯接口設計、電平接口轉換和高性能數(shù)字信號處理等領域取得越來越廣泛的應用。CPLD/FPGAD不僅可以解決電子系統(tǒng)

2020-03-05 06:20:45

的研究主要針對幀轉移型面陣CCD的驅動時序的實現(xiàn)方面,對行間轉移型面陣CCD驅動的研究很少,本文給出了行間轉移型面陣CCD數(shù)據采集系統(tǒng)完整的軟硬件設計。 1 面陣CCD圖像采集系統(tǒng)組成 整個系統(tǒng)

2018-11-15 16:27:46

數(shù)據采集系統(tǒng)是由哪些部分組成的?Blackfin及uClinux在數(shù)據采集系統(tǒng)中有哪些應用?數(shù)據采集系統(tǒng)該如何去設計?

2021-04-26 06:20:04

數(shù)據采集系統(tǒng)的特點數(shù)據采集系統(tǒng)的硬件電路設計數(shù)據采集系統(tǒng)軟件的設計

2021-04-30 06:44:55

基于AVR和CPLD的高速數(shù)據采集系統(tǒng)該怎樣去設計?

2021-04-29 06:59:21

采用PCI總線流水式高速數(shù)據采集系統(tǒng)設計摘要:目前基于PCI總線的高速數(shù)據采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能

2009-10-30 15:09:49

目前想做到的是CCD實時采集樣品的熱輻射,不太懂數(shù)據采集卡的原理。CCD是128*128的,采集到的數(shù)據是怎么樣的?如果放到labview用矩陣顯示,是一個128*128的不斷變化的數(shù)字矩陣?系統(tǒng)應該怎么連線?小白不是很懂這個應該怎么做?求大神給點思路。

2017-01-09 14:51:13

高速數(shù)據采集系統(tǒng)的硬件結構MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據采集系統(tǒng)中的應用

2021-04-08 06:11:56

快速變化的測量、 控制、 調節(jié)和自動化任務需要靈活的系統(tǒng)。 DASYLab數(shù)據采集(DAQ)助手提供了豐富的開發(fā)

2021-10-14 16:53:05

介紹了基于聲卡的數(shù)據采集系統(tǒng)的制作要點,運用labview開發(fā)系統(tǒng),在普通配備聲卡的計算機上,實現(xiàn)了單通道數(shù)據采集。

2008-08-06 22:14:07 156

156 measX eGAS數(shù)據采集系統(tǒng) 現(xiàn)代鉛酸電池的副反應是復雜的,特別是在動態(tài)條件下。但是,了解電池的性能和狀態(tài)對于目前具有啟停系統(tǒng)或微混合動力

2022-05-24 09:50:12

線陣CCD數(shù)據采集及LCD顯示 Linear Array CCD Data Acquisition and LCD Display

摘要:以TCD1200D為例,介紹了線陣CCD的一種通用高速數(shù)據采集方法,詳細介紹了電路組成、數(shù)據采集軟件實現(xiàn),

2009-01-11 12:08:46 45

45 數(shù)據采集在信號處理系統(tǒng)中占有重要的地位,它是聯(lián)系前端和后端的橋梁,數(shù)據采集系統(tǒng)的采集精度、穩(wěn)定性以及采集速度將直接影響到整個系統(tǒng)的性能。本文研究了整個基于總

2009-08-28 17:32:22 7

7 設計了以CPLD 為核心處理芯片的多路數(shù)據采集系統(tǒng),按照正確的時序直接控制AD676和雙端口RAM的工作, 所有這些功能都采用VHDL語言進行描述。關鍵詞:CPLD, AD676, VHDL語言, 雙端口R

2009-09-01 10:26:41 25

25 光強數(shù)據采集系統(tǒng)是一個與CCD 光電器件和微機技術結合使用的,專門用來采集一維光強變化分布的曲線圖樣數(shù)據的模/數(shù)轉換系統(tǒng)。它具有高靈敏度、低噪聲、快速讀出、高動態(tài)范圍

2009-09-18 10:09:37 44

44 本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高度表高速大容量數(shù)據采集存儲系統(tǒng),分析了系統(tǒng)組成和設計思想,著重對CPLD 實現(xiàn)的功能做了介紹并給出了代表信號

2009-09-18 11:09:30 11

11 本文針對新型匝間耐壓測試儀中需要高速采集數(shù)據的問題提出了一種結合CPLD 與單片機的高速數(shù)據采集系統(tǒng)設計方案。CPLD 產生A/D 芯片的控制時序以及SRAM 的讀寫控制時序,單片機輸

2009-12-23 14:59:57 88

88 基于計算機技術及虛擬儀器平臺LabWindows/CVI 開發(fā)了多通道實時數(shù)據采集系統(tǒng)。系統(tǒng)采用ACL-8112PG 數(shù)據采集卡作為數(shù)據采集硬件,與單通道數(shù)據采集相比,多通道數(shù)據采集需要解決

2009-12-31 15:10:06 79

79 基于CPLD 的雷達高度表高速大容量數(shù)據采集存儲系統(tǒng)設計作者:李貴新 袁嗣杰 轉貼自:微計算機信息摘 要:本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高

2010-01-27 14:18:26 22

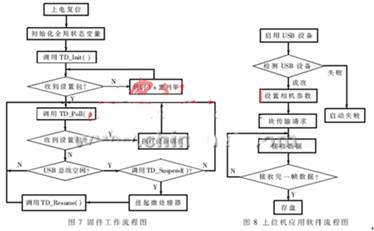

22 為了解決相機與電腦之間的數(shù)據傳輸問題# 設計了一種基于相機的高速數(shù)據采集系統(tǒng)#包括信號調理電路$%I$ 轉換電路和DEF 數(shù)據傳輸模塊等的設計利用PP 公司提供的開發(fā)包設計了固件

2010-07-02 14:48:49 49

49 本文對激光掃描車身坐標測量系統(tǒng)的數(shù)據采集部分進行了深入研究,設計了基于“AVR+FIFO+CPLD”的數(shù)據采集及處理模塊;解決了當多路信號有數(shù)據同時傳輸時,如何將數(shù)據完整地寫入F

2010-11-22 14:51:10 24

24 換體DMA高速數(shù)據采集電路的CPLD實現(xiàn)

介紹了換體DMA高速數(shù)據采集電路原理及其CPLD實現(xiàn)。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 666

666

CPLD在多路高速同步數(shù)據采集系統(tǒng)中的應用

CPLD(Complex Programmable Logic Device,復雜可編程邏輯器件)是在傳統(tǒng)的PAL、GAL基礎上發(fā)展而來的,具有多種工作方式

2009-03-28 16:49:00 767

767

數(shù)據采集系統(tǒng)是通過采樣電路將輸入的模擬信號轉換成離散信號,并送入CPU、MCU或DSP進行處理。現(xiàn)在流行的基于PCI總線設計的采集卡是數(shù)據采集系統(tǒng)的主流,其優(yōu)點是可以利用PCI

2009-04-19 10:52:31 817

817

設計了以CPLD為核心處理芯片的多路數(shù)據采集系統(tǒng),整個數(shù)據采集系統(tǒng)可實現(xiàn)最大采集頻率為800kHz,通道數(shù)為48路的模擬信號的采集。系統(tǒng)中采用了TI公司最新推出的高速低功耗A/D

2009-05-05 20:04:02 1666

1666

介紹了一種基于CPLD(復雜可編程邏輯器件)和FIFO(先入先出存儲器)的多通道高速A/D數(shù)據采集系統(tǒng)的設計方法,并給出了這種數(shù)據采集方法的硬件原理電路和主要的軟件設計思路

2009-05-05 20:50:09 1651

1651

摘要: 采用VHDL語言和圖形輸入設計方法,給出了用CPLD在遠程多路數(shù)據采集系統(tǒng)中實現(xiàn)地址譯碼、串口擴展、模塊測試、模數(shù)轉換以及高位數(shù)據處理等功能的具體方

2009-06-20 14:52:11 525

525

摘要:介紹了換體DMA高速數(shù)據采集電路原理及其CPLD實現(xiàn)。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積大、電路復雜、不能實現(xiàn)在線

2009-06-20 15:12:07 878

878

高速數(shù)據采集系統(tǒng)中精確時標的CPLD實現(xiàn)方法

本文介紹一種利用復雜可編程邏輯器件給高速數(shù)據采集系統(tǒng)中的采集數(shù)據貼上精確時間標簽的方法,并

2009-07-20 12:42:23 609

609 基于ADS8364的數(shù)據采集系統(tǒng)設計

開發(fā)了基于DSP和ADS8364的數(shù)據采集處理系統(tǒng)。該系統(tǒng)主要由信號調理模塊、A/D轉換模塊、DSP處理器模塊、CPLD邏輯控制模塊、Flash存儲器模

2009-09-19 09:30:20 1487

1487

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據采集系統(tǒng)的設計與實現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據采集系統(tǒng),并詳細闡述了系統(tǒng)的結構和軟硬件的實

2009-10-15 23:46:59 616

616

高幀頻CCD數(shù)據采集處理系統(tǒng)的設計

引 言 電荷耦合器件CCD(Charge Coupled Devices)可以將光信號的強弱轉化為勢阱中電荷量的多少,從而實現(xiàn)光電轉換。它在

2009-11-17 17:32:45 1160

1160

基于單片機和CPLD實時數(shù)據采集顯示系統(tǒng)設計

1 引言 數(shù)據采集是分析模擬信號量數(shù)據的有效方法。而實時顯示數(shù)據是自動化檢測系統(tǒng)的現(xiàn)實需求。在測

2009-12-22 17:31:02 1739

1739

基于CPLD/FPGA高速數(shù)據采集系統(tǒng)的設計

0 引 言 傳統(tǒng)的數(shù)據采集系統(tǒng)一般采用單片機,系統(tǒng)大多通過PCI總線完成數(shù)據的傳輸。其缺點是數(shù)學運算能力差;

2010-01-27 09:35:01 507

507

CCD相機的高速數(shù)據采集系統(tǒng)設計

CCD(Charge Couple Device)中文名為“電荷耦合器件”,是一種以電荷包的形式存儲和傳遞信息的半導體表面器件。由于CCD相機

2010-03-18 11:19:14 1483

1483

為實現(xiàn)尺寸較大、內部結構較為復雜的星載電子設備的多余物自動檢測,設計了以EZ-USB FX2和CPLD芯片為核心器件的數(shù)據采集卡,實現(xiàn)了四通道的同步數(shù)據采集和傳輸。此系統(tǒng)包括數(shù)據采

2011-03-21 10:54:38 0

0 介紹了基于 PCI-6221DAQ 卡在LabVIEW 7 Express 開發(fā)環(huán)境下數(shù)據采集系統(tǒng)的開發(fā),證實了LabVIEW 7 Express在開發(fā)數(shù)據采集系統(tǒng)方面的優(yōu)勢。

2011-05-23 11:38:05 49

49 CPLD在高速數(shù)據采集系統(tǒng)中的應用! 介紹了高速數(shù)據采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產品的特點及其開發(fā)軟件.CPLD根據高速數(shù)據采集系統(tǒng)的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 本文設計了一種基于CPLD(復雜可編程邏輯器件)+FX2(單片機CY7C68013)的便攜式高速數(shù)據采集系統(tǒng),采用了數(shù)據流驅動多模塊并行技術和USB2.0接口。實踐證明,該方案結構簡單,成本低廉

2012-05-25 09:53:19 1471

1471

本文提出了采用Xilinx公司生產的CPLD來對多通道旋轉編碼器進行數(shù)據采集的方法,著重介紹了系統(tǒng)的軟硬件設計和驅動程序開發(fā),以及實際應用情況,得出了用CPLD技術為多通道編碼器

2012-07-11 10:36:31 1224

1224 基于LabVIEW數(shù)據采集系統(tǒng)的快速開發(fā)。

2016-01-20 16:27:01 0

0 基于FPGA的新型高速CCD圖像數(shù)據采集系統(tǒng)

2016-09-22 13:05:38 22

22 基于CPLD高速數(shù)據采集系統(tǒng)設計_鮮果

2017-03-19 11:45:23 3

3 介紹了基于CPLD的線陣CCD數(shù)據采集系統(tǒng)的硬、軟件構成,工作原理及設計方案。采用TOSHIBA公司近年來推出的高速線陣CCD芯片TCD1209D,針對其驅動時序的要求,選用XILINX公司的復雜

2019-11-28 16:23:00 19

19 為了提高數(shù)據采集卡的速度,同時降低成本,設計一種并行數(shù)據采集系統(tǒng),要求并行采集速度大于10 Mb/s。整個系統(tǒng)由AVR與CPLD控制實現(xiàn),通過MAXl308完成模數(shù)轉換,并設計搭建了其外圍電路。采用

2020-07-20 17:17:02 11

11 線陣CCD(Charge Coupled Device)越來越廣泛地被應用到工業(yè)、軍事、民用行業(yè)。采用CCD數(shù)據采集卡和微機相結合,對被測圖像信息進行快速采樣、存儲及數(shù)據處理,是線陣CCD數(shù)據采集發(fā)展的新方向。配以適當?shù)墓鈱W系統(tǒng),可以實現(xiàn)光-機-電-算一體化設計。

2020-08-21 09:30:14 3760

3760

介紹一種基于Actel公司Fusion StartKit FPGA的線陣CCD圖像數(shù)據采集系統(tǒng)。以FPGA作為圖像數(shù)據的控制和處理核心,通過采用高速A/D、異步FIFO、UART以及電平轉換、放大

2021-02-02 17:12:32 5

5

電子發(fā)燒友App

電子發(fā)燒友App

評論