??? 關鍵詞:多通道,高速數據采集系統,CPLD,FIFO

1 引 言

隨著數字信號處理技術及各種故障分析技術的發展,以及單片機的運算速度的提高,在一些由單片機構成的較小系統中對信號進行實時處理(如諧波分析等)已經成為可能,且越來越受到人們的重視。這就要求作為最底層的數據采集系統,既要具有很高的采樣速率,又要能提供更豐富的原始數據信息。

常規采集方案為:(1)由單片機直接控制的采集方案,這是最簡單最常用的控制方案。由于每次采樣都要有單片機的參與,需占用單片機的時間,影響其數據處理,而且對于多通道、多個A/D轉換器的控制,因所需處理的信息更多,則更加不方便。(2)由DMA控制的采集方案。此方案硬件電路復雜,若與單片機配合使用,需要單片機具有總線掛起功能(Hold功能),否則還需要進行總線切換。在總線掛起的時候,單片機就不能訪問外部存儲器和外部端口,如果單片機要訪問外部數據,也只能等待總線的釋放,這樣就帶來很多不方便,也影響數據的及時處理。

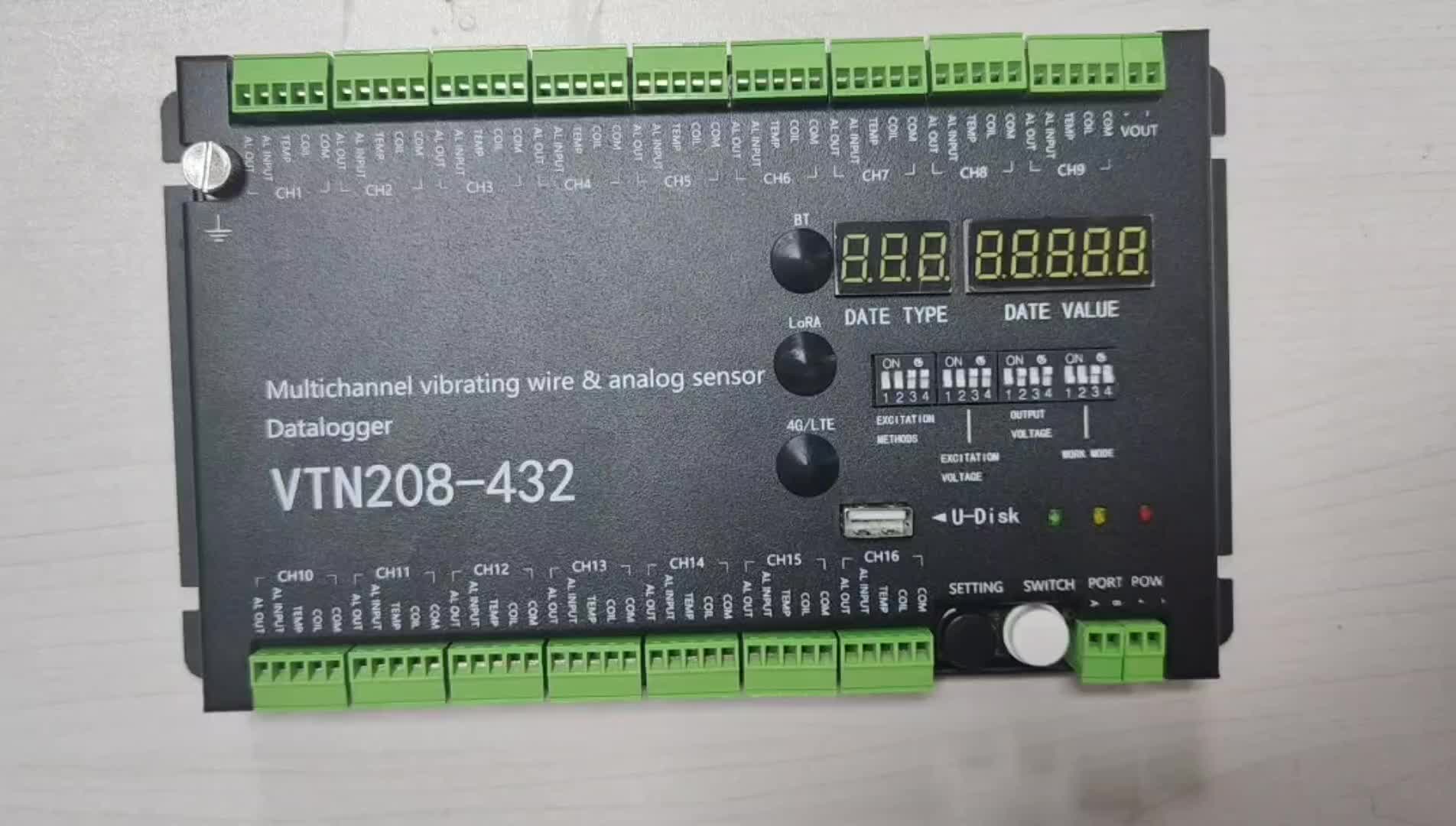

在電力系統的微機檢測系統中或者其他數據巡檢系統中,需要對多通道的數據作快速的采集分析,尤其是對于實時性很強的系統,更要求采集獲得的數據必須實時準確地反映系統的運行情況,例如,故障錄波和實時在線監測系統〔1〕〔2〕。本文提出了一種易與各種單片機系統接口的由純硬件電路控制的多通道高速數據采集系統。它的自動采樣硬件電路主要采用CPLD(Complex Programmable Logic Device)和FIFO(First In FirstOut)技術設計而成。該裝置可以實現多路模擬量的高速采集,每一個模數轉換器(ADC)可以采集10個通道的數據,并且多個模數轉換器件的輸出可以以總線形式進行擴展。

2 系統設計原理框圖和基本設計思想

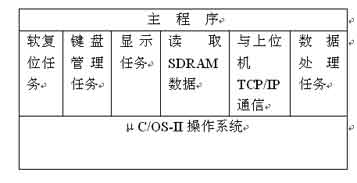

??? 多通道高速A/D數據采集系統的設計原理框圖如圖1所示。

圖中模擬輸入量1至模擬輸入量n是指每一個模數轉換器(ADC)的采樣通道數,模擬量經過低通濾波器預處理后,再進入采樣保持器(S/H),經多路開關(Multi-channelSwitches)分時切換進入模數轉換器,通過DSP(Digital SignalProcessing)芯片的觸發,在CPLD器件的控制下,進入n個通道的一次循環采樣,并將采樣數據依順序打入FIFO器件,DSP在每個采樣結束后直接從FIFO芯片中讀出數據即可。該多通道高速A/D數據采集系統的設計核心就是在DSP芯片的每一個定時中斷時,從FIFO芯片中讀入采樣數據后,復位FIFO器件,觸發CPLD進行硬件時序控制采樣,采樣過程不需要DSP芯片的參與,DSP芯片可以并行處理主程序中的數據。

3 芯片介紹

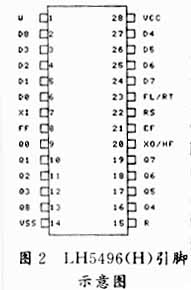

3.1 FIFO存儲器件LH5496(H)簡介

LH5496(H)是SHARP公司采用CMOS工藝制造的512×9位可以實現先進先出(FIFO)算法、可以進行異步讀寫操作的雙端口存儲器。它提供“全空”(/EF)、“全滿”(/FF)、“半滿”(/HF)狀態標志,用以防止數據溢出或不足。擴展邏輯電路允許多片FIFO進行級聯,在字寬和容量深度兩方面進行擴展,而且不會增加額外的延時時間〔3〕。LH5496(H)功能引腳如圖2所示。

讀寫操作會自動訪問存儲器中的連續存儲單元,從FIFO中讀出的數據順序與寫入的順序相同,地址的順序在內部已經預先定義好,對芯片的操作不需要額外的地址信息。芯片提供對讀/寫指針的復位功能(/RS),使內部讀/寫指針同時設置到初始位置。另外,它還對讀指針提供單獨的復位功能(/RT),僅把讀指針設置到初始位置,實現對已讀出數據的重新讀取。該器件采用9位數據寬度,第9位用作控制位或奇偶校驗位,在需要對傳輸進行奇偶校驗的通訊系統中,該位可以被用到。IDT公司的LH5496(H)的存取時間可以有15μs、20μs、25μs、35μs、50μs、65μs、80μs幾種選擇。

需要注意的是,這是一個單向的FIFO雙端口存儲器,即,只能由D0~D8輸入數據,由Q0~Q8輸出數據,所以,讀、寫控制線只有一套。也就是說不能作為

雙向的數據傳送。另外,因為這是一個FIFO(先入先出)存儲器,所以沒有絕對地址的概念,只有讀指針和寫指針的相對位置。當相對位置為0時,表明存儲器空;為所用的存儲器的容量時,表明存儲器己滿。具體包括:

(1)寫操作:只要/FF標志不為0,就可以進行寫操作,且可以與讀操作同時進行。每寫一次數據,寫指針自動加一,當寫指針與讀指針的相對位置為存儲器的容量時,標志/FF清零。當/FF標志為0時,所進行的任何寫操作都不會改變存儲器中的數據,也不會改變寫指針的值。此時的寫禁止由內部控制。

(2)讀操作:只要/EF標志不為0,就可以進行讀操作,且可以與寫操作同時進行。每讀一次數據,讀指針自動加一,當讀指針與寫指針的相對位置為0時,標志/EF清零。當/EF標志為0時,所進行的任何讀操作都不會改變讀指針,且讀出的數據都為0FFH,即數據總線呈現高阻。

3.2 X95108芯片簡介

X95108芯片是XILINX公司生產的CPLD芯片,它是X9500系列芯片,是一種ISP(在系統可編程)芯片〔4〕(http://www.XILINX.com,1998),它的主要特點有:7.5ns的pin-to-pin邏輯時延,工作時鐘125MHz,具有108個宏單元和2400個邏輯門,每個宏單元可工作在省電模式,最多108個用戶I/O引腳,采用ISP在系統可編程技術,可編程10000次以上,支持擴展IEEE1149.1邊界掃描協議(JTAG),輸入輸出緩沖器可兼容5V TTL電平,5V CMOS電平,3.3V及2.5V CMOS電平,封裝有84腳PLCC,100腳PQFT,100腳TQFP,和160腳PQFP供選擇。

3.3 AD976A簡介

AD976A是ANALOGDEVICE公司生產的一種高速16位模數轉換器,其采樣速率為200ksps,能夠在單電源5V供電情況下工作,具有極低功耗的特點(http://www.ANALOG.com,1998)。它的輸入信號范圍為-10V~+10V,內含時鐘、2.5V參考電源和誤差校準電路,使用時,用戶可選擇外部參考電源亦可選擇內部參考電源。芯片采用低功耗設計,最大功率消耗為100mW。AD976A在漂移、增益、線性度和SNR(信噪比)上作了嚴格的修正。有28引腳DIP、SSOP和SOIC封裝可供選擇。

4 系統設計原理及工作原理

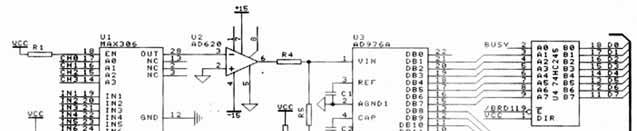

4.1 A/D轉換部分的工作原理

多通道高速A/D數據采集系統的采樣部分的原理框圖如圖3所示。它由一片多路模擬開關MAX306,一片儀器放大器AD620,一片AD976A,兩片數據緩沖接口器件74HC245構成了一個數據轉換單元。MAX306是一個16路的多路模擬開關,本設計中輸入了10路模擬量,其中,前9路接入采樣的模擬信號。為了減小采樣誤差,在信號進入MAX306之前增加了采樣保持LF398進行采樣保持,第10路用于電源電壓的監視。AD620是一個高精度的儀器放大器,本系統將其接成放大倍數為1的工作方式,AD976采用內部2.5V電壓基準源,74HC245作為數據緩沖接口,輸入接到AD976A的數據線上,輸出接到連接FIFO的輸入數據總線上,可以將多個這樣的數據轉換單元并接到總線上,通過每個單元的74HC245的使能腳選通。由于設計上是可以擴展的,即,將多個數據轉換單元數據輸出總線并聯接到FIFO的輸入總線上,所以,采用將AD976A的/BUSY位作為數據位最低位讀入。由于是多通道多A/D轉換器的工作模式,在設計時已經考慮到采樣保持及轉換時間的要求,并給出了一定的裕度,定時采樣時不必判斷A/D轉換是否完成,而直接讀取總線上的數據。在數據處理時,判

斷最低位是否為0來確定本次采樣數據是否有效,如果有效,則右移一位得到有效數據,當然,這樣會降低采樣精度,但對一般的數據處理系統,15位也已經足夠了。如果無效,則舍棄本次采樣數據,并累加無效次數,計數超過設定的次數,則應發出告警,提示AD976A采樣異常。

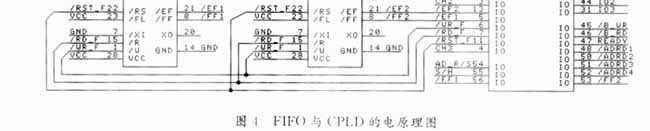

4.2 CPLD實現全自動硬件采樣的原理

FIFO與CPLD及與DSP(TMS320F206)、74HC245輸出總線及外圍器件的連接如圖4所示。圖中,X95108芯片的引腳只畫出了與采樣有關的一部分,另外與DSP接口及存儲器等的片選信號沒有畫出。

FIFO的D0~D15連接到A/D轉換單元的74HC245的輸出數據線上,BD0~BD15則連接到DSP芯片的數據總線上。/WR? F是由CPLD發出的將AD976A轉換完成后的數據打入FIFO的寫信號,/RD? F是DSP采樣數據從FIFO芯片中讀出的讀信號。/RST? F復位FIFO芯片的信號,S/H是啟動采樣保持器工作在采樣還是保持狀態的控制信號,CH0~CH3是每一片A/D芯片的輸入通道選擇。由于每次采樣前會復位FIFO器件,所以,每次采樣開始時的讀指針和寫指針均指向第一個物理存儲地址,只要采樣的數據不超過256個字,/EF和/FF標志可以不讀入判斷,實際上,/EF和/FF標志引腳雖然連接到了X95108,但沒有處理。X95108實現時序的控制,包括:啟動采樣,鎖存數據,啟動A/D轉換,將數據打入FIFO存儲器,通道號遞增重復下一通道采樣。

硬件控制采樣邏輯實際上就是CPLD與采樣保持器、A/D轉換器、FIFO的時序配合,時序由CPLD在DSP觸發采樣后自動完成。

DSP芯片上電初始化時就給FIFO器件發一個復位信號,使FIFO器件的讀指針和寫指針復位,指向第一個物理單元,同時,去觸發CPLD進入第一通道的采樣邏輯,CPLD硬件邏輯如圖5所示。

由于FIFO器件的讀和寫是完全獨立的,所以,DSP芯片在每一個定時中斷中,直接一次性地將所有采樣數據從FIFO中讀取數據,放入DSP的內存區域供處理,讀完數據后,復位FIFO器件并重新觸發CPLD執行下一點的采樣,退出定時中斷程序處理數據。

多個AD976A的轉換是同時進行的,順序進行的僅僅是從AD976A將采樣數據打入FIFO存儲器和從FIFO讀出采樣數據,所以,數據最高采樣速率取決于以下幾個部件的速率,即,采樣保持器的采樣時間,A/D轉換時間,A/D中數據打入FIFO的時間,以及從FIFO中讀出數據的時間。通過選用高速的采樣保持器件和高速的A/D轉換器件,可以提高采樣的速率。

CPLD程序用VHDL語言設計,設計的關鍵是分析各個器件的工作時序和采樣保持時間,A/D轉換時間,打入數據等。VHDL設計的時序處理的進程中,要根據CPLD工作的頻率計算各個等待周期,等器件準備好以后才能進行下一個處理。如圖5所示,DSP觸發復位FIFO信號和采樣邏輯,CPLD先復位FIFO,然后啟動采樣保持器進行采樣,插入等待周期,等采樣完成以后,再發出命令使采樣保持器保持數據,然后啟動A/D轉換器轉換,插入等待周期,即理論上的轉換完成時間加上一定的時間裕度,等待A/D轉換結束,然后將數據打入FIFO,遞增模擬通道號,進行下一通道的采樣。

5 結束語

?? 本文提出了一種易與各種單片機系統接口的由純硬件電路控制的多通道高速數據采集系統。由于本采樣電路是多通道高速采樣,所以要合理地設計直流電源,在設計PCB板時,要注意合理布局和設置良好的靜電屏蔽,還要考慮電磁干擾問題。如果是擴展多個A/D轉換器,A/D選擇的讀入信號為X95108上的/BRD1~/BRD4,在X95108上還可以擴展讀入信號,以增加A/D轉換器,這時更應該注意總線的布局。它的自動采樣硬件電路主要采用CPLD和FIFO技術設計而成。該裝置可以實現多路模擬量的高速采集。在實際應用工頻電流電壓采樣中,可以采集36路模擬量,每個周波(20ms)采樣32點,工作非常穩定可靠,值得推廣。

2 李維波,毛承雄,李啟炎,等.陡脈沖大電流的Rogowski測 量線圈仿真研究.高電壓技術,2002,28(8):11~133 竇振中編著.單片機外圍器件使用手冊——存儲器分冊.北京:北京航空航天大學出版社,1998

4 朱明程編著.XILINX數字系統現場集成技術.南京:東南大學出版社,2001

5 李剛,林凌,葉文宇編著.TMS320F206DSP結構、原理及應用.北京:北京航空航天大學出版社,2002

電子發燒友App

電子發燒友App

評論