有限且不斷縮小的電路板空間、緊張的設(shè)計周期以及嚴格的電磁干擾(EMI)規(guī)范(例如 CISPR 32 和 CISPR 25)這些限制因素,都導(dǎo)致獲得具有高效率和良好熱性能電源的難度很大。在整個設(shè)計周期中,電源設(shè)計通常基本處于設(shè)計過程的最后階段,設(shè)計人員需要努力將復(fù)雜的電源擠進更緊湊的空間,這使問題變得更加復(fù)雜,非常令人沮喪。為了按時完成設(shè)計,只能在性能方面做些讓步,把問題丟給測試和驗證環(huán)節(jié)去處理。簡單、高性能和解決方案尺寸三個考慮因素通常相互沖突:只能優(yōu)先考慮一兩個,而放棄第三個,尤其當(dāng)設(shè)計期限臨近時。犧牲一些性能變得司空見慣;其實不應(yīng)該是這樣的。

本文首先概述了在復(fù)雜的電子系統(tǒng)中電源帶來的嚴重問題:即 EMI,通常簡稱為噪聲。電源會產(chǎn)生 EMI,必須加以解決,那么問題的根源是什么?通常有何緩解措施?本文介紹減少 EMI 的策略,提出了一種解決方案,能夠減少 EMI、保持效率,并將電源放入有限的解決方案空間中。

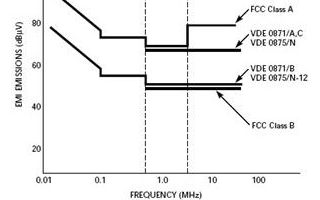

什么是 EMI? 電磁干擾是會干擾系統(tǒng)性能的電磁信號。這種干擾通過電磁感應(yīng)、靜電耦合或傳導(dǎo)來影響電路。它對汽車、醫(yī)療以及測試與測量設(shè)備制造商來說,是一項關(guān)鍵設(shè)計挑戰(zhàn)。上面提到的許多限制和不斷提高的電源性能要求(功率密度增加、開關(guān)頻率更高以及電流更大)只會擴大 EMI 的影響,因此亟需解決方案來減 少 EMI。許多行業(yè)都要求必須滿足 EMI 標準,如果在設(shè)計初期不加以考慮,則會嚴重影響產(chǎn)品的上市時間。

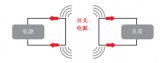

EMI 耦合類型 EMI 是電子系統(tǒng)中的干擾源與接收器(即電子系統(tǒng)中的一些元件)耦合時所產(chǎn)生的問題。EMI 按其耦合介質(zhì)可歸類為:傳導(dǎo)或輻射。

傳導(dǎo) EMI(低頻,450 kHz 至 30 MHz) 傳導(dǎo) EMI 通過寄生阻抗以及電源和接地連接以傳導(dǎo)方式耦合到元件。噪聲通過傳導(dǎo)傳輸?shù)搅硪粋€器件或電路。傳導(dǎo) EMI 可以進一步分為共模噪聲和差模噪聲。

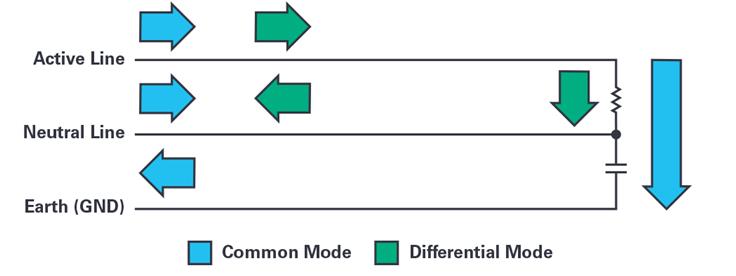

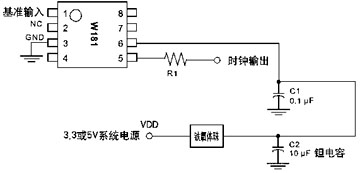

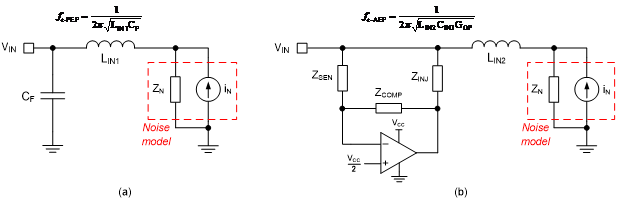

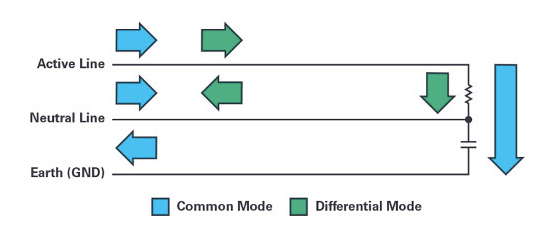

共模噪聲通過寄生電容和高 dV/dt (C × dV/dt)進行傳導(dǎo)。它通過寄生電容沿著任意信號(正或負)到 GND 的路徑傳輸,如圖 1 所示。

差模噪聲通過寄生電感(磁耦合)和高 di/dt (L × di/dt)進行傳導(dǎo)。

圖 1. 差模和共模噪聲。

輻射 EMI(高頻,30 MHz 至 1 GHz) 輻射 EMI 是通過磁場能量以無線方式傳輸?shù)酱郎y器件的噪聲。在開關(guān)電源中,該噪聲是高 di/dt 與寄生電感耦合的結(jié)果。輻射噪聲會影響鄰近的器件。

EMI 控制技術(shù) 解決電源中 EMI 相關(guān)問題的典型方法是什么?首先,確定 EMI 就是一個問題。這看似很顯而易見,但是確定其具體情況可能非常耗時,因為它需要使用 EMI 測試室(并非隨處都有),以便對電源產(chǎn)生的電磁能量進行量化,并確定該電磁能量是否符合系統(tǒng)的 EMI 標準要求。

假設(shè)經(jīng)過測試,電源會帶來 EMI 問題,那么設(shè)計人員將面臨通過多種傳統(tǒng)的校正策略來減少 EMI 的過程,其中包括: 布局優(yōu)化:精心的電源布局與選擇合適的電源組件同樣重要。成功的布局很大程度上取決于電源設(shè)計人員的經(jīng)驗水平。布局優(yōu)化本質(zhì)上是個迭代過程,經(jīng)驗豐富的電源設(shè)計人員有助于最大限度地減少迭代次數(shù),從而避免耽誤時間和產(chǎn)生額外的設(shè)計成本。問題是:內(nèi)部人員往往不具備這些經(jīng)驗。

X 緩沖器:一些設(shè)計人員會提前規(guī)劃并為簡單的緩沖器電路(從開關(guān)節(jié)點到 GND 的簡單 RC 濾波器)提供占位面積。這樣可以抑制開關(guān)節(jié)點的振鈴現(xiàn)象(一項產(chǎn)生 EMI 的因素),但是這種技術(shù)會導(dǎo)致?lián)p耗增加,從而對效率產(chǎn)生負面影響。

X 降低邊沿速率:減少開關(guān)節(jié)點的振鈴也可以通過降低柵極導(dǎo)通的壓擺率來實現(xiàn)。不幸的是,與緩沖器類似,這會對整個系統(tǒng)的效率產(chǎn)生負面影響。

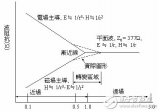

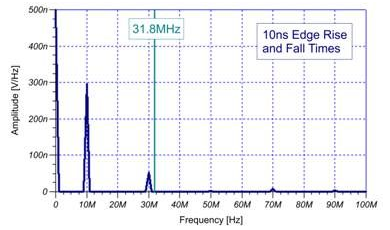

展頻(SSFM):許多 ADI 公司的 Power by linear?開關(guān)穩(wěn)壓器都提供該特性,它有助于產(chǎn)品設(shè)計通過嚴格的 EMI 測試標準。采用 SSFM 技術(shù),在已知范圍內(nèi)(例如,編程頻率 fSW 上下±10%的變化范圍)對驅(qū)動開關(guān)頻率的時鐘進行調(diào)制。這有助于將峰值噪聲能量分配到更寬的頻率范圍內(nèi)。

X 濾波器和屏蔽:濾波器和屏蔽總是會占用大量的成本和空間。它們也使生產(chǎn)復(fù)雜化。

以上所有制約措施都可以減少噪聲,但是它們也都存在缺 陷。最大限度地減少電源設(shè)計中的噪聲通常能夠徹底解決問 題,但卻很難實現(xiàn)。ADI 公司的 Silent Switcher?和 Silent Switcher 2 穩(wěn)壓器在穩(wěn)壓器端實現(xiàn)了低噪聲,從而無需額外的濾波、屏蔽或大量布局迭代。由于不必采用昂貴的反制措施,加快了產(chǎn)品上市時間并節(jié)省大量的成本。

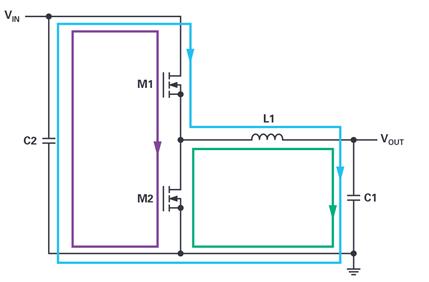

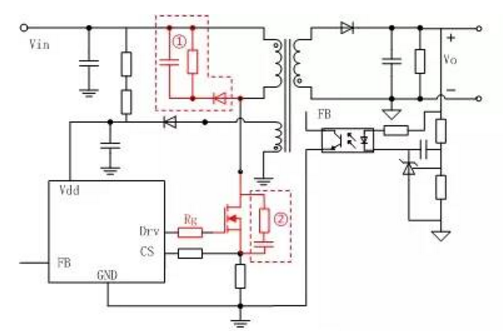

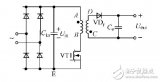

最大限度地減小電流回路 為了減少 EMI,必須確定電源電路中的熱回路(高 di/dt 回路)并減少其影響。熱回路如圖 2 所示。在標準降壓轉(zhuǎn)換器的一個周期內(nèi),當(dāng) M1 關(guān)閉而 M2 打開時,交流電流沿著藍色回路流動。在 M1 打開而 M2 關(guān)閉的關(guān)閉周期中,電流沿著綠色回路流動。產(chǎn)生最高 EMI 的回路并非完全直觀可見,它既不是藍色回路也不是綠 色回路,而是傳導(dǎo)全開關(guān)交流電流(從零切換到 IPEAK ,然后再切換回零)的紫色回路。該回路稱為熱回路,因為它的交流和 EMI 能量最大。

導(dǎo)致電磁噪聲和開關(guān)振鈴的是開關(guān)穩(wěn)壓器熱回路中的高 di/dt 和寄生電感。要減少 EMI 并改進功能,需要盡量減少紫色回路的輻射效應(yīng)。熱回路的電磁輻射騷擾隨其面積的增加而增加,因此,如果可能的話,將熱回路的 PC 面積減小到零,并使用零阻抗理想電容可以解決該問題。

圖 2. 降壓轉(zhuǎn)換器的熱回路

使用 Silent Switcher 穩(wěn)壓器實現(xiàn)低噪聲 磁場抵消 雖然不可能完全消除熱回路區(qū)域,但是我們可以將熱回路分成極性相反的兩個回路。這可以有效地形成局部磁場,這些磁場在距 IC 任意位置都可以有效地相互抵消。這就是 Silent Switcher 穩(wěn)壓器背后的概念。

圖 3. Silent Switcher 穩(wěn)壓器中的磁場抵消。

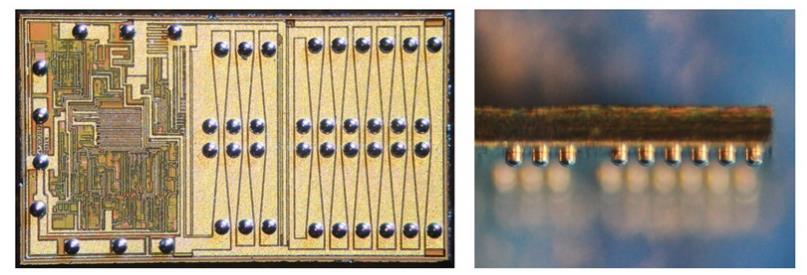

倒裝芯片取代鍵合線 改善 EMI 的另一種方法是縮短熱回路中的導(dǎo)線。這可以通過放棄將芯片連接至封裝引腳的傳統(tǒng)鍵合線方法來實現(xiàn)。在封裝中倒裝硅芯片,并添加銅柱。通過縮短內(nèi)部 FET 到封裝引腳和輸入電容的距離,可以進一步縮小熱回路的范圍。

圖 4. LT8610 鍵合線的拆解示意圖。

圖 5. 帶有銅柱的倒裝芯片。

Silent Switcher 與 Silent Switcher 2

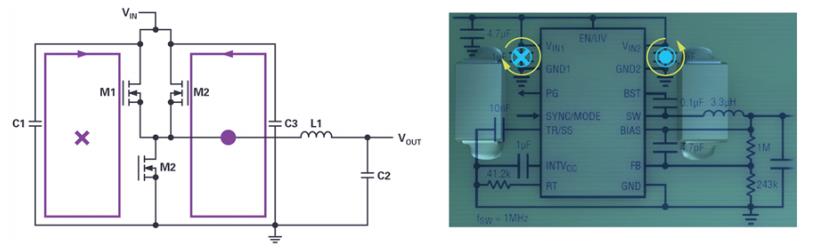

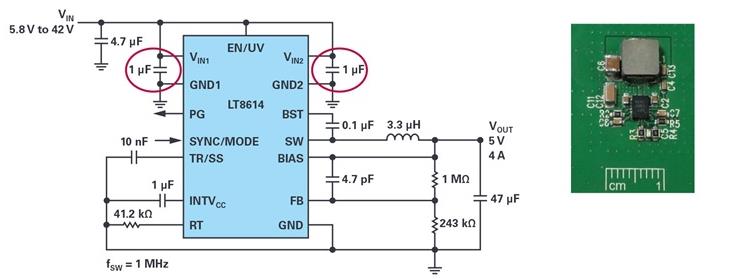

圖 6. 典型的 Silent Switcher 應(yīng)用原理圖及其在 PCB 上的外觀。

圖 6 顯示了使用 Silent Switcher 穩(wěn)壓器的一個典型應(yīng)用,可通過兩個輸入電壓引腳上的對稱輸入電容來識別。布局在該方案中非常重要,因為 Silent Switcher 技術(shù)要求盡可能將這些輸入電容對稱布置,以便發(fā)揮場相互抵消的優(yōu)勢。否則,將喪失 SilentSwitcher 技術(shù)的優(yōu)勢。當(dāng)然,問題是如何確保在設(shè)計及整個生產(chǎn)過程中的正確布局。答案就是 Silent Switcher 2 穩(wěn)壓器。

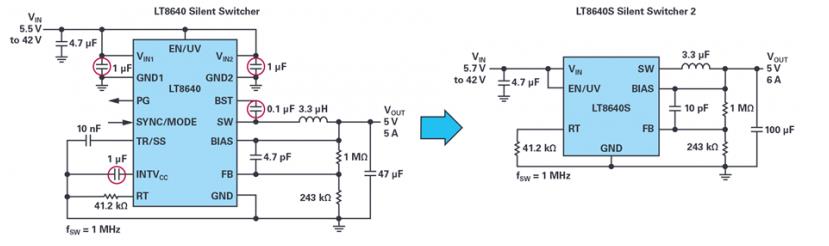

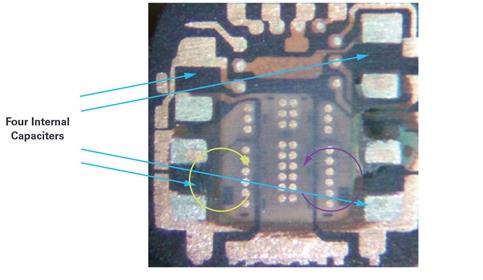

Silent Switcher 2 Silent Switcher 2 穩(wěn)壓器能夠進一步減少 EMI。通過將電容 VIN 電容、 INTVCC 和升壓電容)集成到 LQFN 封裝中,消除了 EMI 性能對 PCB 布局的敏感性,從而可以放置到盡可能靠近引腳的位置。所有熱回路和接地層都在內(nèi)部,從而將 EMI 降至最低,并使解決方案的總占板面積更小。

圖 7. Silent Switcher 應(yīng)用與 Silent Switcher 2 應(yīng)用框圖。

圖 8. 去封的 LT8640S Silent Switcher 2 穩(wěn)壓器。

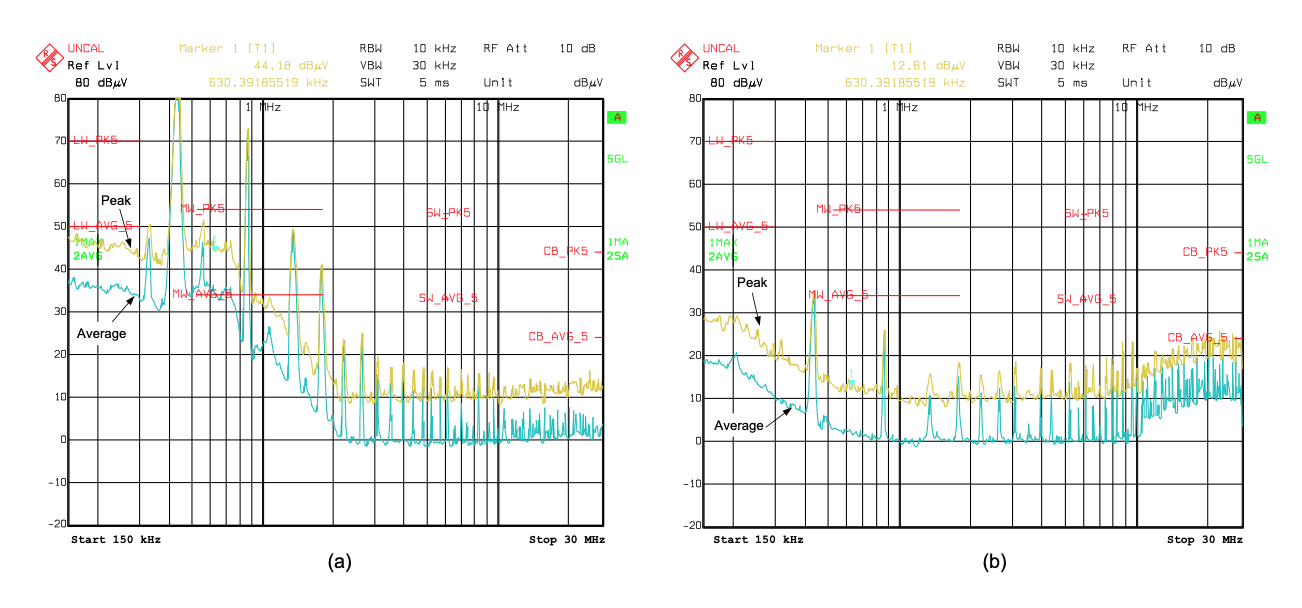

Silent Switcher 2 技術(shù)還可以改善熱性能。LQFN 倒裝芯片封裝上的多個大尺寸接地裸露焊盤有助于封裝通過 PCB 散熱。消除高電阻鍵合線還可以提高轉(zhuǎn)換效率。在進行 EMI 性能測試時, LT8640S 能滿足 CISPR 25 Class 5 峰值限制要求,并且具有較大的裕量。

μModule Silent Switcher 穩(wěn)壓器 借助開發(fā) Silent Switcher 產(chǎn)品組合所獲得的知識和經(jīng)驗,并配合 使用現(xiàn)有的廣泛 μModule?產(chǎn)品組合,使我們提供的電源產(chǎn)品易于設(shè)計,同時滿足電源的某些重要指標要求,包括熱性能、可靠性、精度、效率和良好的 EMI 性能。

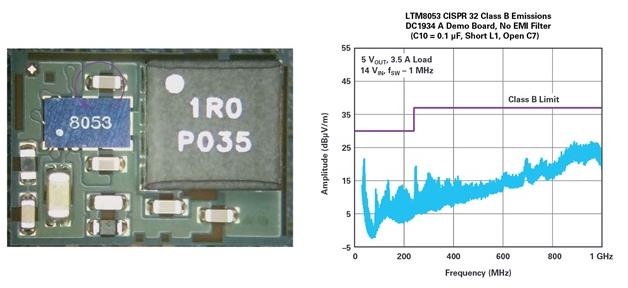

圖 9 所示的 LTM8053 集成了可實現(xiàn)磁場抵消的兩個輸入電容以及 電源所需的其他一些無源組件。所有這些都通過一個 6.25 mm ×9 mm × 3.32 mm BGA 封裝實現(xiàn),讓客戶可以專心完成電路板的其他部分設(shè)計。

圖 9. LTM8053 Silent Switcher 裸露芯片及 EMI 結(jié)果。

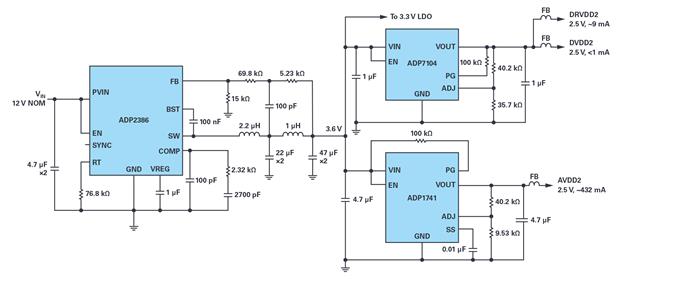

無需 LDO 穩(wěn)壓器——電源案例研究 典型的高速 ADC 需要許多電壓軌,其中一些電壓軌噪聲必須非常低才能實現(xiàn) ADC 數(shù)據(jù)表中的最高性能。為了在高效率、小尺寸板空間和低噪聲之間達成平衡,普遍接受的解決方案是將開關(guān)電源與 LDO 后置穩(wěn)壓器結(jié)合使用,如圖 10 所示。開關(guān)穩(wěn)壓器能夠以更高效率實現(xiàn)更高的降壓比,但噪聲相對也較大。低噪聲 LDO 后置穩(wěn)壓器效率相對較低,但它可以抑制開關(guān)穩(wěn)壓器產(chǎn)生的大部分傳導(dǎo)噪聲。盡可能減小 LDO 后置穩(wěn)壓器的降壓比有助于提高效率。這種組合能產(chǎn)生干凈的電源,從而使 ADC 以最高性能運行。但問題在于多個穩(wěn)壓器會使布局更復(fù)雜,并且 LDO 后置穩(wěn)壓器在較高負載下可能會產(chǎn)生散熱問題。

圖 10. 為 AD9625 ADC 供電的典型電源設(shè)計。

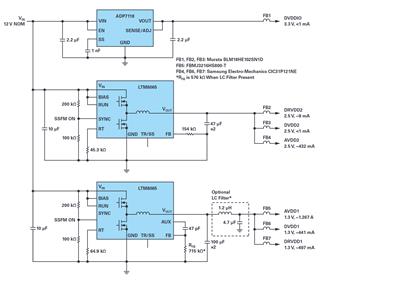

圖 10 所示的設(shè)計顯然需要進行一些權(quán)衡取舍。在這種情況下,低噪聲是優(yōu)先考慮事項,因此效率和電路板空間必須做些讓步。但也許不必如此。最新一代的 Silent Switcher μModule 器件將低噪聲開關(guān)穩(wěn)壓器設(shè)計與μModule 封裝相結(jié)合,能夠同時實現(xiàn)易設(shè)計、高效率、小尺寸和低噪聲的目標。這些穩(wěn)壓器不僅盡可 能減少了電路板占用空間,而且實現(xiàn)了可擴展性,可使用一個μModule 穩(wěn)壓器為多個電壓軌供電,進一步節(jié)省了空間和時間。圖 11 顯示了使用 LTM8065 Silent Switcher μModule 穩(wěn)壓器為 ADC 供電的電源樹替代方案。

圖 11. 使用 Silent Switcher μModule 穩(wěn)壓器為 AD9625 供電,可節(jié)省空間的解決方案。

這些設(shè)計都已經(jīng)過相互測試比較。ADI 公司最近發(fā)表的一篇文章對使用圖 10 和圖 11 所示電源設(shè)計的 ADC 性能進行了測試和比較。測試包括以下三種配置: 使用開關(guān)穩(wěn)壓器和 LDO 穩(wěn)壓器為 ADC 供電的標準配置。 使用 LTM8065 直接為 ADC 供電,不進行進一步的濾波。 使用 LTM8065 和額外的輸出 LC 濾波器,進一步凈化輸出。

測得的 SFDR 和 SNRFS 結(jié)果表明,LTM8065 可用于直接為 ADC 供電,并不會影響 ADC 的性能。

這個實施方案的核心優(yōu)勢是大大減少了元件數(shù)量,從而提高了效率,簡化了生產(chǎn)并減少了電路板占位空間。

小結(jié) 總之,隨著更多系統(tǒng)級設(shè)計需要滿足更加嚴格的規(guī)范,盡可能充分利用模塊化電源設(shè)計變得至關(guān)重要,尤其在電源設(shè)計專業(yè)經(jīng)驗有限的情況下。由于許多細分市場要求系統(tǒng)設(shè)計必須符合最新的 EMI 規(guī)范要求,因此將 Silent Switcher 技術(shù)運用于小尺寸設(shè)計,同時借助μModule 穩(wěn)壓器簡單易用的特性,可以大大縮短產(chǎn)品上市時間,同時還可以節(jié)省電路板空間。

電子發(fā)燒友App

電子發(fā)燒友App

評論