介紹

LWIP(Lightweight IP)是一個輕量級的開源TCP/IP協(xié)議棧,它專為嵌入式系統(tǒng)和小型設(shè)備而設(shè)計。LWIP旨在提供TCP/IP網(wǎng)絡(luò)協(xié)議支持,使嵌入式系統(tǒng)能夠與其他設(shè)備通過網(wǎng)絡(luò)進(jìn)行通信

LWIP特點(diǎn):

- 輕量級:LWIP被設(shè)計為占用較少的內(nèi)存和處理器資源,使其能夠在嵌入式系統(tǒng)中高效運(yùn)行。

- 可裁剪性:LWIP允許根據(jù)具體需求進(jìn)行裁剪,只包含必要的協(xié)議和功能,以減小存儲空間和處理器開銷。

- 高性能:LWIP使用了一些性能優(yōu)化技術(shù),如零拷貝和事件驅(qū)動機(jī)制,以提高網(wǎng)絡(luò)通信的效率和吞吐量。

- 可移植性:LWIP具有良好的可移植性,可以在多種操作系統(tǒng)和硬件平臺上運(yùn)行。 支持多種應(yīng)用層協(xié)議:除了TCP/IP協(xié)議棧,LWIP還提供了一些常用的應(yīng)用層協(xié)議實(shí)現(xiàn),如HTTP、SNMP和MQTT。

以太網(wǎng)簡介

STM32中可以通過以太網(wǎng)按照 IEEE 802.3-2002 標(biāo)準(zhǔn)發(fā)送和接收數(shù)據(jù)。以太網(wǎng)提供了可配置、靈活的外設(shè),用以滿足客戶的各種應(yīng)用需求。它支持與外部物理層(PHY) 相連的兩個工業(yè)標(biāo)準(zhǔn)接口:默認(rèn)情況下使用的介質(zhì)獨(dú)立接口 (MII)(在 IEEE 802.3 規(guī)范中定義)和簡化介質(zhì)獨(dú)立接口 (RMII)。

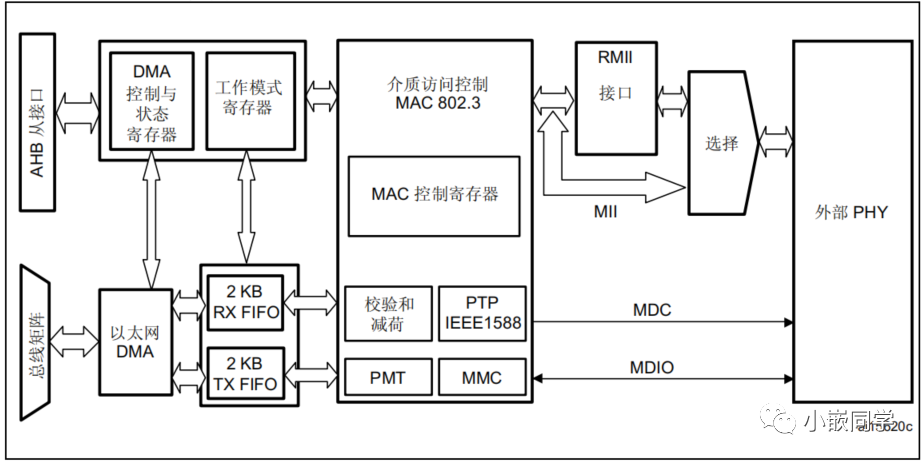

stm32 以太網(wǎng)框圖

當(dāng)進(jìn)行發(fā)送數(shù)據(jù)的時候,首先系統(tǒng)存儲器以DMA的方式發(fā)送至發(fā)送FIFO(Tx FIFO)進(jìn)行緩沖,再通過MAC內(nèi)核進(jìn)行發(fā)送。同樣,接收 FIFO (Rx FIFO) 則存儲通過線路接收的以太網(wǎng)幀,直到這些幀通過 DMA 傳送到系統(tǒng)存儲器。

以太網(wǎng)外設(shè)還包括用于與外部 PHY 通信的 SMI。通過一組配置寄存器,用戶可以為 MAC 控 制器和 DMA 控制器選擇所需模式和功能。

上面的主要需要分析的模式是:MAC內(nèi)核、RMII/MII介質(zhì)接口、外部的PHY.

MAC內(nèi)核

MAC內(nèi)核是以太網(wǎng)控制器的關(guān)鍵組件,負(fù)責(zé)處理以太網(wǎng)幀的發(fā)送、接收、解析、封裝、錯誤檢測和流控制等功能。它與PHY層緊密協(xié)作,實(shí)現(xiàn)了STM32F4微控制器與以太網(wǎng)之間的可靠數(shù)據(jù)通信。

- 幀處理:MAC內(nèi)核負(fù)責(zé)處理以太網(wǎng)數(shù)據(jù)幀的發(fā)送和接收。它與PHY層進(jìn)行接口連接,將主機(jī)發(fā)送的數(shù)據(jù)封裝為以太網(wǎng)幀并發(fā)送到網(wǎng)絡(luò)上,同時從網(wǎng)絡(luò)接收數(shù)據(jù)幀并傳遞給主機(jī)進(jìn)行處理。

- 幀解析和封裝:MAC內(nèi)核負(fù)責(zé)解析接收到的以太網(wǎng)幀,提取其中的目標(biāo)MAC地址、源MAC地址、幀類型和數(shù)據(jù)等信息。同時,它也負(fù)責(zé)封裝主機(jī)發(fā)送的數(shù)據(jù)為以太網(wǎng)幀,添加必要的控制信息。

- 錯誤檢測和處理:MAC內(nèi)核執(zhí)行幀的校驗和錯誤檢測。它會驗證接收到的幀的完整性和正確性,通過校驗和字段檢查是否存在錯誤。如果幀出現(xiàn)錯誤或校驗失敗,MAC內(nèi)核會丟棄或丟棄該幀,并通知主機(jī)。

- 幀的重傳和丟棄:MAC內(nèi)核負(fù)責(zé)處理發(fā)送失敗或接收錯誤的情況。在發(fā)送時,如果未收到幀的確認(rèn)響應(yīng)或檢測到?jīng)_突,MAC內(nèi)核會觸發(fā)重傳機(jī)制。在接收時,如果幀出現(xiàn)錯誤或無效,MAC內(nèi)核會丟棄該幀并通知主機(jī)。

- 幀流控制:MAC內(nèi)核支持流控制機(jī)制,用于控制數(shù)據(jù)幀的發(fā)送速率。它可以根據(jù)接收端的緩沖區(qū)狀態(tài)和網(wǎng)絡(luò)流量情況,自動調(diào)整發(fā)送速率,以避免數(shù)據(jù)丟失或網(wǎng)絡(luò)擁塞。

上面是MAC內(nèi)核功能的描述,了解一下即可。我們主要是要關(guān)注Mac內(nèi)核與PHY的物理接口看MAC是如何管理PHY.

站管理接口:SMI

描述

站管理接口(Station Management Interface,SMI)是用于與物理層(PHY)設(shè)備進(jìn)行通信和配置的接口。SMI接口提供了主機(jī)(STM32)與PHY設(shè)備之間的通信通道,使得主機(jī)能夠控制和監(jiān)控PHY設(shè)備的操作。主要功能如下:

- 寄存器訪問:通過SMI接口,主機(jī)可以讀取和寫入PHY設(shè)備的寄存器。這些寄存器包含了控制PHY設(shè)備功能和配置參數(shù)的信息。主機(jī)可以通過讀取和寫入寄存器的值來配置PHY設(shè)備的工作模式、速度、雙工模式等。

- PHY設(shè)備配置:主機(jī)可以使用SMI接口來配置PHY設(shè)備的各種參數(shù)。通過讀取和寫入寄存器的值,主機(jī)可以設(shè)置PHY設(shè)備的工作模式、速度、自動協(xié)商等。這樣可以適應(yīng)不同的網(wǎng)絡(luò)環(huán)境和需求。

- 狀態(tài)查詢:通過SMI接口,主機(jī)可以查詢PHY設(shè)備的狀態(tài)信息。主機(jī)可以讀取PHY設(shè)備的狀態(tài)寄存器,以獲取連接狀態(tài)、速度狀態(tài)、工作模式等信息。這些狀態(tài)信息可以幫助主機(jī)監(jiān)測網(wǎng)絡(luò)連接和PHY設(shè)備的工作狀態(tài)。

- 錯誤處理:SMI接口還提供了錯誤處理的能力。主機(jī)可以讀取PHY設(shè)備的狀態(tài)寄存器以檢測錯誤標(biāo)志,并根據(jù)錯誤類型采取適當(dāng)?shù)拇胧@纾匦屡渲肞HY設(shè)備、進(jìn)行錯誤恢復(fù)等,以確保網(wǎng)絡(luò)通信的可靠性。

主要是關(guān)注SMI對PHY設(shè)置:如工作模式、速度、雙工模式、自動協(xié)商設(shè)置。

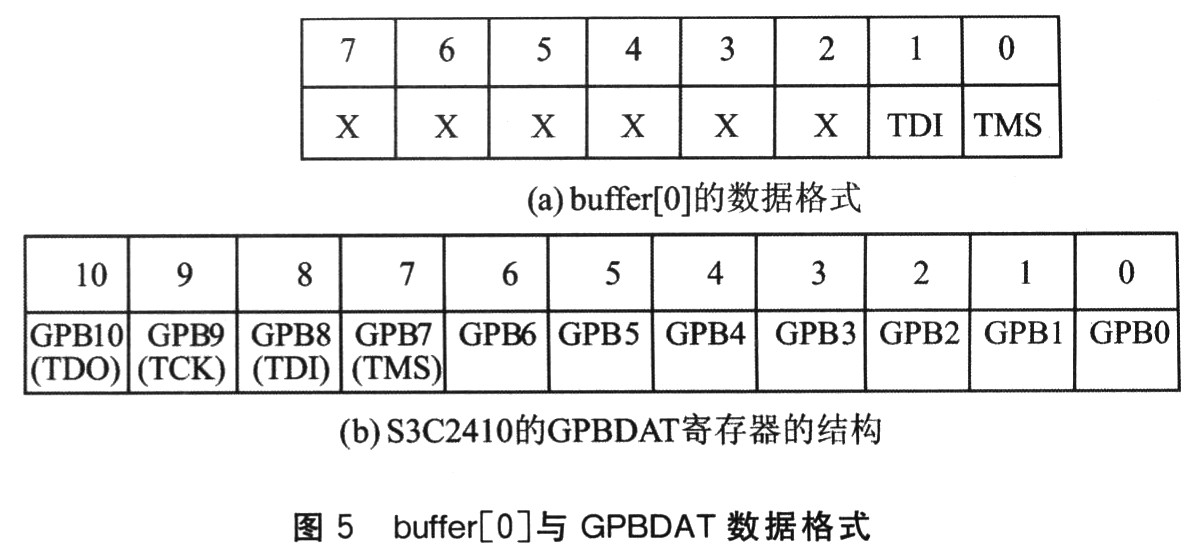

SMI 站管理接口

如上圖,SMI與PHY硬件接口由兩根組成:MDC[時鐘線]、MDIO[數(shù)據(jù)線]。通過這兩根線可以訪問多達(dá)32個PHY。SMI可以從 32 個 PHY 中選擇一個 PHY 。PHY里面包含了一個 32 個寄存器。這個寄存器中主要是對發(fā)送數(shù)據(jù)進(jìn)行控制\\接收狀態(tài)信息。任意時間只能訪問一個PHY。它的幀結(jié)構(gòu)如下。

幀格式

- 報頭:SMI幀以4個報頭字節(jié)(0xFFFFFFFF)開始,在發(fā)送\\寫入操作時,用于主機(jī)與PHY設(shè)備的之間建立同步通信。

- 起始:幀起始由 [01] 模式定義,用于驗證線路從默認(rèn)邏輯“1”狀態(tài)變?yōu)檫壿嫛?”狀 態(tài),然后再從邏輯“0”狀態(tài)變?yōu)檫壿嫛?”狀態(tài)。

- 操作:定義正在發(fā)生的事務(wù)(讀取[10]或?qū)懭隱01])的類型。

- PHY地址:PHY 地址有 5 位,可構(gòu)成 32 個唯一 PHY 地址。最先發(fā)送和接收地址的 MSB 位。

- 寄存器地址:寄存器地址有 5 位,從而可在所選 PHY 設(shè)備中對 32 個不同的寄存器進(jìn)行尋 址。最先發(fā)送和接收地址的 MSB 位。

- TA:周轉(zhuǎn)字段在 RADDR 和 DATA 字段間定義了一個 2 位模式,以避免在讀取事務(wù)期間 出現(xiàn)競爭現(xiàn)象。讀取事務(wù)時,MAC 控制器將 TA 的 2 個位驅(qū)動為 MDIO 線上的高阻態(tài)。 PHY 設(shè)備必須將 TA 的第一位驅(qū)動為高阻態(tài),將 TA 的第二位驅(qū)動為“0”。 寫入事務(wù)時,MAC 控制器針對 TA 字段驅(qū)動 [10] 模式。PHY 設(shè)備必須將 TA 的 2 個位 驅(qū)動為高阻態(tài)。

- 數(shù)據(jù):數(shù)據(jù)字段為 16 位。最先發(fā)送和接收的位必須為 ETH_MIID 寄存器的位 15。

- 空閑:MDIO 線驅(qū)動為高阻態(tài)。三態(tài)驅(qū)動器必須禁止,PHY 的上拉電阻使線路保持邏輯 “1”狀態(tài)。

寫操作

當(dāng)應(yīng)用程序?qū)?MII 寫入位和繁忙位置 1 時,SMI 將通過傳輸 PHY 地址、PHY 中的寄存器地址以及寫入數(shù)據(jù)。來觸發(fā)對 PHY 寄存器進(jìn)行寫操作。事務(wù)進(jìn)行期間, 應(yīng)用程序不能更改 MII 地址寄存器的內(nèi)容或 MII 數(shù)據(jù)寄存器。在此期間對 MII 地址寄存器或 MII 數(shù)據(jù)寄存器執(zhí)行的寫操作將會忽略(繁忙位處于高電平狀態(tài)),事務(wù)將無錯完成。寫操 作完成后,SMI 將通過復(fù)位繁忙位進(jìn)行指示。

寫操作

讀操作

當(dāng)用戶將以太網(wǎng) MAC MII 地址寄存器 (ETH_MACMIIAR) 中的 MII 繁忙位置 1、MII 寫入位清 零時,SMI 將通過傳輸 PHY 地址和 PHY 中的寄存器地址在 PHY 寄存器中觸發(fā)讀操作。事 務(wù)進(jìn)行期間,應(yīng)用程序不應(yīng)更改 MII 地址寄存器的內(nèi)容或 MII 數(shù)據(jù)寄存器。在此期間對 MII 地址寄存器或 MII 數(shù)據(jù)寄存器執(zhí)行的寫操作將會忽略(繁忙位處于高電平狀態(tài)),事務(wù)將無 錯完成。讀操作完成后,SMI 將復(fù)位繁忙位,然后用從 PHY 中讀取的數(shù)據(jù)更新 MII 數(shù)據(jù)寄存器。

讀操作

時鐘選擇

MAC 啟動管理寫/讀操作。SMI 時鐘是一個分頻時鐘,其時鐘源為應(yīng)用時鐘(AHB 時鐘)。 分頻系數(shù)取決于 MII 地址寄存器中設(shè)置的時鐘范圍。

時鐘選擇

介質(zhì)接口

上面我們提到過一個MII的概念。MII其實(shí)就是一種介質(zhì)接口。STM32除了MII介質(zhì)接口外還有RMII介質(zhì)接口。介質(zhì)接口是配合SMI對PHY進(jìn)行控制的。比如:SMI什么時候發(fā)數(shù)據(jù)、什么時候收數(shù)據(jù)、發(fā)寫操作幀還是發(fā)讀操作幀都是需要介質(zhì)接口上的寄存器的值進(jìn)行控制的。為此,MAC內(nèi)核與PHY的物理接口其實(shí)就是SMI+RMII/MII 組成,后面分析都是基于這兩者結(jié)合體。

介質(zhì)獨(dú)立接口:MII

介質(zhì)獨(dú)立接口 (MII) 定義了 10 Mbit/s 和 100 Mbit/s 的數(shù)據(jù)傳輸速率下 MAC 子層與 PHY 之間的互連。

介質(zhì)獨(dú)立接口信號

- TX_CLK:連續(xù)時鐘信號。該信號提供進(jìn)行 TX 數(shù)據(jù)傳輸時的參考時序。標(biāo)稱頻率為: 速率為 10 Mbit/s 時為 2.5 MHz;速率為 100 Mbit/s 時為 25 MHz。

- TXD(Transmit Data):TXD信號是主機(jī)向PHY設(shè)備發(fā)送數(shù)據(jù)的并行輸出信號。主機(jī)通過TXD線將以太網(wǎng)幀的數(shù)據(jù)發(fā)送給PHY設(shè)備。

- TX_EN:發(fā)送使能信號。該信號必 須與報頭的前半字節(jié)進(jìn)行同步 (MII_TX_CLK)

- RX_CLK:連續(xù)時鐘信號。該信號提供進(jìn)行 RX 數(shù)據(jù)傳輸時的參考時序。標(biāo)稱頻率 為:速率為 10 Mbit/s 時為 2.5 MHz;速率為 100 Mbit/s 時為 25 MHz。

- RXD[3:0]:數(shù)據(jù)接收信號。該信號是 4 個一組的數(shù)據(jù)信號。

- RX_ER:接收錯誤信號。該信號必須保持一個或多個周期 (MII_RX_CLK),從而向 MAC 子層指示在幀的某處檢測到錯誤。

- RX_DV:接收數(shù)據(jù)有效信號。該信號表示 PHY 當(dāng)前正針對 MII 接收已恢復(fù)并解碼的半字節(jié)。

- CRS:載波偵聽信號。當(dāng)發(fā)送或接收介質(zhì)處于非空閑狀態(tài)時,由 PHY 使能該信號。

- COL:沖突檢測信號。檢測到介質(zhì)上存在沖突后,PHY 必須立即使能沖突檢測信號, 并且只要存在沖突條件,沖突檢測信號必須保持有效狀態(tài)。該信號無需與 TX 和 RX 時 鐘保持同步。在全雙工模式下,該信號沒意義。

- MDIO(Management Data Input/Output):MDIO信號用于主機(jī)與PHY設(shè)備之間的管理數(shù)據(jù)的雙向傳輸。主機(jī)通過MDIO信號線向PHY設(shè)備發(fā)送配置和控制命令,并從PHY設(shè)備讀取狀態(tài)和配置信息。

- MDC(Management Data Clock):MDC信號是MDIO信號的時鐘信號,用于同步MDIO數(shù)據(jù)的傳輸。MDC信號的頻率由主機(jī)控制,用于提供時序同步。

TX 接口信號編碼

RX 接口信號編碼

MII時鐘源

要生成 TX_CLK 和 RX_CLK 時鐘信號,必須向外部 PHY 提供 25MHz 時鐘,如下圖示。除了使用外部 25 MHz 石英晶體提供該時鐘,還可以通過 STM32F4xx 微控制器的 MCO 引腳輸出該信號。這種情況下,必須對 PLL 倍頻進(jìn)行配置,以通過 25 MHz 外部石英晶體在 MCO 引腳上獲得所需頻率。

精簡介質(zhì)獨(dú)立接口:RMII

精簡介質(zhì)獨(dú)立接口 (RMII) 規(guī)范降低了 10/100 Mbit/s 下微控制器以太網(wǎng)外設(shè)與外部 PHY 間的 引腳數(shù)。根據(jù) IEEE 802.3u 標(biāo)準(zhǔn),MII 包括 16 個數(shù)據(jù)和控制信號的引腳。RMII 規(guī)范將引腳 數(shù)減少為 7 個(引腳數(shù)減少 62.5%)。

RMII 接口是 MAC 和 PHY 之間的實(shí)例化對象。這有助于將 MAC 的 MII 轉(zhuǎn)換為 RMII。RMII 具有以下特性:

- 支持 10-Mbit/s 和 100-Mbit/s 的運(yùn)行速率

- 參考時鐘必須是 50 MHz

- 相同的參考時鐘必須從外部提供給 MAC 和外部以太網(wǎng) PHY

- 它提供了獨(dú)立的 2 位寬(雙位)的發(fā)送和接收數(shù)據(jù)路徑

RMII時鐘源

時鐘源方案

MII與RMII除了在IO接口不同外,還存在著發(fā)送位寬的不同。介質(zhì)MII接口一個周期發(fā)送位寬位4位,RMII的是2位。但是由于他們發(fā)送周期不同。如果在相同的時間內(nèi),RMII發(fā)送了兩次而MII發(fā)送了一次。所以最終的速率是一樣的。

PHY

描述

上面分析的過程中,我們知道了。Mac內(nèi)核的數(shù)據(jù)最終,是通過PHY發(fā)送出去的。那么PHY是什么?這里主要是對LAN8720A這款PHY進(jìn)行分析。如下圖就是LAN8720A的內(nèi)部框圖

LAN8720A內(nèi)部框圖

PHY在計算機(jī)網(wǎng)絡(luò)中起著關(guān)鍵作用,負(fù)責(zé)將數(shù)字?jǐn)?shù)據(jù)轉(zhuǎn)換為物理信號,并在物理介質(zhì)上進(jìn)行可靠的傳輸。它處理信號的編碼、調(diào)制、傳輸和解調(diào)過程,同時支持時鐘同步、錯誤檢測和糾正,以及自動協(xié)商功能。PHY的正確操作和配置對于實(shí)現(xiàn)高速、可靠的數(shù)據(jù)通信至關(guān)重要。

LAN8720A

PHY內(nèi)部包含了32個寄存器,都是通過MAC的SMI上的MDC與MDIO這兩根線進(jìn)行PHY的寄存器的讀寫。上面我們知道我們主要是通過這兩根線實(shí)現(xiàn)PHY的速度與雙工模式確定。

LAN8720A的32個內(nèi)部寄存器如下

LAN8720A內(nèi)部寄存器

而控制雙工模式以及速度的模式主要存在于第3 1個寄存器也稱為BCR寄存器,其寄存器設(shè)置如下。

雙工與模式設(shè)置寄存器

如下圖是前面提及的MDIO數(shù)據(jù)幀格式

對于2:4字段。最高位為1的時候表示是全雙工、0的時候表示半雙工。第二第三位代表的速度。01 表示10Mbit/s、10表示100Mbit/s如果我想把當(dāng)前的第一個PHY假如為0x00[有多個PHY]設(shè)置為100Mbit/s 與全雙工模式。該如何操作?

首先,確定時PHY的地址。那么PHY的地址就是0x00。接下來就是寄存器的地址,這里的寄存器是最后一個寄存器地址:0x1F.最后是數(shù)據(jù)位:100Mbit/s 全雙工。對應(yīng)上面表的110,所以數(shù)據(jù)位為0000000000011000.

MAC 802.3 幀格式

上面的分析其實(shí)都是在物理層于數(shù)據(jù)鏈路層的內(nèi)容。既然是在物理層那么就應(yīng)該有物理層的數(shù)據(jù)幀結(jié)構(gòu)標(biāo)準(zhǔn)。這個幀標(biāo)準(zhǔn)就是MAC 802.3 幀格式。這個幀結(jié)構(gòu)分為:有標(biāo)記MAC幀格式與無標(biāo)記MAC幀結(jié)構(gòu)

無標(biāo)記MAC幀格式

- 報頭:MAC幀以7個字節(jié)的報頭(10101010...)開始,用于同步接收方的時鐘。

- 幀起始定界符(Start Frame Delimiter,SFD):緊接著前導(dǎo)碼是一個字節(jié)的SFD(10101011),用于標(biāo)識幀的起始。

- 目標(biāo)MAC地址(Destination MAC Address):6個字節(jié),指示數(shù)據(jù)幀的目標(biāo)設(shè)備的MAC地址。該字段唯一標(biāo)識了數(shù)據(jù)幀的接收方。

- 源MAC地址(Source MAC Address):6個字節(jié),指示數(shù)據(jù)幀的發(fā)送設(shè)備的MAC地址。該字段唯一標(biāo)識了數(shù)據(jù)幀的發(fā)送方。

- 長度/類型(Length/Type):2個字節(jié),指示數(shù)據(jù)字段的長度或指示數(shù)據(jù)字段的類型。當(dāng)長度小于等于1500時,它指示了上層協(xié)議類型。

- 數(shù)據(jù)字段(Data):46-1500個字節(jié),包含了上層協(xié)議(如IP或ARP)傳輸?shù)臄?shù)據(jù)。

- 幀校驗序列(Frame Check Sequence,F(xiàn)CS):4個字節(jié),用于檢測數(shù)據(jù)幀在傳輸過程中是否發(fā)生了錯誤。FCS字段使用循環(huán)冗余校驗(CRC)算法計算得出。

帶標(biāo)記的 MAC 幀格式

帶標(biāo)記的MAC幀格式和不帶標(biāo)識符的MAC幀之間的區(qū)別在于是否包含了標(biāo)識符字段。下面是它們的區(qū)別:

- 帶標(biāo)記的MAC幀格式(Tagged MAC Frame):帶標(biāo)記的MAC幀格式是在不同的網(wǎng)絡(luò)技術(shù)中使用的一種擴(kuò)展幀格式。它包含了一個額外的標(biāo)識符字段,用于標(biāo)記幀所屬的虛擬局域網(wǎng)(VLAN)。標(biāo)識符字段是一個特定的VLAN標(biāo)簽,用于將幀與相應(yīng)的VLAN關(guān)聯(lián)起來。帶標(biāo)記的MAC幀格式通常用于實(shí)現(xiàn)虛擬局域網(wǎng)的劃分和管理。

- 不帶標(biāo)識符的MAC幀格式(Untagged MAC Frame):不帶標(biāo)識符的MAC幀格式是最常見的以太網(wǎng)幀格式,也被稱為普通以太網(wǎng)幀格式。它不包含額外的標(biāo)識符字段,只包含了目標(biāo)MAC地址、源MAC地址、長度/類型、數(shù)據(jù)字段和幀校驗序列。不帶標(biāo)識符的MAC幀格式適用于普通的以太網(wǎng)通信,不涉及虛擬局域網(wǎng)的劃分和管理。

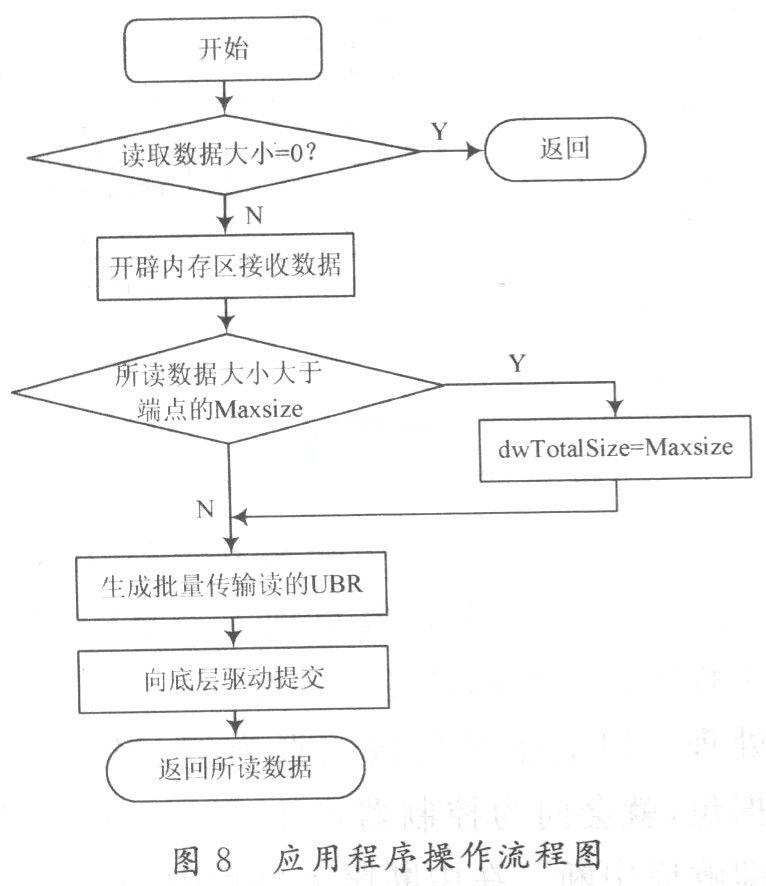

以太網(wǎng)DMA描述符

如下框圖,已經(jīng)分析了MAC內(nèi)核、PHY。而最后我們需要對以外網(wǎng)DMA與TxFiFo、RxFiFo 這部分進(jìn)行分析。

stm32 以太網(wǎng)框圖

以太網(wǎng)DMA控制器操作過程:

DMA 具有獨(dú)立的發(fā)送和接收引擎以及相應(yīng)的 CSR(控制和狀態(tài)寄存器)空間。發(fā)送引擎將 數(shù)據(jù)從系統(tǒng)存儲器傳送到 Tx FIFO,而接收引擎將數(shù)據(jù)從 Rx FIFO 傳送到系統(tǒng)存儲器。DMA 可以在 CPU 完全不干預(yù)的情況下,通過描述符有效地將數(shù)據(jù)從源傳送到目標(biāo)。DMA 專為面 向包的數(shù)據(jù)傳送(如以太網(wǎng)中的幀)而設(shè)計。該控制器經(jīng)過編程后,可在完成幀發(fā)送和接收 傳送操作時以及其它正常/錯誤條件下產(chǎn)生 CPU 中斷。DMA 和 STM32通過以下兩種數(shù) 據(jù)結(jié)構(gòu)進(jìn)行通信:

- 控制和狀態(tài)寄存器 (CSR)

- 描述符列表和數(shù)據(jù)緩沖區(qū)。

什么是以太網(wǎng)DMA描述符

DMA 既可將接收到的數(shù)據(jù)幀傳送到 STM32F4xx 存儲器中的接收緩沖區(qū),也可以傳送 STM32 存儲器的發(fā)送緩沖區(qū)中的數(shù)據(jù)幀。位于 STM32F4xx 存儲器中的描述符用作指向這些緩沖區(qū)的指針。共有兩個描述符列表:一個用于接收,一個用于發(fā)送。兩個列表的基址分別寫入 DMA 寄存器 3 和寄存器 4。最后一個描述符會指回第一個描述符以構(gòu)成環(huán)形結(jié)構(gòu)。可通過配置接收和發(fā)送描述符 (RDES1[14] 和 TDES0[20])中鏈接的第二個地址來完成描述符的顯式鏈接。

簡單來說就是TxFiFo與RxFiFo緩沖區(qū)內(nèi)存的管理是通過鏈表實(shí)現(xiàn)。不然怎么叫FIFO先入先出不就是一個隊列數(shù)據(jù)結(jié)構(gòu)嘛。

DMA 既可將接收到的數(shù)據(jù)幀傳送到 STM32F4xx 存儲器中的接收緩沖區(qū),也可以傳送 STM32 存儲器的發(fā)送緩沖區(qū)中的數(shù)據(jù)幀。位于 STM32F4xx 存儲器中的描述符用作指向這些緩沖區(qū)的指針。

描述符

描述符主要分兩種:常規(guī)描述符、增強(qiáng)描述符

常規(guī)描述符:管理緩沖區(qū)常規(guī)描述符:在常規(guī)描述符基礎(chǔ)上開啟時間戳和 IPv4校驗和減荷這里主要分析常規(guī)的描述符,其結(jié)構(gòu)框圖如下

常規(guī) Tx DMA 描述符

其中需要比較注意的位為

- TDES0[31]置0:CPU可將數(shù)據(jù)拷貝到描述符中,拷貝完成之后把該位置1,告訴DMA可以發(fā)送數(shù)據(jù)

- TDES0[20]置1:描述符中的第二個地址是下一個描述符地址

- TDES1[28:16]:如果TDES0[20] 位置1,則該字段無效

- TDES3[31:0]:取決于TDES0[20]的值,為1,則指向下一個描述符地址

常規(guī) Rx DMA 描述符結(jié)構(gòu)

- RDES0[31]置1:MAC將數(shù)據(jù)從RX FIFO傳輸?shù)絉X描述符中,拷貝完成之后該位置0,告訴CPU可以接收數(shù)據(jù)

- RDES0[14]置1:描述符中的第二個地址是下一個描述符地址

- RDES1[28:16]:如果RDES0[14]位置1,則該字段無效

- RDES3[31:0]:取決于RDES0[14]的值,為1,則指向下一個描述符地址

描述符結(jié)構(gòu)

其中根據(jù)RES3/TDES3字段來判斷是什么結(jié)構(gòu),如果是指向下一個緩沖區(qū)地址那么就是鏈接結(jié)構(gòu),如果是第二個緩沖區(qū)就是1環(huán)形結(jié)構(gòu)。

電子發(fā)燒友App

電子發(fā)燒友App

評論