電子發燒友網核心提示:本文為玩轉賽靈思Zedboard開發板(3):基于Zynq PL的流水燈,內容精彩,敬請對電子發燒友網保持密切關注。基于Zynq PL的流水燈是使用PL做流水燈實驗,目的是為

2012-12-05 14:25:41 12770

12770 本文轉自公眾號歡迎關注 《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下 (qq.com) 一.前言 前面我們了解了板子的原理圖和資源,進行了基本的狀態確認,現在我們

2023-07-19 18:36:28 1353

1353

大家好!我是一名學生,與我的合作伙伴一起在MicroZed板上開展項目。我們正在使用Vivado 2015.4,Xilinix SDK 2015.4和Digilent USB-JTAG編程電纜(我們

2019-10-22 08:47:02

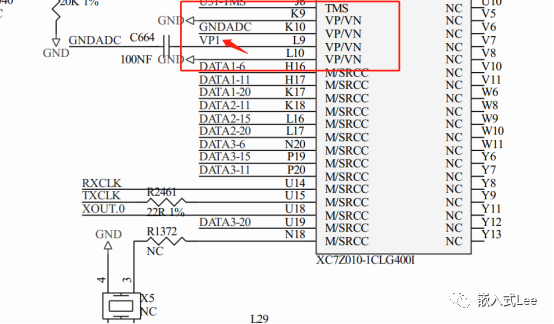

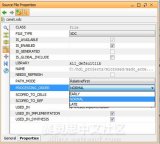

你好,我有一個關于XADC及其AXI4Lite接口輸入的問題。我想在Microzed 7020主板上測試XADC,在通過AXI4Lite接口將Zynq PL連接到XADC向導(參見第一個附件)之后

2018-11-01 16:07:36

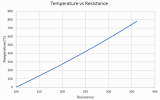

大家好!我們開始在Zynq(XC7Z020)中使用XADC,SW人員想知道溫度報警中斷是否有滯后現象?特別是有兩個位似乎很有用,cource的bit 0(OT)和bit 8(OT Deactive

2020-07-15 08:37:12

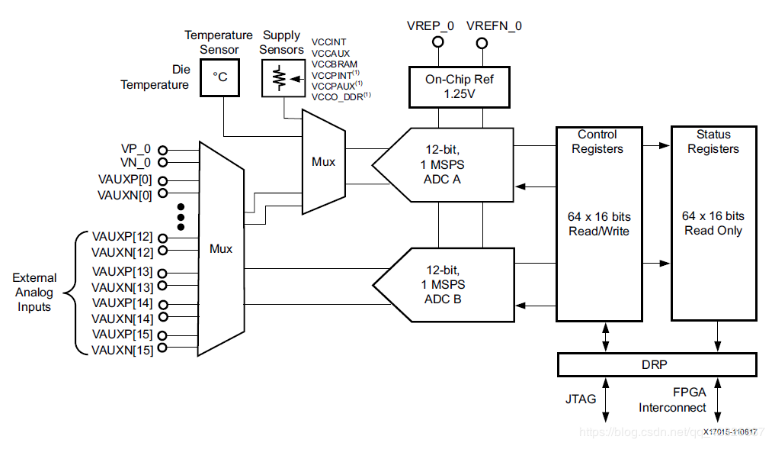

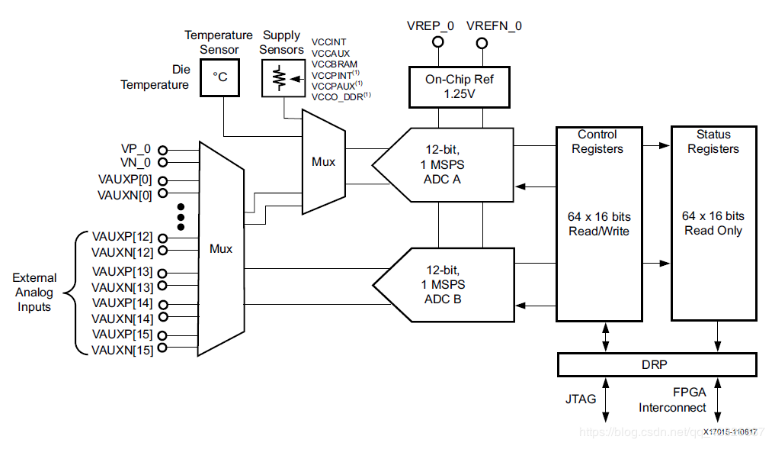

Xilinx7系列內部自帶一個雙通道12位分辨率的高速(1MSPS 1M sample per second)采樣速率的模擬混合信號處理模塊,雙通道的ADC支持單極和差分工作模式,最多支持17路外部

2019-09-10 10:27:36

你好, 我試圖通過使用XADC讀取模擬信號。我有Zynq-7000板。我找不到引腳分配文件。要將模擬信號輸入到從vaux0到vaux15的16個通道,我應該如何與XADC接頭建立輸入連接? 非常感謝。 :)

2020-05-07 08:15:58

`玩轉Zynq連載19——[ex02]基于Zynq PL的歡快流水燈 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-08-28 09:26:47

`玩轉Zynq連載1——Zynq的linux啟動過程更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1概述 簡單的,以ug585中的一張圖來看,從大的方面說

2019-04-16 06:56:32

`玩轉Zynq連載22——[ex03] 基于Zynq PL的PLL配置實例更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-09-06 08:13:18

`玩轉Zynq連載28——[ex50] 第一個Zynq系統工程“HelloZynq” 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接

2019-09-30 12:57:32

`玩轉Zynq連載2——Zynq PS的GPIO外設更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1 概述 Zynq的GPIO外設控制最多54個MIO引腳,也

2019-04-18 16:33:51

`玩轉Zynq連載30——[ex52]基于Zynq PS的GPIO控制 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-10-10 11:21:06

`玩轉Zynq連載31——[ex53] 基于Zynq PS的EMIO控制 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-10-12 17:35:16

介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹.pdf》。3 AXI GP外設配置在zstar_ex53實例的基礎上,需要對ZYNQ7Processing System(PS)配置頁面做更改

2019-11-12 10:23:42

芯片可以做到了最優狀態。因此,對于用Zynq做開發的工程師而言,如何玩轉AXI HP總線就成為了必修課。本實例(zstar_ex56)通過一個簡單的AXIHP總線主機的讀時序和寫時序邏輯,來帶領讀者掌握

2019-11-26 09:47:20

不同通道使用情況下的數據吞吐量。大家可以在此基礎上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹

2019-11-28 10:11:38

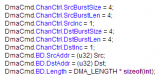

實現模擬電壓采集方式的設置,并讀取轉換后的模擬電壓數據。XADC內部寄存器的映射如圖所示。圖 XADC內部寄存器映射關系截圖在Zynq中,XADC模塊通過AXI GP總線連接到PS。XADC相當于重新

2019-12-03 11:17:44

/Adam-Taylor-s-MicroZed-Chronicles-Part-108-Creating-our-)中描述的方法進行操作。硬件/ ba-p / 665756)但我無法弄清楚HSI是什么或如何打開SDSoC提示。我只需要一個可以在SDSoC設計中使用的ADC。必須有一個更容易/更好的方法來做到這一點,但我會接受任何有效的方法!請幫忙。

2020-05-25 08:18:59

各位大神好,最近在學習xilinx公司的ZYNQ7000系列的開發板,學習XADC,有沒有用過的大神,求給一些學習指導。真不太會用啊!

2020-03-24 05:35:10

本帖最后由 yintengfei 于 2015-6-10 09:14 編輯

拿到板子一段時間 但是實在太忙,前幾天搞個helloworld整的我感覺也立馬不好了。今天主要XADC在ZYNQ

2015-06-09 01:20:07

、雙極和差分等信號類型。在7系列的FPGA中,XADC提供了JTAG和DRP(dynamic reconfiguration port)接口,用于訪問其內部的狀態和控制寄存器。在ZYNQ

2020-09-01 17:35:31

VDDRData; // init_platform(); //printf("Adam Edition MicroZed Using Vivado How To Printf \n

2019-09-10 17:45:31

你好根據ZYNQ-7000 TRM,板載最小/最大電源軌[VCCINT,VCCAUX& VCCBRAM]等...可以使用內部XADC電源傳感器進行監控。你能否分享一下procdure或命令來監控linux環境中的ZYNQ rails。謝謝

2020-04-13 06:44:08

視頻太大了,無法上傳,直接分享百度網盤了介紹一下內容【黑金ZYNQ7000系列原創視頻教程】20.Linux下的GPIO操作【黑金ZYNQ7000系列原創視頻教程】19.Linux下的hello

2016-11-14 21:04:04

最近在研究zynq7000系列的開發板,上面帶有兩個12位的XADC,有沒有用過的大神給些學習的指導,要是能有小例子就更好啦,謝謝大家了

2016-05-04 15:21:51

想買個二手STM8S系列開發板,已經玩轉了的希望轉手給我,價格請加Q1922234601詳談。

2016-08-12 15:23:27

如何玩轉STM32-F429系列

2021-10-13 06:45:39

如何玩轉STM32-F429系列控制器?

2021-11-12 06:06:38

/Adam-Taylor-s-MicroZed-Chronicles-Part-180-All-about-the-Xilinx/ba-p/756988但該芯片自帶板,Zynq 7020屬于Zynq家族。是否可以在電路板上使用它?如果沒有,支持reVision的官方(Xilinx / AVNet / ...)主板的最低成本是多少?籌碼怎么樣?

2019-10-10 06:25:58

應該是“Xilinx模擬混合信號模塊”,是FPGA中的一個硬核。在7系列FPGA中,XADC提供了DRP和JTAG接口,用于訪問XADC的狀態和控制寄存器。Zynq中添加了第三個接口,稱作PS-XA...

2021-12-27 06:18:43

如何零死角玩轉STM32-F429系列

2021-10-13 08:47:02

如何零死角玩轉STM32-F429系列?

2021-10-12 07:43:14

你好我在Zynq 7010設計上添加了一個UART 16550 IP,中斷直接連接到Zynq INTC。在petalinux中導入硬件設計后,pl.dtsi結構似乎沒問題,但是當我編譯圖像并啟動板

2020-04-08 07:50:34

我昨天才發現我的兩塊microZED板都有相同的MAC地址(第一次將它們同時插入網絡)。通過u-boot代碼,我看到MAC地址被烘焙到環境中(在zync_common.h中)。#define

2019-09-16 14:57:55

網絡上關于ARTY板和XADC的所有教程完全混淆了我。我是FPGA的新手,所以我希望你能在這里回答我的問題。我有一個ARTY板,我想將它與模擬輸入信號連接,并在XADC向導中看到正弦輸出,只顯示

2020-08-25 12:19:45

:366 298 GIC 29 twd23:0 0 GIC 62 43c40000.xadc81:0 0 zynq-gpio 52 rv8803147:0 0 GIC 57 cdns-i2c148

2020-04-24 09:43:51

By Adam Taylor 到目前為止的文章中,我們已經研究了MicroZed開發板上使用以太網的數據傳輸問題。我們還沒有涉及片上外設通信的問題:實時時鐘,非易失內存以及獨特的傳感器。這些通信涉及到I2C或者SPI總線。

2017-01-13 11:07:11 748

748 在Adam Taylor玩轉MicroZed系列的前期部分中,我們介紹了IP棧的概念。(見Adam Taylor玩轉MicroZed系列第79部分:Zynq SoC以太網第3部分)接下來就是在我們的設計中使用該協議棧了。SDK開發環境允許我們創建BSP的時候包含一個輕量級的IP棧(lwIP)。

2017-01-13 11:17:11 1033

1033

By Adam Taylor 在本系列博客的前兩部分中,我們研究了帶有Zynq SoC PS(處理器系統)的以太網MAC(介質訪問控制層),包括深入探討了一個MAC使用范例。以太網MAC是一個基礎的構建模塊,它允許我們實現一個IP棧,然后因此給我們的工程創建聯網條件。

2017-01-13 11:24:11 669

669 By Adam Taylor 在約束系列的最后,我們講講關聯布局宏(RPM)的約束。RPM允許你在FPGA的布局中將DSP、FF、LUT和RAMS等資源組合在一起。與PBlocks不同,RPM并不

2017-11-10 14:49:02 748

748 By Adam Taylor 在過去一周中,我接到了很多不同人的來信,他們正在使用以Zynq為基礎的開發工具。他們非常想知道怎么樣去把MicroZed系列博客教程應用到他們所選擇的硬件平臺上。加上

2017-02-08 02:12:49 426

426

研究了相關的時序約束后,在設計中我們也不能忽視所能運用到的物理約束。一個工程師最常用的物理約束是I/O管腳的放置和與每個I/O腳相關的參數定義(標準、驅動能力等)。然而,還有其它類型的物理約束: ?放置約束——定義元件位置 ?布線約束——定義信號布線 ?I/O腳約束——定義I/O腳位置和I/O腳參數 ?配置約束——定義配置方法 按照慣例,有一些約束獨立于這些組之外。Vivado套件有三個約束,并且主要用于網表: ?DONT_TOUCH——用來防止

2017-02-08 02:20:11 206

206

By Adam Taylor 在先前的博客中我們研究過I/O約束,下一個合乎邏輯的步驟就是研究如何在我們的設計中用FPGA進行放置和布線約束。使用放置約束的原因如下:為了幫助實現時序,或者

2017-02-08 02:22:11 238

238 通過前面的學習,我們已經對Zynq系列的PL和PS部分已經有了相當多的了解。其中有關約束的部分我們曾經提到過但是沒有重點關注。約束可以添加特定的信息到你的設計,并在綜合工具和實現工具中可以得到實現

2017-02-08 03:58:43 645

645

上周的博客中我們完成了硬件的搭建,并且把硬件部分導入到SDK,見Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通過寫一個簡單的程序

2017-02-08 05:53:11 303

303

: AXI4-Stream—使用DMA時,從Zynq SoC的XDAC流式接口到內存映射,提供高性能輸出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 286

286 在我最新一期發表的博客中介紹了如何通過Zynq PS(處理器系統)內部的AXI總線接口尋址Zynq SoC的XADC模塊以及如何調試與分析你的應用程序。但是我們仍然沒有看到Zynq SoC的一個非常

2017-02-08 08:14:11 153

153

在本系列上一篇博客中,我們學習了解了使用XMD和XSDB來調試我們的應用和系統。然而為了確保我們的應用在性能上是優化的,另一個非常重要的方面就是對應用程序進行詳細分析。 分析不同于調試,就分析功能

2017-02-08 09:53:00 130

130 在此系列博客的前面幾期中,我們已經可以運行示例應用并獲得用于分析的程序運行數據。運行分析器可以生成一個gmon.out格式的文件,它包含了分析數據。當應用程序運行自然結束或者通過SDK來終止應用程序

2017-02-08 09:56:49 180

180

在上一篇的MicroZed系列博客中,我們學習了兩種與XADC進行通信的方法:Zynq SoC 的AXI或者DevC接口。通過在每個驅動程序中輸出XADC的基地址,我演示了這兩種XADC通信方法

2017-02-08 09:58:42 221

221 前面的幾篇博客中,我們通過介紹怎樣驅動CCD的一些知識了解了PicoBlaze的一些特點,同時也知道了通過Zynq PS(處理器系統)可是實現PicoBlaze的動態可重配置,我覺得在這次博客當中

2017-02-08 11:11:37 134

134 安富利近期宣布發布售價$299的MicroZed 工業物聯網入門套件(IIoT Starter Kit)。該套件基于安富利MicroZed SoM,板上搭載Xilinx ZYNQ Z7010 SoC

2017-02-08 11:57:12 243

243 作者:Adam Taylor 在上一篇博客中我們已經知道了如何動態更新PicoBlaze的運行程序,現在我們要學習一個完成的設計應用。一個非常相關的應用就是驅動CCD(電荷耦合元件)圖像傳感器,因為

2017-02-08 12:31:33 144

144 正如我上周所講,Petalinux是Xilinx針對Zynq SoC提供的Linux官方版本。為了攫取該版本最大資源,我們需要創建自己的版本。這就需要我們在Linux環境下進行開發。現在,并不是

2017-02-08 13:58:08 164

164 如果在我們的虛擬機上已經安裝好了SDK,我們就得使用Linux操作系統來建立我們自己的應用程序。這通常需要對 Zynq SoC的硬件重新進行定義。 首先,我們要做的就是確保將VIVADO設計套件以及

2017-02-08 13:58:11 300

300 我必須承認這是一篇我從來不希望要寫的博客。當我開始寫玩轉MicroZed時,我還不確定每周一篇寫到52篇。達到這樣的里程碑并擁有150,000的瀏覽量,我想回顧過去的一年在Zynq SoC上涵蓋

2017-02-08 15:35:37 108

108 作者:Adam Taylor 在上一篇博客中我們了解了Zynq SoC的OCM(片上存儲器) ,利用它可以實現在AMP模式下內部處理器內核之間的通信。現在我們將寫一些程序代碼將這個設備(OCM)利用

2017-02-08 15:38:12 606

606 作者:Adam Taylor 在最近的幾篇博客中,我們花了主要精力講解操作系統和AMP(非對稱多進程處理),接下來我們希望看到Linux系統在microzed板上運行。我們目前還沒有討論

2017-02-08 15:42:12 529

529

作者:Adam Taylor 上篇博客中我們看到了在ZynqSoC的兩塊ARM Cortex-A9 MPCore處理器之間共享數據。我提到方法可以改進——使得更加高效——我們可以使用軟件中斷來進行

2017-02-08 15:47:34 222

222 介紹完操作系統后我將會在Zynq SoC上演示,我打算首先在MicroZed上實現的操作系統就是Micrium公司的uC/OSiii。這是一個硬式實時操作系統,可以點擊這里下載。 該OS已經用于大量

2017-02-08 18:26:11 149

149 最近的幾篇關于MicroZed系列的博客中我們介紹并了解了RTOS(實時操作系統)的概念,既然已經介紹了基本知識,是時候在MicroZed開發板上實現運行我們的第一個操作系統。我們將使

2017-02-08 18:27:06 323

323

作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 在我前面的一篇博客(查看Adam Taylor玩轉MicroZed系列40:MicroZed操作系統第二部分)中,大家已經見識

2017-02-08 18:27:11 202

202 我本來打算在這篇博客中繼續介紹探討運行于Zynq SoC上的操作系統。然而由于上周有人提問過一些關于Zynq SoC外設XADC,中斷和alarms的問題,我認為我們應該快速的了解一下以及我們怎樣

2017-02-08 18:30:02 312

312

在這期博客前面的幾期,我們介紹了驅動Adafruit Neopixels設計實例的解決方案架構。我們使用Vivado方塊圖設計這個解決方案(具體可以查看Adam Taylor玩轉MicroZed系列

2017-02-08 19:05:11 281

281

作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 By Adam Taylor 我們采用基于Zynq的MicroZed板來實現Adafruit NeoPixel驅動器,前后花了

2017-02-08 19:06:11 152

152 到目前為止,我們已經從Zynq/MicroZed系列博客中看到了很多設計的例子,但是這些設計都沒有使用到操作系統。裸板系統對于目前我們博客中涉及到的例子已經足夠滿足設計要求了,但是如果我們想使用更加

2017-02-08 19:09:11 111

111 最近我拿到了一塊MicroZed I/O 擴展板卡,這個擴展板補充完善了MicroZed系統化模塊(SOM)設計方法,通過分解位于MicroZed開發板背面的兩個小型的I/O引腳集管上的I/O引腳

2017-02-08 20:20:29 359

359 中的每一個RGB LED像素的設置。因此我需要在PC(DTE)和MicroZed(DCE)之間實現一個基本的通信協議。 我將要使用Zynq PS中的UART來發送和接收數據,在BSP中,它被聲明

2017-02-09 01:56:30 145

145

作者是Adam Taylor,該文章發表在 第87期XCell期刊 上。Adam經常給XCell期刊投稿,在XCell日報上,他的“MicroZed Chronicles”系列文章已經發表了近30期,最近他成為了e2v科技的系統工程主管。

2019-10-06 17:09:00 3013

3013

Adam Taylor's博客系列講解在基于ARM的Zynq SoC芯片可編程邏輯上實現定點數學函數計算。 我們已經在MicroZed 系列的前期博客中學習了在PL(可編程邏輯)內實現定點運算,現在

2017-02-09 02:07:37 210

210

在上一篇博文中,我介紹了讓人著迷的Adafruit NeoPixel RGB LED,并且大概描述了NeoPixel驅動設計的基本要點。(參見” 亞當泰勒玩轉MicroZed連載31:系統模塊驅動

2017-02-09 03:41:03 280

280

的文章。這篇文章的標題是安富利Zynq系統模塊減少了客戶開發的時間和成本,該文章描述了兩個公司成功的應用安富利基于Zynq的MicroZed系統模塊,第一個例子就是SmartDAQ 1000 智能傳感器平臺(ISP)來自于新墨西哥州的洛斯阿拉莫斯的山風暴儀器(MSI),上圖是這個SmartDAQ 1000?

2017-02-09 04:24:11 121

121 。 與我們在本博客系列中的方法一樣:加上所生成的頭文件作為BSP的一部分。這些頭文件提供了宏和函數,我們可以用來驅動DMA 。我們將在這個示例中加入: Xscugic.h和xil_exceptions.h

2017-02-09 05:47:33 211

211

Adam Taylor's博客系列講解基于ARM的Zynq SoC芯片可編程邏輯實現定點算法以提高性能。 這個博客系列每周發布,迄今為止已經發布了6個月,我們在Zynq SoC處理器系統(PS

2017-02-09 07:58:12 193

193 了解Zynq PS / PL接口之后;到目前為止,我們已經分析了Zynq All Programmable SoC芯片中的PS (處理器系統)與PL(可編程邏輯)之間的接口。

2017-02-10 12:00:11 957

957

我們先來了解一下上節中介紹的Zynq SoC PS/PL接口,我創建一個很簡單的外設,使用的是DSP48E1的DSP邏輯片,依靠這個外設第一個寄存器內的控制字執行乘法,加法或減法。

2017-02-10 12:04:41 469

469

到現在為止,我們知道如何在基于Zynq SoC的系統中例化PicoBlaze 軟核處理器。在這篇博客,我們將繼續探索更多關于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新編譯整個設計。

2017-02-11 07:01:06 926

926 Zynq SoC的處理系統提供額外功能讓我們可以建立一個更加靈活的Zynq 程序下載系統以適應更多工作。

2017-02-11 07:03:11 1053

1053

在以前發布的玩轉MicroZed系列博客中,我們建立了一個基于Zynq的系統,通過使用雙端口RAMS和BRAM(塊RAM)控制器將兩個PicoBlaze處理器核連接到Zynq的PS部分,現在我們將學習一下怎樣實現更新存儲在雙端口RAM中的PicoBlaze處理器的程序。

2017-02-11 07:05:11 943

943

如何獲得FreeRTOS演示并且在MicroZed上運行。FreeRTOS由Real Time Engineering公司開發,為小容量和極快運行速度的嵌入式系統提供幫助。

2017-02-11 10:03:12 1513

1513

在上一篇博客中成功地演示了FreeRTOS并在基于Zynq的MicroZed板上運行之后,顯然我們想要能夠編寫我們自己的應用程序。因此,我們將首先舉一個簡單的例子。我們將配置Zynq SoC的XADC并且在串行鏈路上輸出結果。

2017-02-11 10:03:13 1019

1019 1、 簡介 XADC是zynq芯片內部進行溫度和電壓檢測的模塊,通過(Xilinx Wiki - xadc.html)這篇wiki可以知道,XADC控制器有兩種表現形式,一種是位于PS內部,即文檔

2018-06-30 14:24:00 2738

2738

在Zynq SoC內部使用XADC可以極大提高系統集成度,而且實現起來非常簡單直觀。賽靈思Zynq?-7000 All Programmable SoC配套提供一個帶有2個12位模數轉換器(ADC

2017-11-18 13:28:02 2860

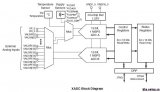

2860 Zynq器件XADC模塊包括2個12比特1 MIPS的模數轉換器和相關的片上傳感器,模數轉換器能為系統應用提供通用目的的高精度的模擬接口,下圖是XADC模塊的框圖。

2018-07-02 03:31:00 20064

20064

Zynq SoC架構的主要優勢之一就是能夠通過在器件的可編程邏輯內構建外設來加快處理速度。 這是Adam Taylor 計劃編寫的Zynq-7000 All Programmable SoC實際操作

2018-01-12 03:50:33 824

824

經過這幾年的市場磨礪,Zynq-7000 FPGA SoC器件平臺在開發者中的認知度和接受度越來越高,這種“ARM處理器+可編程邏輯”的創新架構,可以幫助開發者在設計中找到高性能與靈活性的完美平衡,對此大家也心知肚明。 但是在實際的應用中,想要玩轉Zynq這種“異構”平臺,并非信手拈來這樣簡單。

2018-06-26 06:40:00 8504

8504 Adam Taylor討論了使用Zynq?和Zynq UltraScale +?SoC開發圖像處理應用程序時學到的一些技巧

2018-11-30 06:37:00 2023

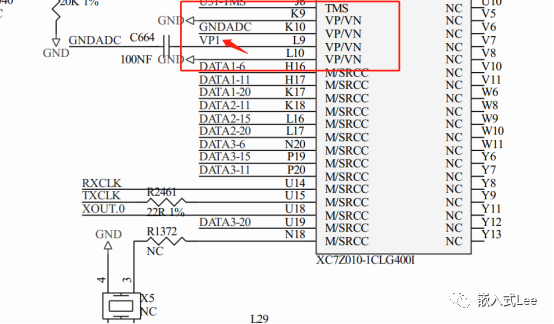

2023 XADC模擬輸入包括專用模擬輸入VP/VN和16組復用模擬信號輸入VAUX(15:0);XADC轉換結果可以通過動態重配接口(DRP)或者JTAG接口輸出;告警信號可通過ALM(7:0)輸出,并有專用的溫度告警信號OT。

2019-02-14 17:30:41 10608

10608

Zynq片內XADC應用筆記(深圳中遠通電源技術有限公司)-應用筆記簡要描述Xilinx?Zynq?XADC的相關資源及若干種應用。參考文檔:?ug480:7Series_XADC

2021-09-22 18:36:50 14

14 應該是“Xilinx模擬混合信號模塊”,是FPGA中的一個硬核。在7系列FPGA中,XADC提供了DRP和JTAG接口,用于訪問XADC的狀態和控制寄存器。Zynq中添加了第三個接口,稱作PS-XA...

2022-01-05 14:26:11 10

10 XADC具有兩個12位的ADC,具有獨立的跟蹤和保持放大器,模擬多路復用器(最多17個外部模擬輸入通道)以及片上散熱和片上電壓傳感器。可以將兩個ADC配置為同時采樣兩個外部輸入模擬通道。采樣保持

2022-07-11 11:03:38 1600

1600 Xilinx 7系列FPGA全系內置了一個ADC,稱呼為XADC。

2023-08-15 09:19:25 697

697

電子發燒友App

電子發燒友App

評論