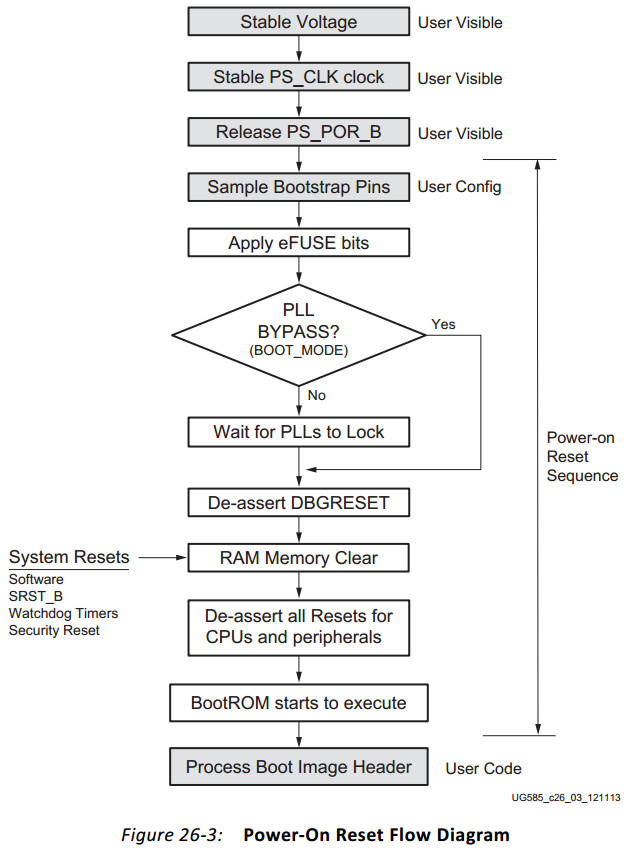

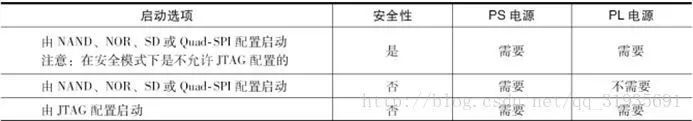

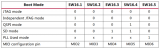

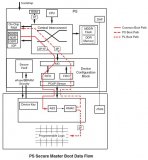

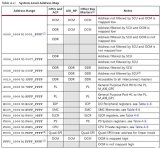

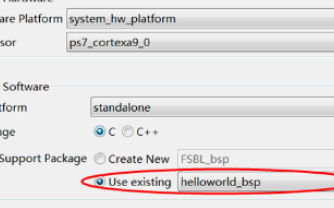

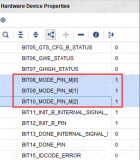

無任是用CPU作為系統(tǒng)的主要器件,還是用FPGA作為系統(tǒng)的主要器件,系統(tǒng)設計中首先要考慮到的問題就是處理器的啟動加載問題。XILINX推出的ZYNQ可擴展處理平臺,片內(nèi)包括兩個高性能的ARM Cortex A9硬核(稱為處理系統(tǒng)processing system (PS))和FPGA(稱為可編程邏輯programmable logic (PL)),在基于該平臺的系統(tǒng)設計時具有極大的靈活性,本文就ZYNQ系統(tǒng)設計時都會遇到啟動加載問題作一個拋磚引玉的描述,如有不當之處還請高手斧正。^_^一、器件配置單元ZYNQ器件都帶有一個器件配置單元(device configuration unit (DEVCFG) ),該模塊由PS控制,提供軟件控制下的PS和PL的初始化和配置功能。以前單個FPGA器件提供的下載方法已經(jīng)不在適用,PL的配置下載必須在PS的參與下進行。Zynq-7000的器件配置單元包括下面的PS單元:①CPU②OCM(引導ROM和共享RAM)③ 部分頂層總線和外設④PS器件配置模塊在PL側(cè),下面的單元也將參與:①PLS器件配置邏輯和接口② 解密/鑒權硬件③存儲在eFUSE單元或者電池備份RAM(BBRAM)內(nèi)的解密密鑰下圖為PS器件配置子系統(tǒng)框圖:[[wysiwyg_imageupload:1338:]]提供的關鍵特性如下:A.提供3種不同的PS配置方法,包括2種主模式和1種從模式。① 加密主模式② 非加密主模式③ 非加密從模式B.3種不同的主模式啟動源①NOR FLASH②NAND FLASH③QSPI FLASHC:JTAG非加密從模式D:用AES-256和HMAC (SHA-256)進行PS/PL的加密下載E:高速配置用的主DMA接口F:100 MHz 32-bit PCAP流接口H:SoC加密調(diào)試功能在系統(tǒng)上電復位時,PS采樣專用bootstrapping signals引腳電平來決定從什么方式引導器件。這個引導過程是由一個Cortex A9核執(zhí)行片內(nèi)的ROM code實現(xiàn)的,ROM code的功能是初始化L1 cache和基本的總線系統(tǒng),加載相應的NAND, NOR, Quad-SPI, and PCAP驅(qū)動,從指定接口加載第一級BOOTLOADER(the first stage boot loader (FSBL))到片內(nèi)執(zhí)行。由于OCM RAM大小有限制,第一級BOOTLOADER大小最大為256KB。用戶只需要按要求提供啟動映像和設置正確的bootstrapping signals引腳電平,系統(tǒng)上電復位時由ROM code自動加載到片內(nèi)并且程序調(diào)轉(zhuǎn)到啟動映像,此時系統(tǒng)的全部控制功能交由用戶的啟動映像控制,用戶如要實現(xiàn)的第二級BOOTLOADER功能由啟動映像的程序?qū)崿F(xiàn)。對于加密配置方法,需要用到AES-256解密代碼和SHA-256簽定(簽名)算法, PS需要用PL內(nèi)硬連線的AES-256 和SHA-256模塊,這時就要求在加密配置情況下PL就必須上著電,既使系統(tǒng)并不配置PL部分也需上電。器件的加密密鑰可以由用戶選擇是存儲在片內(nèi)的eFUSE單元(具有掉電非易失性)或者內(nèi)部電池供電的BBRAM內(nèi)(具有掉電易失性,適用于安全級別要求更高的場合), 下表總結了配置模式和相關信息:[[wysiwyg_imageupload:1339:]]二、PS非加密主模式配置過程這種模式下PS啟動映像是直接從外部非易失存儲器(NAND, NOR, Quad-SPI)內(nèi)加載到片內(nèi)OCM內(nèi),隨后PL映像可以直接配置到PL內(nèi),整個過程如下圖示:[[wysiwyg_imageupload:1340:]]PL映像的配置可由配置接口模塊用DMA來高速實現(xiàn),在非加密情況下速度可以達到400MB/s, 加密情況下速度可以達到100MB/s, 這在FPGA需要部分重配置時十分有用。三、PS加密主模式配置過程PS加密主模式用到了位與片內(nèi)PL部分的硬件AES-256解密模塊和SHA-256模塊來對PS啟動映像進行解密和完整性鑒定,器件密鑰存儲在片內(nèi)的eFUSE單元或者內(nèi)部BBRAM內(nèi),當PS加載成功后,用戶可以選擇用下面缺省的PL引導過程來配置PL部分,如下圖示:[[wysiwyg_imageupload:1341:]]其中配置PL時的比特流既可以是已經(jīng)經(jīng)過AES-256加密的比特流,也可以是先經(jīng)過PS先進行解密后成為明文比特流送到PL內(nèi),這個過程的保密性由用戶選擇使用。在保密ROM引導階段如果PS完整性鑒定失敗,CPU就立即斷言PROG_B信號而清除PL內(nèi)容,同時發(fā)出一個加密復位信號,這使PS內(nèi)部的RAM和寄存器進行復位,然后CPU進入睡眠模式,系統(tǒng)只有重復上電才能復位。PL配置發(fā)生在BOOT的第二階段,這個過程完成可以由用戶選擇自己的方法在任何時間內(nèi)來配置一次或多次,并不需要一定按缺省的PL引導過程來配置PL部分。四、啟動模式引腳ZYNQ器件有5個啟動模式信號mode[4:0],用來指出從哪里啟動,是否是JTAG模式,PLL是否旁路等。另外有兩個電壓模式信號vmode[1:0]用來指明MIO BANK的電壓模式,vmode[1:0] 信號和mode[4:0] 信號通過上拉和下拉來確定電平值,上拉和下拉電阻建議為20k歐姆,上拉是連接到VCCO_MIO0電壓,下拉是連接到地。系統(tǒng)在釋放PS_POR_B復位腳后這些啟動模式引腳信號會被采樣3個PS_CLK時鐘用來確定啟動方式。vmode[1:0] 信號和mode[4:0] 信號對應的I/O管腳為MIO[8:2],各信號具體含義如下:①Mode[0] 用來指明是否是JTAG 模正。②Mode[3:1]用來選擇啟動源,是從NOR Flash還是從NAND Flash還是從QSPI啟動。③Mode[4]用來使能PLL。④Vmode[1:0] 用來配置I/O BANK電壓。這些信號和MIO管腳的對應關系如下表表示:[[wysiwyg_imageupload:1342:]]注:上表中X表示不關心。實際設計中,由于MIO管腳數(shù)量有限(只有54個),且只分為兩個BANK(MIO Bank 0對應管腳為PS_MIO[15:0],PS_CLK,PS_POR_B;MIO Bank 1對應管腳為PS_MIO[53:16],PS_VREF_MIO和PS_SRST_B),并不建議系統(tǒng)設計為從并行的NOR Flash啟動,因為這種方式NOR Flash占用的MIO管腳數(shù)量大多(大于40個管腳),系統(tǒng)設計為從NAND Flash或QSPI啟動都可以,這兩種方式占用的MIO管腳數(shù)量要少些,NAND Flash的優(yōu)點是容量比較大,缺點是讀寫速度要慢些(典型速度10MB/s), QSPI也是一種NOR Flash,不過接口是四線串行接口,可以獲得比較高的讀寫速度(典型速度50MB/s),如果系統(tǒng)希望從其它方式如USB, Ethernet, SD/SDIO等方式啟動,這都需要用戶在第一級啟動映像內(nèi)自行設計啟動引導代碼。以上拋磚引玉,歡迎大家補充說明,主要參考文獻為Zynq-7000 Extensible Processing Platform Technical Reference Manual,大家可到XILINX官方網(wǎng)站上下載來仔細研究。

ZYNQ器件的啟動配置方法

- FPGA(591969)

- 賽靈思(130433)

- Xilinx(119164)

相關推薦

淺談zynq啟動,BootROM和FSBL等的執(zhí)行過程

本文主要介紹zynq啟動過程,主要包括BootROM和FSBL等的執(zhí)行過程。 硬件啟動過程 1. 重新上電或POR復位后進行硬件啟動過程 2. 掃描啟動引腳設置,并存入只讀寄存器

2020-11-23 14:53:52 8313

8313

8313

8313

ZYNQ常用外設設計:malloc與memcpy的使用方法

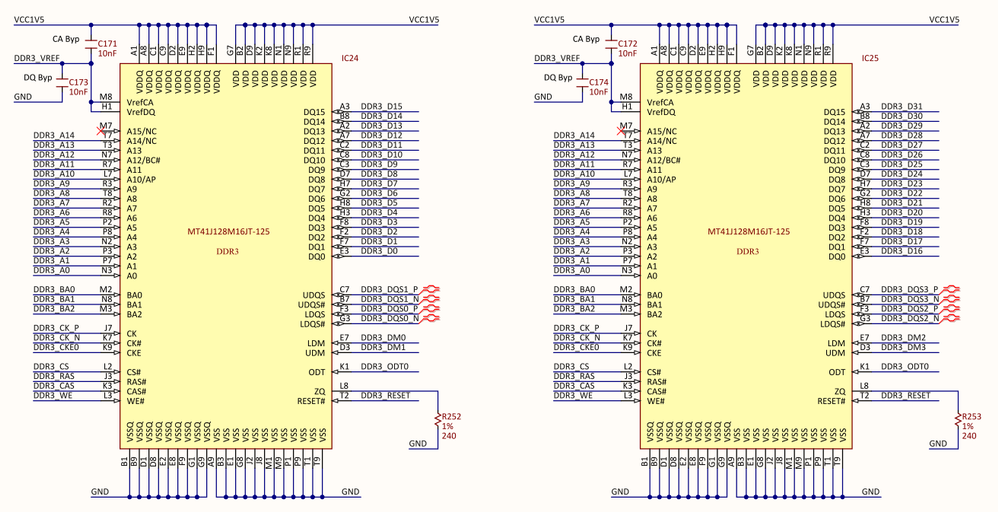

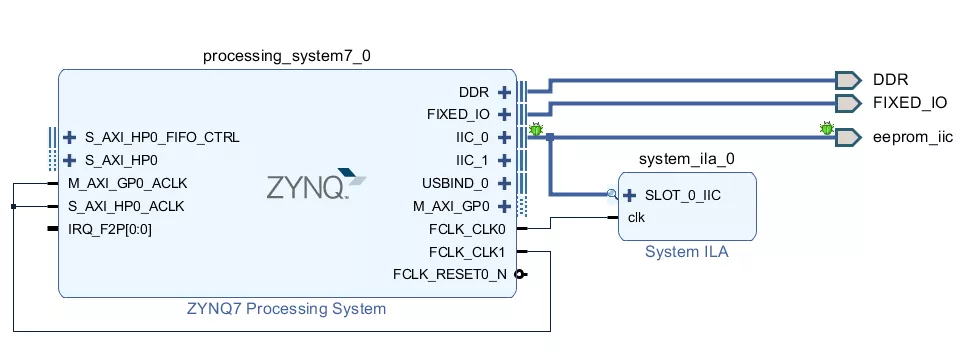

Controller接口,如果外部硬件連接了DDR器件,于是在ZYNQ Processing System中正確配置了相應的信號和參數(shù)后,DDR就可以成為ZYNQ的內(nèi)存,在SDK中可以直接使用memcpy

2020-11-27 12:18:15 6687

6687

6687

6687

基于zynq7000的linux系統(tǒng)搭建設計

基于zynq7020器件來搭建Linux系統(tǒng),描述搭建Linux系統(tǒng)過程中PL側(cè)的配置以及對u-boot,kenel,桌面系統(tǒng)的配置和

2020-11-30 11:56:01 3490

3490

3490

3490

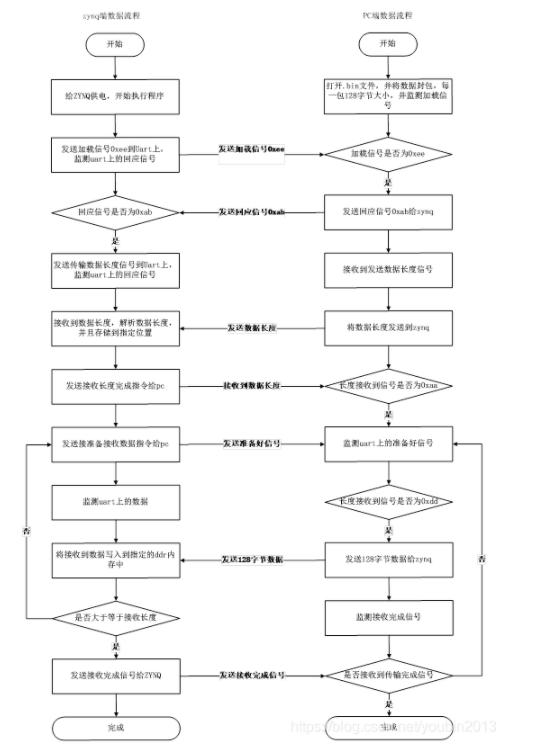

ZYNQ開發(fā)案例之ZYNQ的UART加載

加載方法 ZYNQ的啟動鏡像是由FSBL程序(bootloader),PL配置文件(硬件比特流文件),應用層軟件三個部分組成,其通過SDK的軟件生成工具把三個部分按規(guī)定的格式拼湊成一個.bin文件

2020-12-05 10:15:37 4952

4952

4952

4952

PYNQ案例(二):ZYNQ與PYNQ的區(qū)別與聯(lián)系

Zynq可擴展處理平臺是賽靈思新一代 FPGA的可編程技術的產(chǎn)品系列。與采用嵌入式處理器的FPGA不同,Zynq產(chǎn)品系列的處理系統(tǒng)不僅能在開機時啟動,而且還可根據(jù)需要配置可編程邏輯。采用這種方法

2020-12-25 14:15:48 5212

5212

5212

5212詳解Zynq的兩種啟動模式

Zynq-7000AP SOC器件有效利用了片上CPU來幫忙配置,在沒有外部JTAG的情況下,處理系統(tǒng)(PS)與可編程邏輯(PL)都必須依靠PS來完成芯片的初始化配置。 ZYNQ的兩種啟動模式:從BootROM主動啟動,從JTAG被動啟動。

2023-08-02 09:33:09 736

736

736

736

通過JTAG啟動Linux的方法和腳本

在 AMD SoC 器件(AMD Zynq 7000 SoC,AMD Zynq UltraScale+ MPSoC,AMD Versal Adaptive SoC),常見的啟動方式是通過加載外部

2023-12-22 10:27:25 506

506

506

506

ZYNQ7010使用JTAG燒錄程序到NAND運行的方法

51一樣應用,那么你可以參考一下。參考文章EBAZ4205 ZYNQ 7Z010 裸機程序NAND固化 JTAG調(diào)試方法如果本文有地方寫的不清楚可以跳轉(zhuǎn)過去看下。本文主要是硬件改動,軟件燒錄與測試方法與參考文章并無區(qū)別。可以先看完本文的硬件改動后再看參考文章,改動的地方主要是原理圖中標紅色框的這兩個電阻(

2022-01-06 07:52:41

ZYNQ與DSP之間SRIO通信的設計實現(xiàn)

User Defined文件夾處右擊,并在彈出的菜單中點擊“New Target Configuration”新建目標配置文件:在打開的目標配置文件中,需要配置仿真器類型、器件型號,我們實驗用的仿真器為

2023-02-21 14:51:50

ZYNQ怎么修改PHY的初始化配置

本帖最后由 一語奔馳 于 2016-11-25 15:18 編輯

我ZYNQ外接的PHY是88E1512,現(xiàn)在有一個系統(tǒng),外接的是88E1510的PHY,但是我想使用88E1512來實現(xiàn)光口

2016-11-25 14:21:28

ZYNQ的GPIO相關資料推薦

ZYNQ 分為 PS 和 PL 兩部分,那么器件的引腳(Pin)資源同樣也分成了兩部分。ZYNQ PS 中的外設可以通過 MIO(Multiuse I/O,多用輸入/輸出)模塊連接到 PS 端的引腳

2022-02-08 07:27:16

ZYNQ(FPGA)與DSP之間SRIO通信實現(xiàn)

XinesC6657.gel。設置完Gel文件后,點擊Save: 1.1.3.2.2.2 啟動目標配置文件在已經(jīng)創(chuàng)建并設置好的目標配置文件處右擊,并在彈出的菜單中點擊Launch Selected Configuration

2023-02-02 21:43:20

Zynq DDR控制器參數(shù)配置資料介紹

說一下配置的過程,如何從PDF中拿出參數(shù)來首先看一下Zynq MPSoC支持的DDR,這里的手冊是UG1085,首先是最大支持多少

2022-04-19 17:56:03

Zynq UltraScale + MPSoC USB 3.0 CDC器件類設計

Zynq?UltraScale+?MPSoC USB 3.0控制器由兩個獨立的雙角設備(DRD)控制器組成。兩者都可以單獨配置為在任何給定時間用作主機或設備。USB 3.0 DRD控制器通過高級可

2019-01-03 09:59:50

Zynq-7000 SoC提供 FPGA 資源

與內(nèi)置于 TE0720 系列 Trenz Electronic SoM(采用 Zynq Z-7014S 和 Zynq Z-7020 器件)中的 FPGA 容量相比,集成到 TE0723-03M

2018-08-31 14:43:05

Zynq在非JTAG模式下的啟動配置流程

是怎樣實現(xiàn)對自己的配置? 這也是本文將要和大家共同討論的問題。 Zynq的啟動流程 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器

2021-01-08 16:33:01

Zynq在非JTAG模式下的啟動配置流程

本文主要與大家分享了Zynq在非JTAG模式下的啟動配置流程,旨在讓大家對Zynq的三階段啟動模式有一個具體的認識,希望大家多多交流。

2021-03-17 07:36:30

Zynq無法設置為從QSPI閃存啟動怎么解決?

為了確保正確回退到金啟動,AR#67221規(guī)定QSPI閃存的D2和D3數(shù)據(jù)條應連接到4K7上拉。但是看看Zynq xc7z030fbg676,這些引腳也可用作配置模式引腳。QSPI D2 =模式引腳

2020-06-09 17:24:31

zynq上linux內(nèi)核啟動

各位i大神,小弟最近遇到了zynq上無法啟動linux的問題,不知道哪里的錯誤都是按照xilinx官網(wǎng)做的。。thanks

2014-07-07 12:40:30

zynq上的中斷方法是什么

你好我想制作一個具有中斷信號的自定義IP。我正在尋找這個中斷信號的規(guī)格。我在哪里可以找到這個規(guī)格?例如水平或邊緣檢測器如果它是水平檢測器,它應該停留多長時間?我正在使用ZYNQ ZC706板。如果你

2019-04-10 11:49:23

zynq這種FPGA器件相對以往傳統(tǒng)FPGA有哪些優(yōu)勢和劣勢

zynq是xilinx的新一代的嵌入ARM硬核的SOC,請問1、這種FPGA器件相對以往傳統(tǒng)FPGA有哪些優(yōu)勢和劣勢?2、針對圖像和視頻處理的,這兩類哪一種器件更適合?3、相同價格的情況下,ARM硬核的引入相比傳統(tǒng)FPGA是否會降低zynq的性價比和靈活度?

2022-11-07 15:28:45

Xilinx-ZYNQ7000學習筆記

Xilinx-ZYNQ7000系列-學習筆記(3):系統(tǒng)復位與啟動一、復位ZYNQ-7000 SoC系統(tǒng)中的復位可以由硬件、看門狗定時器、JTAG控制器或軟件產(chǎn)生,可用于驅(qū)動系統(tǒng)中每個模塊的復位信號

2022-01-25 07:05:36

Zybo Zynq開發(fā)板可以創(chuàng)建多個設備配置嗎?

大家好,我正在與SoC邁出第一步,我目前正在使用Zybo Zynq開發(fā)板。我有一個簡單的問題:是否可以創(chuàng)建多個設備配置,為每個配置生成比特流并將比特流存儲在內(nèi)存或其他內(nèi)容中,以便創(chuàng)建一個說“配置庫

2020-05-20 10:44:19

freeRTOS 如何移植到zynq芯片

因為最近要用到zynq芯片,我希望能在zynq芯片上使用freeRTOS,但是弄不明白怎么移植進去。一般xillinx sdk在工程里面添加操作系統(tǒng)的方法是,在repository里先安裝相應的庫

2020-06-11 04:35:29

petalinux內(nèi)核無法在Zynq 7020上從閃存啟動的解決辦法?

大家好,我使用zynq 7020開發(fā)板,其自定義架構不支持SD卡,但支持QSPI閃存。我通過在SDK中使用以下bif文件創(chuàng)建zynq啟動映像來構建.msc文件 [bootloader] zynq

2020-07-30 16:24:39

【Z-turn Board試用體驗】+Zynq7000啟動流程介紹

Zynq-7000 Extensible Processing Platform,是一個可擴展處理平臺,簡單說就是有個FPGA做外設的A9雙核處理器。所以,它的啟動流程自然也和FPGA完全不同,而與

2015-07-22 20:42:50

【Z-turn Board試用體驗】+板上資源Zynq7000啟動流程的學習

做一遍也不害怕!Zynq7000,是一個可擴展處理平臺,簡單說就是有個FPGA做外設的A9雙核處理器。所以,它的啟動流程自然也和FPGA完全不同,而與傳統(tǒng)的ARM處理器類似。Zynq7000支持從多種設備

2015-05-27 20:50:06

【正點原子FPGA連載】第二十章另一種方式編譯ZYNQ鏡像-領航者ZYNQ之linux開發(fā)指南

使用source命令執(zhí)行petalinux的環(huán)境配置腳本settings.sh,如下所示:source /home/zynq/petalinux/v2018.3/settings.sh圖 31.1.2 運行

2020-09-15 15:24:44

【正點原子FPGA連載】第十八章Linux內(nèi)核移植-領航者ZYNQ之linux開發(fā)指南

Xilinx官方ZYNQ EVK開發(fā)板對應的Linux內(nèi)核,發(fā)現(xiàn)其不可以在正點原子的ZYNQ開發(fā)板上啟動,所以本節(jié)我們就參考Xilinx EVK開發(fā)板的設置,修改相應的配置使其在正點原子的領航者開發(fā)板上能啟動

2020-09-14 15:42:54

介紹zynq調(diào)試時內(nèi)存讀寫的常規(guī)方法

1、ZYNQ調(diào)試時內(nèi)存讀寫的一般方法假設查看的數(shù)據(jù)從地址0x0開始,大小為4個字節(jié)。打開示例工程并啟動調(diào)試。在菜單欄選擇Window->Show View->Memory打開內(nèi)存視圖。原作者: 嵌入式男單第九名 劉廣信

2022-07-05 15:30:17

使用Zynq設備和Tandem配置的PCIe BOOTUP時間有什么要求?

嗨,PCIe-Spec定義在穩(wěn)定供電后100ms,PCIe設備必須為鏈路訓練做好準備。使用7系列Zynq設備無法達到此時間。我使用了兩種方法來減少啟動時間: - 優(yōu)化FSBL以達到SPI控制器的最大

2020-06-09 16:42:15

使用IMPACT(ISE)將比特流下載到Zynq設備中而無需啟動ARM?

大家好,有沒有一種簡單的方法可以使用IMPACT(ISE)將比特流下載到Zynq設備中而無需啟動ARM?我知道這可以用Vivado完成。TIA

2020-07-21 15:11:31

關于zynq啟動的問題,求達人解答!

[/td][td]關于zynq啟動的問題,求達人解答![img][/img]查閱了些資料,發(fā)現(xiàn)zynq是分部啟動的。1)其中arm部分是否可以軟重啟,自己收到復位命令后進行從新加載PS部分;2)有

2013-08-23 10:49:00

如何使用Windows在Zynq 7000主板上啟動linux?

如何使用Windows在Zynq 7000主板上啟動linux?在Linux中我有終端可以請你建議是否有任何Windows終端以上來自于谷歌翻譯以下為原文How can I boot linux

2019-04-09 13:12:21

玩轉(zhuǎn)Zynq連載1——Zynq的linux啟動過程

`玩轉(zhuǎn)Zynq連載1——Zynq的linux啟動過程更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1概述 簡單的,以ug585中的一張圖來看,從大的方面說

2019-04-16 06:56:32

玩轉(zhuǎn)Zynq連載22——[ex03] 基于Zynq PL的PLL配置實例

`玩轉(zhuǎn)Zynq連載22——[ex03] 基于Zynq PL的PLL配置實例更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-09-06 08:13:18

玩轉(zhuǎn)Zynq連載28——[ex50] 第一個Zynq系統(tǒng)工程“Hello Zynq”

Zynq,而是如何新建Zynq系統(tǒng)模塊、配置PS的參數(shù)、導出硬件、新建軟件工程并且在線板級運行起來。流程很重要,大家在開始的時候總要先走一遍流程了解開發(fā)的全貌,然后再細細把玩,逐個精通。 2 新建

2019-09-30 12:57:32

玩轉(zhuǎn)Zynq連載29——[ex51] 制作裸跑程序的啟動文件BOOT.bin

Zynq的啟動原理,建議參考文檔《玩轉(zhuǎn)Zynq-基礎篇:Zynq的啟動過程.pdf》。 2 導出硬件信息并啟動SDK參考文檔《玩轉(zhuǎn)Zynq-工具篇:導出PS硬件配置和新建SDK工程》。 3 創(chuàng)建FSBL工程

2019-09-30 14:11:59

請問如何配置rtc中斷線到zynq?

喜如何用zqq的irq no 52到MIO26(gpio中斷)引腳配置中斷線?我正在使用以下devicetree配置i2c1:i2c @ e0005000 {compatible =“cdns

2020-04-24 09:43:51

請問如何在zynq和virtex-7之間配置x8,x16,x32的數(shù)據(jù)行?

我正在使用zynq芯片和VIRTEX-7設計電路板。我想知道在Zynq PL引腳和Virtex-7 IO引腳之間選擇配置數(shù)據(jù)線(例如Slave SelectMAP X8,X16,X32)的方法。在

2020-06-05 10:31:19

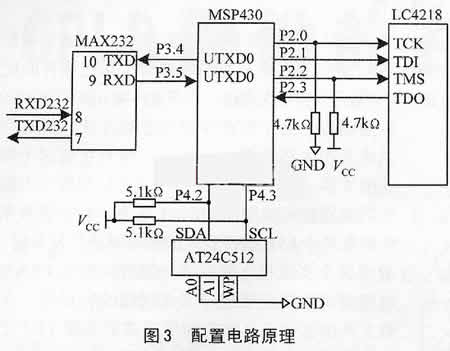

FPGA器件的在線配置方法

摘要:介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數(shù)據(jù)的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統(tǒng)的設計方法及實現(xiàn)

2006-03-13 19:36:49 448

448

448

448Lattice CPLD器件的在系統(tǒng)動態(tài)配置

以下是引用片段: 摘要: 介紹一種利用微控制器動態(tài)配置CPLD器件的方法。將配置文件存放在存儲器中,配置文件中的控制代碼驅(qū)動在微處理器中運行的配置引擎;將配置文件中的配置信息通過JTAG口移入

2009-06-20 10:44:21 3034

3034

3034

3034

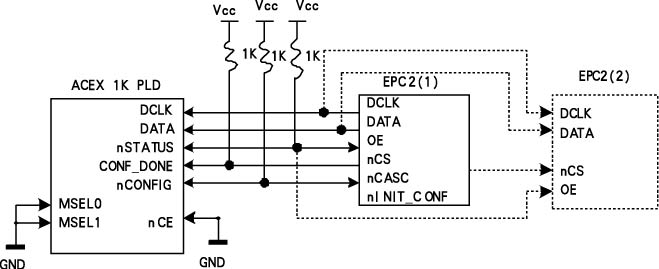

ACEX 1K系列CPLD配置方法探討

摘 要 :介紹ACEX 1K系列器件的配置方法,對幾種方法進行了分析對比,并著重論述了應用配置器件配置 ACEX 1K系列器件的優(yōu)點。

關鍵詞 :CPL

2009-06-20 10:51:54 478

478

478

478

FPGA器件的在線配置方法

摘要: 介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數(shù)據(jù)的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統(tǒng)的設計方法及

2009-06-20 10:57:26 1062

1062

1062

1062

RealviewMDK中啟動代碼的配置詳解

Realview MDK不僅提供了默認的啟動代碼,而且這些啟動代碼可以通過圖形化界面配置。啟動代碼的圖形化配置界面非常類似于Web網(wǎng)頁的界面,甚至后臺處理的腳本也與Html語言十分接近。下面將詳細的解析圖形化界面的設計與配置。 啟動代碼的配置界面是由程序中的

2011-02-24 16:06:53 86

86

86

86ZYNQ學習 —— 啟動流程分析及各環(huán)節(jié)文件生成流程(ZedBo

網(wǎng)絡資料收集,關于啟動流程的一些注意點,關于開發(fā)板ZYNQ系列的包括MIZ702

2016-05-11 17:30:15 3

3

3

3Zynq大家族新增單ARM 核的Zynq 器件,為你提供一個、二個、四個或者六個 ARM 微處理器核的多種選擇

今天,賽靈思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎來一個新的產(chǎn)品系列及三款最新器件! 新的產(chǎn)品系列被稱為Zynq Z-7000S系列,三款新器件分別為

2017-02-08 04:25:13 517

517

517

517

閑話Zynq UltraScale+ MPSoC(連載4)

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC啟動 熊貓君在這里討論啟動(Boot),主要是想聊它的啟動設備和啟動方式。看看啟動設備是否廣泛支持,啟動

2017-02-08 08:31:11 358

358

358

358

閑話Zynq UltraScale+ MPSoC(連載4)

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC啟動 熊貓君在這里討論啟動(Boot),主要是想聊它的啟動設備和啟動方式。看看啟動設備是否廣泛支持,啟動

2017-02-08 08:31:11 339

339

339

339

關于生成從Flash和SD卡啟動的鏡像文件的方法

在《ZYNQ-7000使用總結(3)——PS和PL部分配合使用》中,我們已經(jīng)可以將PL與PS部分一起使用,并且通過JTAG下載到板子運行。對于ZYNQ,有多種啟動方式,比如從JTAG啟動、從QSPI

2019-10-06 16:48:00 2095

2095

2095

2095

一文詳解ZYNQ器件的啟動配置方法

在電子系統(tǒng)設計中,無任是用CPU作為系統(tǒng)的主要器件,還是用FPGA作為系統(tǒng)的主要器件,系統(tǒng)設計中首先要考慮到的問題就是處理器的啟動加載問題。

2018-07-12 08:27:00 9919

9919

9919

9919

ZYNQ 7系列FSBL的啟動過程與配置方法

ZYNQ 7系列所有可編程器件均可以在安全模式下通過靜態(tài)存儲器配置或者在非安全模式下通過JTAG或者靜態(tài)存儲器配置。 (1)JTAG模式主要用于開發(fā)和調(diào)試 (2)NAND、并行NOR、串行NOR

2017-11-17 10:25:52 22027

22027

22027

22027

Xilinx Zynq-7000系列安全配置策略

ZYNQ7000與傳統(tǒng)FPGA有著巨大的差異,它將自己定位為一款All Programmable Soc(軟硬件可編程片上系統(tǒng)),視其為以FPGA作為外設的雙核ARM A9處理器更加準切。它的啟動

2017-11-17 16:04:37 7989

7989

7989

7989構建可啟動的系統(tǒng)鏡像的過程

Zynq系列器件。如果是Mircroblaze器件請忽略。產(chǎn)生的“.BIN”啟動文件可以利用(PROM programmer)拷貝到Flash或直接拷貝到SD第一個FAT分區(qū)。

2017-11-21 11:41:15 968

968

968

968Zynq器件三種主要類型的存儲控制接口解析

基于Zynq器件的嵌入式開發(fā)時,我們不可避免地需要規(guī)劃設計使用什么樣類型和多大地內(nèi)存與FLASH,本文就ZYNQ器件的存儲控制器作一個拋磚引玉的描述,以期大家對它有個基本了解,如有不當或需要補充之處

2017-11-22 08:23:54 6195

6195

6195

6195

在Zynq SoC上實現(xiàn)裸機(無操作系統(tǒng))軟件應用方案

Zynq?-7000 All Programmable SoC在單個器件上實現(xiàn)了ARM處理功能與FPGA邏輯獨特的組合,因此需要雙重的配置過程,同時需要考慮處理器系統(tǒng)和可編程邏輯。工程師會發(fā)

2018-01-12 11:17:15 5494

5494

5494

5494Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

本文試圖搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492

2492

2492ZYNQ-7000如何生成從Flash和SD卡啟動的鏡像文件

ZYNQ-7000如何生成從Flash和SD卡啟動的鏡像文件 將PL與PS部分一起使用,并且通過JTAG下載到板子運行。對于ZYNQ,有多種啟動方式,比如從JTAG啟動、從QSPI(即Flash

2018-05-28 11:42:14 5883

5883

5883

5883

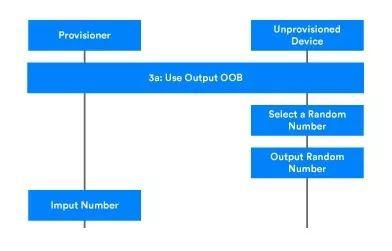

藍牙m(xù)esh安全的啟動配置流程分析

1、發(fā)送Beacon信號:如果未經(jīng)啟動配置的設備支持PB-ADV承載層,則其作為未經(jīng)啟動配置設備Beacon進行廣播;如果使用的是PB-GATT承載層,則發(fā)送可連接的廣播數(shù)據(jù)包。這就向啟動配置設備(Provisioner)表明未經(jīng)啟動配置的設備已做好準備,可進入啟動配置流程。

2018-09-28 08:22:00 5578

5578

5578

5578

如何使用Xilinx SDK啟動電路板及利用Zynq DRAM進行測試

在本視頻中,我們將學習如何使用Xilinx SDK啟動電路板,利用每個驅(qū)動程序提供的應用示例并測試各種外設。

我們將詳細介紹Zynq DRAM測試,并了解如何利用它進行測試。

2018-11-29 06:50:00 4666

4666

4666

4666如何配置和練習U-Boot的USB主機功能

了解如何配置和練習U-Boot的USB主機功能。

這允許在Zynq上使用USB記憶棒進行數(shù)據(jù)存儲和檢索,包括二次啟動。

2018-11-29 06:38:00 2554

2554

2554

2554Zynq-7000 All Programmable SoC器件的I/O標準

了解設計人員在使用Zynq-7000 All Programmable SoC器件時可用的不同I / O,從標準I / O到串行收發(fā)器以及模擬輸入。

2018-11-26 06:36:00 2547

2547

2547

2547Xilinx FSBL如何操作啟動Zynq器件

了解Xilinx FSBL如何操作以啟動Zynq器件。

包括程序執(zhí)行概述,調(diào)試技巧以及有關特定引導設備的信息。

還包括FSBL角度的啟動安全性簡要概述。

2018-11-23 06:32:00 4237

4237

4237

4237ZYNQ-7000如何生成從Flash和SD卡啟動的鏡像文件

ZYNQ-7000如何生成從Flash和SD卡啟動的鏡像文件 將PL與PS部分一起使用,并且通過JTAG下載到板子運行。對于ZYNQ,有多種啟動方式

2018-12-01 08:38:18 7278

7278

7278

7278

ZYNQ的啟動原理和配置

在ps的控制下,可以實現(xiàn)安全或非安全的配置所有ps和pl。通過zynq提供的JTAG接口,用戶可以在外部主機的控制下對zynq進行配置,zynq不支持最開始就配置pl的過程。

2019-05-15 11:41:31 7190

7190

7190

7190

ZYNQ開發(fā)雙核運行原理及過程

ZYNQ是一個可擴展平臺,就是有FPGA作為外設的A9雙核處理器,它的啟動流程與FPGA完全不同,而與傳統(tǒng)的ARM處理器類似,ZYNQ的啟動配置需要多個處理步驟。

2020-12-05 10:48:58 5388

5388

5388

5388Zynq UltraScale+ 器件與PL DNA不同的值

Xilinx 用兩個 96 位獨特器件標識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統(tǒng) (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2022-02-08 14:19:49 1149

1149

1149

1149

Zynq 在非 JTAG 模式下的啟動配置流程

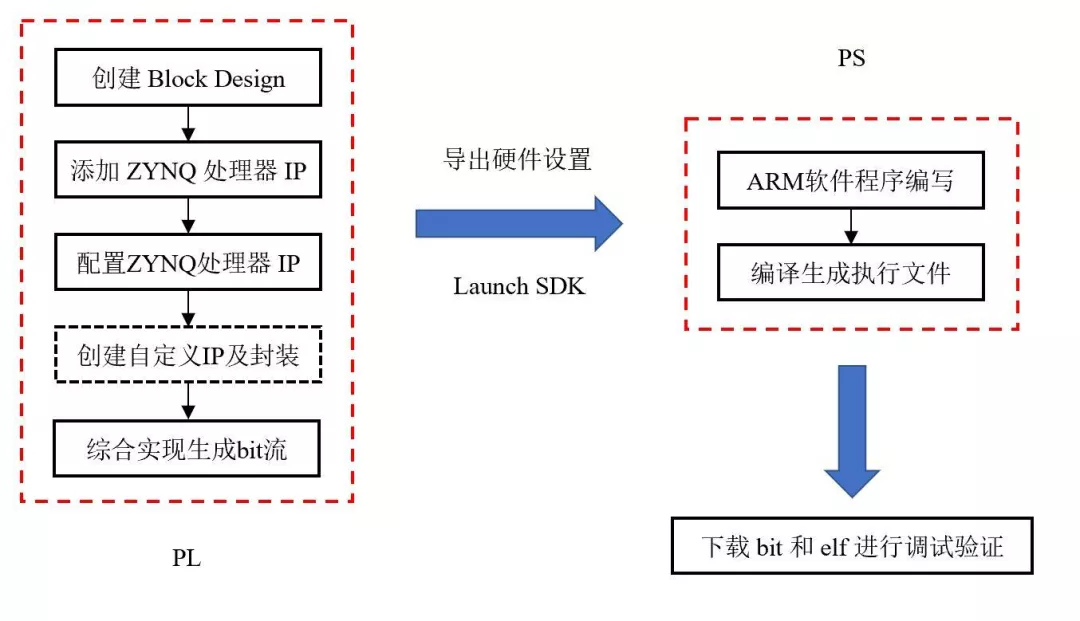

初學 Zynq 的時候,都是按照慣例打開 Vivado 軟件,然后實現(xiàn) Zynq 可編程邏輯硬件部分PL的設置后,把硬件部署導出,再打開 SDK 進行 ARM 核的軟件部分 PS 編程設計,最后再將

2022-02-08 11:48:37 1021

1021

1021

1021

Zynq的啟動與配置過程詳解

初學 Zynq 的時候,都是按照慣例打開 Vivado 軟件,然后實現(xiàn) Zynq 可編程邏輯硬件部分PL的設置后,把硬件部署導出,再打開 SDK 進行 ARM 核的軟件部分 PS 編程設計,最后再將

2021-01-26 07:30:29 20

20

20

20FPGA、Zynq和Zynq MPSoC三種器件的特點介紹

。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點。 2.1 技術時間線 進一步介紹之前,需要指出這三種

2021-04-02 17:20:14 13783

13783

13783

13783

如何在 Vitis 中調(diào)試 Zynq UltraScale 器件啟動鏡像

在本篇博文中,我們將探討如何在 Vitis 中調(diào)試 Zynq UltraScale 器件啟動鏡像。這些啟動鏡像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中

2021-06-01 15:35:45 2709

2709

2709

2709

Zynq-7000 SoC 啟動鏡像布局

為處理海量數(shù)據(jù)、復雜算法、超低延時的應用提供數(shù)字化加速驅(qū)動力是賽靈思一直的目標,為此,賽靈思研發(fā) Bootgen 工具支持將二進制文件縫合在一起并生成器件啟動鏡像。定義了多個屬性和參數(shù)作為創(chuàng)建啟動

2021-08-27 14:11:30 2832

2832

2832

2832FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法

FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法(深圳市村田電源技術有限公司)-FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13

13

13【Zynq UltraScale+ MPSoC解密學習2】Zynq UltraScale+的電源系統(tǒng)

功耗域2.2 低功耗域2.3 全功耗域2.4 PL功耗域2.5 PMU一、電源優(yōu)化方法相對于上一代Zynq器件,Zynq UltraScale+更加...

2021-11-06 21:06:04 6

6

6

6Zynq SDK 驅(qū)動探求(五)軟件動態(tài)重配置硬件比特流

在 Xilinx Zynq 器件中,硬件可編程邏輯 PL 是作為一項外設掛載在 ARM 處理器系統(tǒng)中的,那么 PL 硬件的配置自然也就由處理器負責。本文...

2022-02-07 11:18:27 1

1

1

1ZYNQ的啟動流程

ZYNQ7000 SOC 芯片可以從 FLASH 啟動,也可以從 SD 卡里啟動, 本節(jié)介紹程序 FLASH 啟動的方法。Zynq7000 SOC 芯片上電后,最先運行的是ARM端系統(tǒng)(PS

2022-05-07 09:41:35 5019

5019

5019

5019FPGAs,Zynq和Zynq MPSoC器件的特點

Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進化版本。Zynq是賽靈思發(fā)布的集成PL(FPGA)和PS設計的最早的一代產(chǎn)品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點.

2022-08-15 09:16:38 1629

1629

1629

1629Zynq在非JTAG模式下的啟動配置流程

在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實現(xiàn)的。需要注意的是,與傳統(tǒng)的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進行直接啟動配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 986

986

986

986?在配置FPGA器件時的常見問題及其解決方法

FPGA器件配置方式分三大類:主動配置、被動配置和JTAG配置。 主動配置:由FPGA器件引導配置操作過程。 被動配置:由計算機或控制器控制配置過程。上電后,控制器件或主控器把存儲在外部存儲器

2022-11-17 12:15:10 1141

1141

1141

1141Zynq UltraScale+ RFSoC器件介紹

介紹一下Xilinx公司的新一代Zynq UltraScale+ RFSoC器件,可用于LTE、5G、SDR、衛(wèi)星通信等無線平臺。

2023-05-22 10:38:59 3966

3966

3966

3966

Zynq UltraScale+ MPSoC中的隔離方法

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC中的隔離方法.pdf》資料免費下載

2023-09-13 17:11:48 1

1

1

1Zynq UltraScale+器件封裝和管腳用戶指南

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+器件封裝和管腳用戶指南.pdf》資料免費下載

2023-09-13 10:30:45 1

1

1

1基于zynq7020器件來搭建Linux系統(tǒng)

Zynq器件將arm和FPGA結合,利用了兩者各自的優(yōu)勢,arm可以實現(xiàn)靈活的控制,而FPGA部分可以實現(xiàn)算法加速,這大大擴展了zynq的應用。比如深度學習加速,圖像處理等等。PL側(cè)表示FPGA的邏輯部分,PS側(cè)為arm端以及一些AXI接口控制部分,二者實際上通過AXI接口實現(xiàn)通信和互聯(lián)。

2023-11-09 11:28:04 1460

1460

1460

1460

電子發(fā)燒友App

電子發(fā)燒友App

評論