啟動過程

設備配置包含用于初始化和配置ps和pl的所有方法及過程。在軟件控制下,ps內的DevC提供用于初始化和配置ps和pl的手段和方法,在zynq中提供兩個模塊用于控制配置過程:

BootROM,一個靜態存儲塊器塊,當上電復位和暖復位后,有Cortex-A9的CPU執行這個內置程序;

設備配置單元:用于控制JTAG調試訪問和提供連接到AES、HMAC和PCAP模塊的接口,用于實現對芯片內的pl的配置及數據的解密。

在ps的控制下,可以實現安全或非安全的配置所有ps和pl。通過zynq提供的JTAG接口,用戶可以在外部主機的控制下對zynq進行配置,zynq不支持最開始就配置pl的過程。對zynq的配置過程至少包含兩個階段,但是通常要求3個階段。

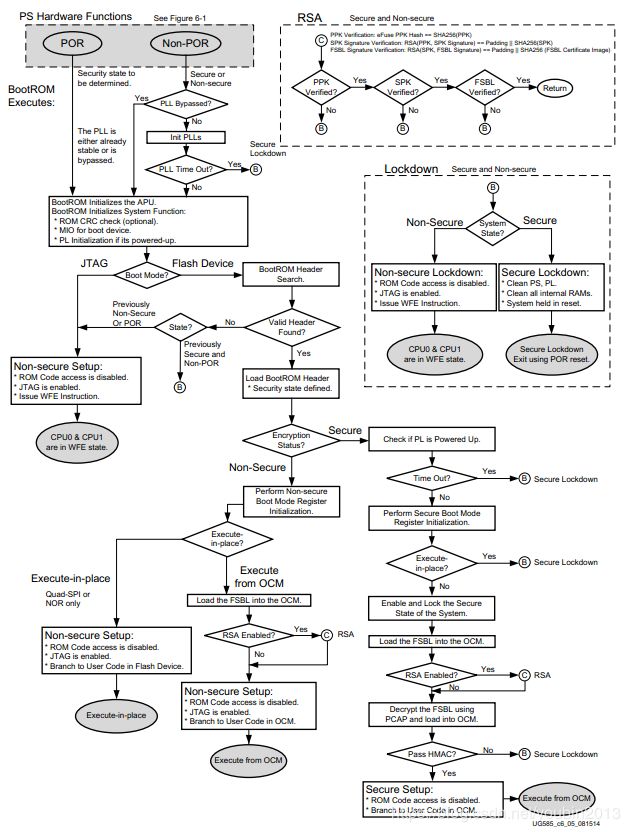

階段0:該階段也稱為BootROM,該階段控制初始設備的啟動。BootROM是上電復位或暖復位后,處理器所執行的用戶不可修改的代碼,該代碼已經固化到zynq的BootROM中;

階段1:在該階段,通常執行第一級啟動引導程序。但是,它也可以是任何用戶控制的代碼;

在該階段,通常執行用戶自己編寫的軟件程序,但是,也可以是第二級的啟動引導程序,該階段完全是在用戶的控制下實現的。

zynq的BootROM

BootROM特性:

提供3種不同的方法,用于配置PS:兩個主模式和一個從模式,即安全、加密的鏡像、主模式;非安全的主模式;通過JTAG的非安全從模式;

支持4種不同的外部啟動源:Quad-SPI Flash、NAND Flash、NOR Flash、SD;

支持使用AES-256和HMAC(SHA-256)的PS安全配置;

支持Soc調試安全性;

從NOR和QSPI芯片內執行配置過程。

當上電復位后,啟動PS配置過程,當禁止JTAG模式時,zynq內的Cortex-A9處理器從片內的BootROM開始執行代碼,BootROM包含用于驅動NADN、NOR、Quad-SPI、SD和PCAP的基本程序代碼。

在BootROM中并不執行對外設的初始化操作,在階段1或該階段之后zynq才對其他外設進行初始化操作,考慮到安全因素,當脫離復位狀態后,Cortex-A9處理器總是PS內所有其他主設備模塊內的第一個設備,當正在執行BootROM時,禁止執行JTAG,以保證安全性操作。

BootROM代碼也負責加載第一啟動鏡像文件,zynq內的硬件支持加載多級用戶啟動鏡像,在第一級啟動之后,用戶負責進一步實現用戶啟動鏡像的加載,當BootROM將控制權移交給fsbl后,用戶負責進一步實現用戶啟動鏡像的加載,當復位操作時,才會重新執行BootROM內的代碼。

BootROM支持加密和不加密的鏡像,此外,當使用芯片內執行特性時,當從線性flash、NOR或QSP直接復制鏡像或執行后,BootROM支持從OCM開始執行階段1鏡像。

在安全啟動CPU時,從安全BootROM運行代碼,并且,對進入的用戶PS鏡像鏡像解碼和認證,將其保存到OCM RAM中,然后,分支進入它,在非安全啟動CPU時,從BootROM運行代碼,如果使用了XIP特性時,在分支跳轉到OCM ROM或Flash內的用戶鏡像時,禁止所有的安全啟動特性,除非使用帶有XIP的啟動,一般將PS啟動鏡像限制到192KB范圍內。

隨后用于PS/PL啟動階段的過程,都是用戶的責任,并且處于用戶的控制下。在zynq中,不允許用戶訪問BootROM中的代碼,在完成階段1安全啟動的過程后,用戶可以繼續執行后續的安全/非安全啟動階段,如果一開始執行的就是非安全的第一個階段,隨后只能執行非安全階段的啟動。

通過PL內硬接線的AES-256和SHA-256模塊,PS實現解密和認證,由于這個原因,在安全啟動任何階段,即使只對PS進行配置,也必須給PL上電,這樣,用戶就可以通過片上的eFUSE單元或片上BRAM,選擇器件的密鑰。

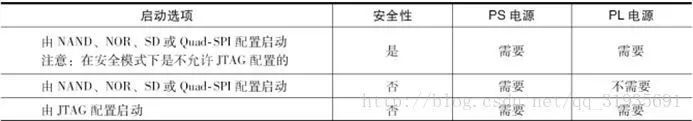

在zynq內支持5種可用的啟動設備,包括NAND、NOR、SD、Quad-SPI和JTAG,其中前4種啟動源用于主模式啟動。

在主模式啟動過程中,Cortex-A9處理器負責將鏡像文件從外部非易失性存儲器加載到片內的PS中。

JTAG只能用于從模式啟動過程,JTAG只支持非安全啟動,一個外部的電腦作為一個主設備,通過JTAG連接,將啟動鏡像加載到OCM,當加載啟動鏡像時,PS CPU保持空閑模式。

BootROM的高層次配置流程如圖所示。

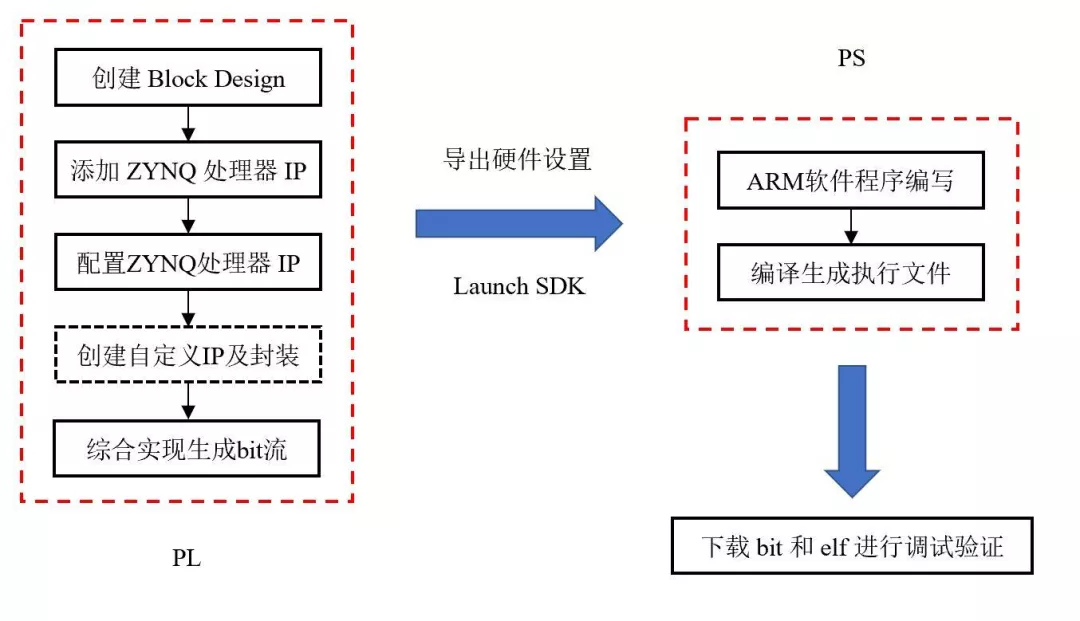

zynq的器件配置接口

設備配置接口結構DevC模塊由3個獨立操作的主模塊構成:

用于連接PL配置邏輯的AXI-PACP接口;

設備安全性管理單元;

一個XDAC接口;

設備配置接口包含一個APB接口,主機使用APB接口配置這3個模塊,并且訪問整個狀態以及實現與PL XADC通信。

AXI-PCAP橋:

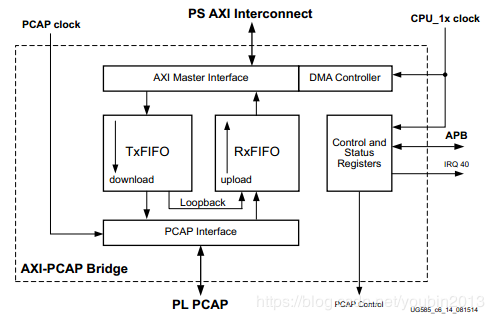

AXI-PCAP橋將32位AXI格式的數據轉換成32位的PCAP協議,反之亦然,這個橋支持配置數據,以并發和非并發的方式下載和上傳,如圖所示。

在AXI和PCAP接口之間存在一個發送和接收FIFO緩沖區,圖中的DMA引擎用于在FIFO和存儲器設備(OCM、DDR存儲器,或者外設存儲器的一個)之間移動數據。

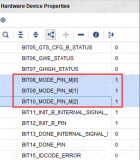

當通過PCAP接口移動數據時,必須給zynq的PL一端供電,通過DevC控制器寄存器的PCAP MODE和PCAP PR比特位,使能PCAP接口,如果發送加密數據,還應該設置QUARTER PCAP RATE EN比特位。

通過DevC模塊內建的DMA引擎,在PCAP接口之間傳輸數據。為了啟動一個數據傳輸過程,必須按照下面的順序寫4個DMA寄存器:DMA源地址寄存器;DMA目的地址寄存器;DMA源長度寄存器;DMA目的長度寄存器。

為了通過PCAP將數據傳輸到PL,目的地址應該設置為0xffffffff。類似的,通過PCAP接口從PL讀數據,源地址應該設置為0xffffffff,必須通過PCAP接口發送加密的PS鏡像,這是由于AES和HMAC引擎都駐留在PL一端。在該情況下,DMA源地址應該設置為一個外部的存儲器接口,而目標地址應該設置為OCM。

DevC的DMA引擎能用于加載不安全的PS鏡像,在加載以前,在雜項控制寄存器內設置PCAP LPBK比特位,這個比特位使能內部的環路,旁路掉PCAP接口,在使用PCAP前,需要再次禁止該比特位,DMA源地址應該設置為一個外部存儲器,而目的地址應該設置為一個OCM或一個有效的外部存儲器接口,如DDR。

PCAP接口也用來回讀PL配置。為了執行回讀操作,PS必須運行軟件代碼,使能產生正確的PL回讀指令,使用兩個DMA訪問周期,回讀一個PL配置。

設備安全性管理:

DevC包含著一個安全策略模塊,提供如下功能:

監控系統安全性,當檢測到沖突的狀態時,能確認一個安全復位,這個狀態能表示不一致的系統配置或篡改;

通過APB接口控制和監視PL配置邏輯;

控制ARM CoreSight的調試器訪問端口DAP和調試級;

提供片上ROM控制。

XADC接口:

讀和寫XADC寄存器;

15個深度的寫命令FIFO和15個深度的讀FIFO(32位寬度);

可編程的FIFO級中斷;

報警中斷;

過溫度中斷;

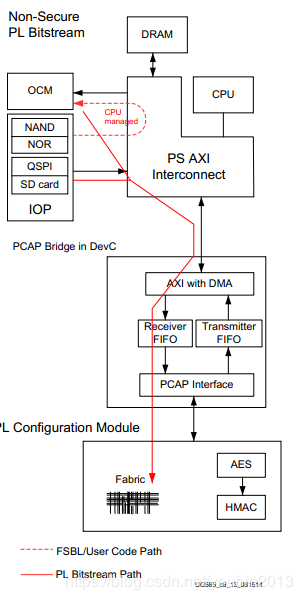

PS主設備非安全啟動

在這個啟動模式下,PS作為主設備。BootROM從選擇的外部存儲器加載一個純文本PS鏡像,如圖3.2所示,在這種情況下,并不要求PL上電,可以使用PS鏡像立即加載或以后加載PL比特流。

配置流程主要步驟如下:

設備上電復位;

BootROM執行:1,讀自舉程序,以確定外部存儲器接口類型;2,讀啟動頭部信息,以確定加密的狀態和鏡像目標;

BootROM使用DevC的DMA,將FSBL加載到OCM或其他有效的目的地址;

通過PCAP,FSBL加載PL比特流。

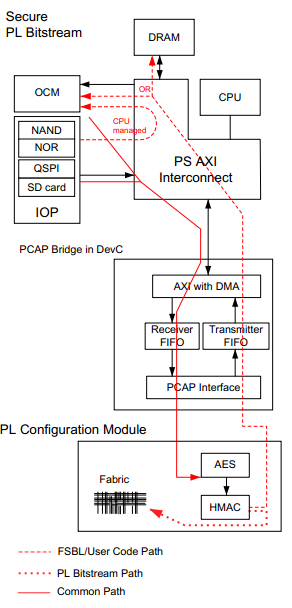

PS主設備安全啟動

在該啟動模式下,PS作為主設備,BootROM從所選擇的外部存儲器加載一個加密的PS鏡像,如圖3.3所示,由于AES和HMAC引擎駐留在PL中,因此要求PL上電來初始化啟動序列,在嘗試解密FSBL前,BootROM驗證PL已經上電,當啟動PS后,可以使用一個加密的比特流配置,或者斷電以后再配置PL。

下面給出了配置流程的詳細步驟:

設備上電復位;

BootROM執行:1,讀自舉程序,以確定外部存儲器接口;2,讀啟動頭部,以確定加密的狀態(安全);3,確認PL上電,開始解密FSBL;

BootROM使用DevC DMA引擎,通過PCAP,將加密的FSBL發送的PL內的AES和HMAC;

PL使用PCAP將解密的FSBL返回到PS,然后,在此將其加載到片內OCM;

關閉BootROM,釋放CPU用于控制FSBL;

FSBL使用一個加密流配置PL。

-

Zynq

+關注

關注

10文章

610瀏覽量

47188

原文標題:ZYNQ的啟動原理和配置

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳解Zynq的兩種啟動模式

玩轉Zynq連載1——Zynq的linux啟動過程

使用Vitis 在EBAZ4205(ZYNQ)礦機上實現"Hello World!"

Zynq在非JTAG模式下的啟動配置流程

Zynq在非JTAG模式下的啟動配置流程

ZYNQ 7系列FSBL的啟動過程與配置方法

Xilinx FSBL如何操作啟動Zynq器件

ZYNQ開發雙核運行原理及過程

Zynq的啟動與配置過程詳解

ZYNQ的啟動原理和配置

ZYNQ的啟動原理和配置

評論