本文首先闡述了FPGA的原理了,其次分析了FPGA比CPU和GPU快的原理,最后闡述了CPU與GPU的區(qū)別。

2018-05-31 09:00:29 15956

15956

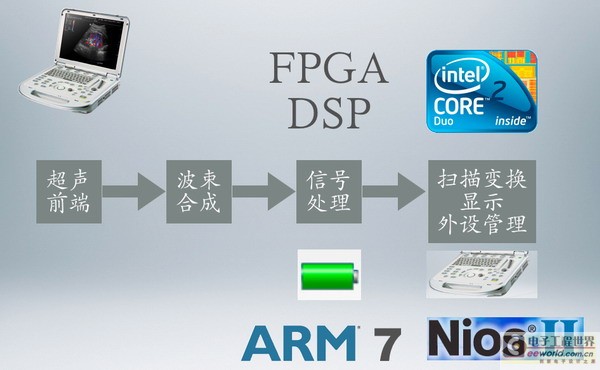

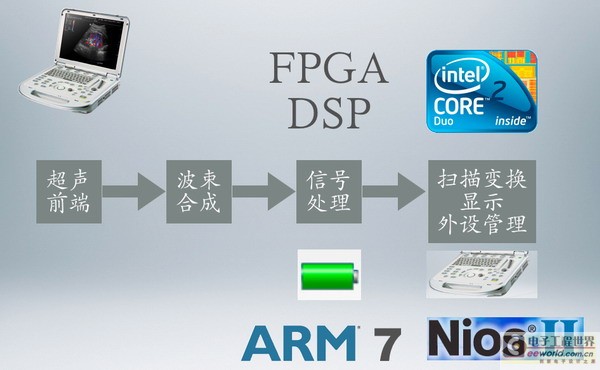

醫(yī)療電子平臺(tái)選擇:FPGA、ARM、X86、DSP還是GPU?

“邁瑞對于處理器平臺(tái)的選擇有兩個(gè)看似矛盾的原則:‘多’和‘少’。其中‘多’是指多樣性,我

2010-04-27 11:27:18 2074

2074

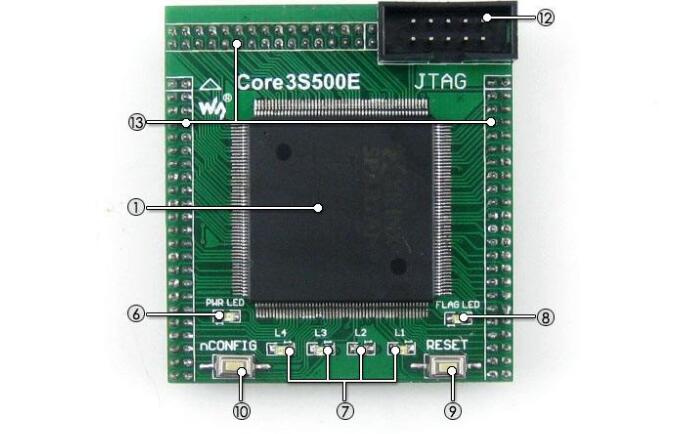

的普及,相信很多人都或多或少了解,什么CPU(中央處理器)和GPU(圖形處理器),但你可能不知道,在芯片領(lǐng)域,還有另外一種鮮為人知的芯片——FPGA。 無論是在軍事領(lǐng)域,還是民用領(lǐng)域都頗具意義。不僅

2016-06-21 11:53:27

現(xiàn)場可編程門陣列 (FPGA) 解決了 GPU 在運(yùn)行深度學(xué)習(xí)模型時(shí)面臨的許多問題

在過去的十年里,人工智能的再一次興起使顯卡行業(yè)受益匪淺。英偉達(dá) (Nvidia) 和 AMD 等公司的股價(jià)也大幅

2024-03-21 15:19:45

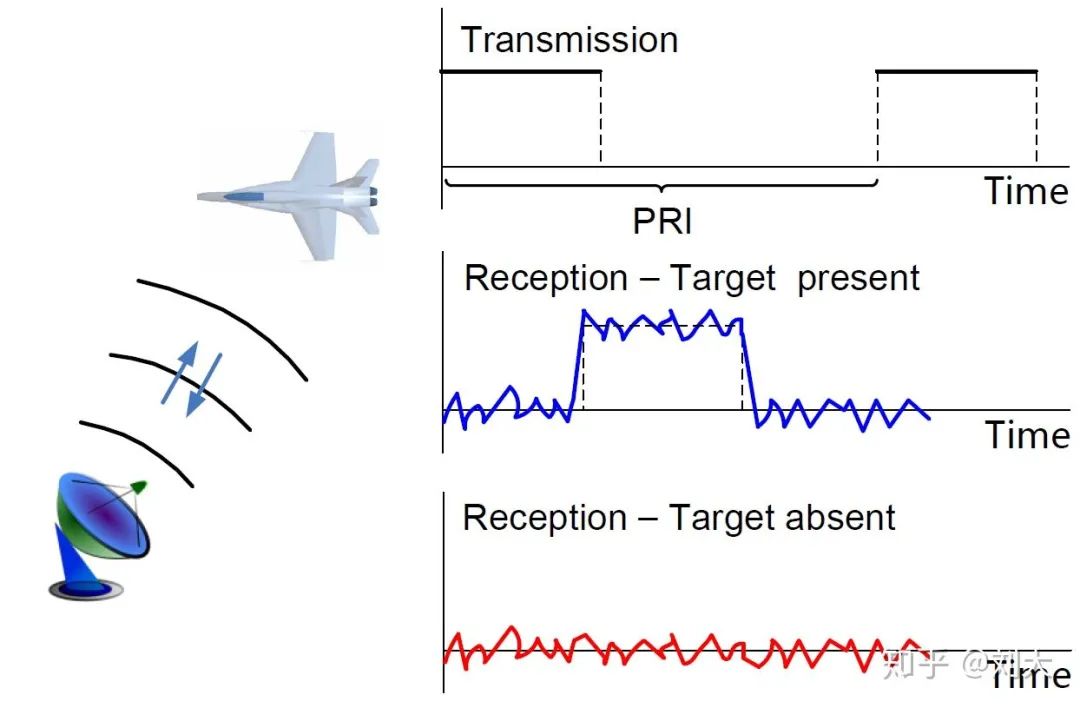

這個(gè)系統(tǒng)的基本原理和部件經(jīng)過發(fā)展后用于民航的空中交通管制后,就成了二次雷達(dá)系統(tǒng)。二次雷達(dá)是在地面站和目標(biāo)應(yīng)答器的合作下,采用問答方式工作,它必須經(jīng)過兩次有源輻射電磁波信號才能完成應(yīng)有的功能。

2019-08-12 08:13:51

執(zhí)行單元,在所有碎片中獨(dú)立執(zhí)行代碼 。盡管有上述約束,但是GPU還是可以有效地執(zhí)行多種運(yùn)算,從線性代數(shù)和信號處理到數(shù)值仿真。雖然概念簡單,但新用戶在使用GPU計(jì)算時(shí)還是會(huì)感到迷惑,因?yàn)?b class="flag-6" style="color: red">GPU需要專有

2016-01-16 08:59:11

本帖最后由 gk320830 于 2015-3-4 21:05 編輯

雷達(dá)手冊第3版(中文)_第25章_雷達(dá)數(shù)字信號處理

2012-08-17 14:11:33

在實(shí)際的外場試飛過程中是不可能實(shí)現(xiàn)的,這也是雷達(dá)信號模擬器對場外試飛的一大優(yōu)勢。FPGA作為高性能數(shù)字信號處理系統(tǒng)中的關(guān)鍵部件,在雷達(dá)信號模擬和雷達(dá)信號采集等方面有著巨大的開發(fā)潛能,采用這些技術(shù)對雷達(dá)

2019-07-10 07:30:35

GPU 和 FPGA。有人說 GPU 好用;有人說 FPGA 靈活可編程;有人說 GPU 運(yùn)算能力強(qiáng),適合對人工智能進(jìn)行“訓(xùn)練”;有人說做“推斷”還得靠 FPGA … 作為程序員,您會(huì)更傾向于用哪一種方案?`

2017-08-23 15:42:16

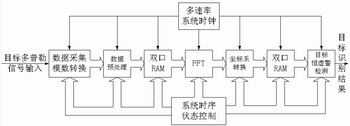

我國目前的海事雷達(dá)大多為進(jìn)口雷達(dá),有效探測距離小,在信噪比降為3 dB時(shí)已經(jīng)無法識別信號。隨著微電子技術(shù)的迅猛發(fā)展,高速A/D(模擬/數(shù)字轉(zhuǎn)換)和高速數(shù)字信號處理器件(Digital

2019-07-04 06:55:39

本文介紹了一種雷達(dá)模目信號產(chǎn)生方法,該方法能夠通過FPGA和DSP實(shí)時(shí)產(chǎn)生具有多普勒頻移的多波束雷達(dá)目標(biāo)回波,其意義在于可以為雷達(dá)信號處理分系統(tǒng)單獨(dú)調(diào)試提供數(shù)據(jù)來源,從而不必等待天線陣面的真實(shí)數(shù)據(jù),這樣可以加快科研進(jìn)度,也方便整機(jī)聯(lián)試時(shí)查找問題。

2011-07-13 09:09:26

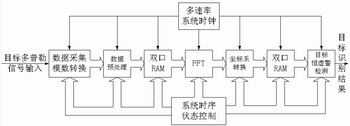

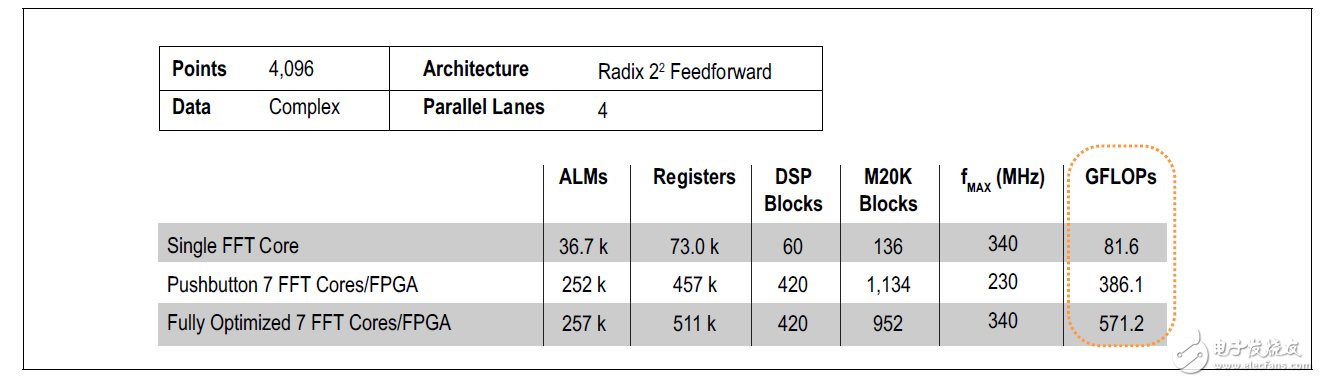

模數(shù)轉(zhuǎn)換、FFT快速、準(zhǔn)確的要求,并且具有高度集成、高可靠性和可編程等特點(diǎn),減少了系統(tǒng)硬件開發(fā)周期,所以選用基于FPGA來實(shí)現(xiàn)雷達(dá)信號處理系統(tǒng)的設(shè)計(jì)。回映電子是一家基于Edge-AI技術(shù)的個(gè)護(hù)健康

2021-12-27 17:08:50

王玲,邱軍海,王世橋(煙臺(tái)工程職業(yè)技術(shù)學(xué)院山東煙臺(tái)264006)線性調(diào)頻信號可以獲得較大的壓縮比,有著良好的距離分辨率和徑向速度分辨率,所以線性調(diào)頻信號作為雷達(dá)系統(tǒng)中一種常用的脈沖壓縮信號,已經(jīng)

2019-07-08 07:38:45

在實(shí)際的外場試飛過程中是不可能實(shí)現(xiàn)的,這也是雷達(dá)信號模擬器對場外試飛的一大優(yōu)勢。FPGA作為高性能數(shù)字信號處理系統(tǒng)中的關(guān)鍵部件,在雷達(dá)信號模擬和雷達(dá)信號采集等方面有著巨大的開發(fā)潛能,采用這些技術(shù)對雷達(dá)

2019-07-15 06:48:33

處理器不斷從FPGA芯片的FIFO中讀出A/D轉(zhuǎn)換后的雷達(dá)接收數(shù)據(jù),經(jīng)過運(yùn)算處理得出噪聲的均方根值,再計(jì)算出雷達(dá)信號的判決門限值寫進(jìn)FPGA芯片的電平接收寄存器中,以進(jìn)行有用信號的判定處理。3 系統(tǒng)的算法

2018-08-15 09:43:14

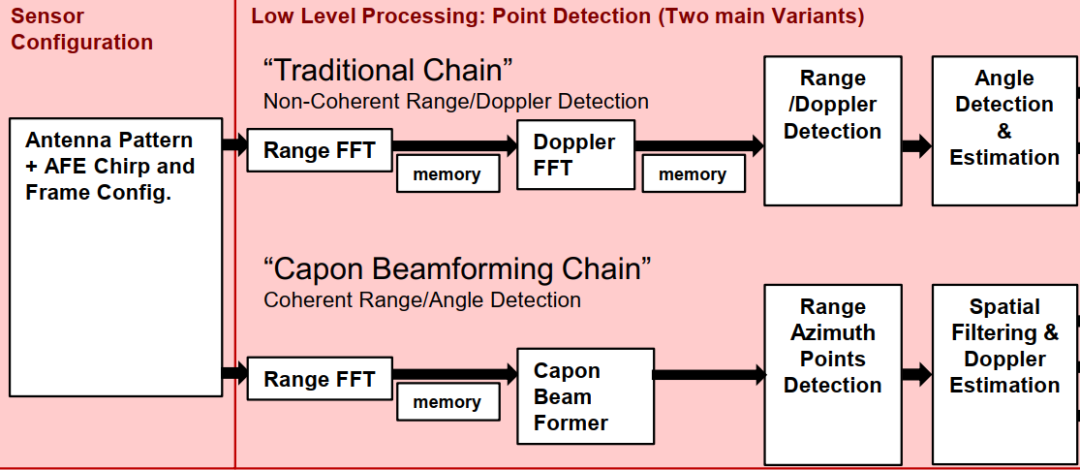

使用SoC FPGA,實(shí)現(xiàn)汽車雷達(dá)的數(shù)字化處理本白皮書介紹使用Altera? 低成本Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢

2013-11-13 15:56:28

本文以FPGA為核心構(gòu)建了一種通用的雷達(dá)回波信號實(shí)時(shí)模擬系統(tǒng)。該系統(tǒng)采用FPGA作為回波信號模擬的運(yùn)算單元,充分利用了FPGA資源豐富、并行處理能力強(qiáng)的特點(diǎn),提高了系統(tǒng)的實(shí)時(shí)性;采用System

2021-04-29 06:14:20

我國目前的海事雷達(dá)大多為進(jìn)口雷達(dá),有效探測距離小,在信噪比降為3 dB時(shí)已經(jīng)無法識別信號。隨著微電子技術(shù)的迅猛發(fā)展,高速A/D(模擬/數(shù)字轉(zhuǎn)換)和高速數(shù)字信號處理器件(Digital Signal

2019-08-05 07:30:20

由于雷達(dá)所處的環(huán)境的復(fù)雜性,除了地物、云雨、鳥群等干擾外,還可能來自臨近的雷達(dá)異步干擾、電臺(tái)干擾等。所有的干擾,經(jīng)過接收機(jī)進(jìn)入信號處理機(jī),雖然經(jīng)過了中頻信號的處理,但還可能有殘余。因此,為了得到更好

2019-08-12 06:00:57

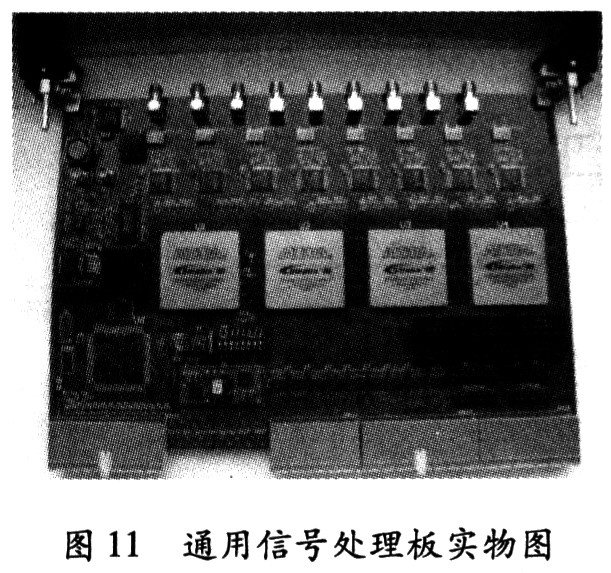

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ設(shè)計(jì)了基于CPCI總線的通用FPGA信號處理板,并在某雷達(dá)系統(tǒng)中進(jìn)行了實(shí)際應(yīng)用。

2021-05-07 06:54:25

雷達(dá)系統(tǒng)在研制過程中,各部分往往是并行的,在調(diào)試信號處理分系統(tǒng)時(shí),如果天線沒做好,就得不到陣面送下來的回波數(shù)據(jù),這時(shí)調(diào)試就無法正常進(jìn)行。為了解決這一問題,往往先設(shè)計(jì)一個(gè)模目信號,把信號處理分系統(tǒng)調(diào)試好,待其他分系統(tǒng)也調(diào)試好后,再切換為正常接收模式,進(jìn)行系統(tǒng)聯(lián)試。

2019-08-26 06:09:44

現(xiàn)代電子戰(zhàn)環(huán)境日趨復(fù)雜,信號日趨密集,新體制雷達(dá)不斷出現(xiàn),雷達(dá)信號的各個(gè)參數(shù)以各種規(guī)律變化,因而從密集復(fù)雜的信號環(huán)境中分選和識別各種新體制雷達(dá)信號就成了電子戰(zhàn)信號處理的一大難題。為了滿足電子支援措施

2019-08-21 07:46:56

微功率沖擊雷達(dá)是國際上近年來發(fā)展起來的一種新型高技術(shù)雷達(dá),作為超寬帶雷達(dá)類型的一種,沖激雷達(dá)直接發(fā)射無載波的基帶極窄脈沖,與傳統(tǒng)雷達(dá)不同的是沖激雷達(dá)系統(tǒng)既不需要對發(fā)射信號進(jìn)行載波調(diào)制,也不需要對接收信號

2019-08-20 06:43:40

數(shù)字式雷達(dá)信號處理器系統(tǒng)組成及工作原理是什么?數(shù)字式雷達(dá)信號處理器的基本工作流程有哪些?

2021-04-21 06:36:22

您好,最近在設(shè)計(jì)一款雷達(dá),發(fā)射板、接收板、和信號處理板,發(fā)射板使用的是FPGA控制+PLL產(chǎn)生發(fā)射波形和本振,想知道這個(gè)FPGA的時(shí)鐘、PLL的時(shí)鐘,信號處理板的時(shí)鐘,是使用一個(gè)晶振的來分配時(shí)鐘呢

2019-01-02 15:36:07

一般的雷達(dá)信號源實(shí)現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結(jié)合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結(jié)合的方式:第三種是由FPGA等可編程器件實(shí)現(xiàn)DDS的方式

2020-11-24 06:39:52

隨著數(shù)字化技術(shù)和系統(tǒng)軟、硬件技術(shù)的不斷提高,“軟件化雷達(dá)”成為雷達(dá)信號處理領(lǐng)域的最新研究方向。通用并行信號處理平臺(tái)是“軟件化雷達(dá)”的重要組成部分。本文討論了

2009-05-25 14:11:51 28

28 設(shè)計(jì)了一種基于DSP 和FPGA 的雷達(dá)信號分選電路,對密集的雷達(dá)信號進(jìn)行分選識別。系統(tǒng)利用FPGA 采集信號的特征參數(shù)以及對參數(shù)進(jìn)行預(yù)處理;采用了累積差值直方圖算法,根據(jù)信號脈

2009-07-16 10:52:25 26

26 本文介紹了一個(gè)基于高速定點(diǎn)DSP的雷達(dá)信號處理實(shí)驗(yàn)系統(tǒng)的設(shè)計(jì)和研制,其中包括雷達(dá)中頻信號采集,多種雷達(dá)信號的設(shè)計(jì)和產(chǎn)生,雷達(dá)回波的

2009-09-04 08:37:07 15

15 本文針對磁通門信號采集與處理的具體特點(diǎn),對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)

2009-12-23 15:09:09 15

15 本文研究了一種相控陣脈沖多普勒雷達(dá)信號處理板的設(shè)計(jì)及實(shí)現(xiàn)。設(shè)計(jì)基于ADSP21161N組成多處理器系統(tǒng),具有針對相控陣的多通道處理能力,可實(shí)時(shí)實(shí)現(xiàn)脈沖多普勒雷達(dá)信號處理中視

2010-01-12 21:39:44 48

48 本文針對磁通門信號采集與處理的具體特點(diǎn),對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)處理,再

2010-07-21 17:24:58 26

26 基于FPGA的各種雷達(dá)信號產(chǎn)生方法,介紹了在FPGA中實(shí)現(xiàn)直接數(shù)字頻率合成器(DDS)以及提高輸出信號質(zhì)量的方法,編程實(shí)現(xiàn)了頻率捷變、線性調(diào)頻以及相位編碼等雷達(dá)信號的產(chǎn)生。仿真

2010-11-29 18:02:49 31

31 摘 要: 本文在闡述某種近距雷達(dá)目標(biāo)檢測原理和FPGA技術(shù)發(fā)展?fàn)顩r的基礎(chǔ)上,著重討論用FPGA設(shè)計(jì)高性能的數(shù)字信號處理系統(tǒng)的方法,并給出一個(gè)應(yīng)用實(shí)例。

2006-03-11 13:16:43 1698

1698

超高速雷達(dá)數(shù)字信號處理技術(shù)

綜述了超高速雷達(dá)數(shù)字信號處理技術(shù)的應(yīng)用背景、研究內(nèi)容、關(guān)鍵技術(shù)及解決方法.采用超高速數(shù)字信號處理技術(shù)實(shí)現(xiàn)

2009-10-21 15:43:36 1651

1651

基于DSP和FPGA技術(shù)的低信噪比雷達(dá)信號檢測

我國目前的海事雷達(dá)大多為進(jìn)口雷達(dá),有效探測距離小,在信噪比降為3 dB時(shí)已經(jīng)無法識別信號。隨著微電子技術(shù)的迅猛發(fā)展,高速

2009-11-05 10:33:24 496

496

基于CPCI總線的通用FPGA信號處理板的設(shè)計(jì)

?隨著雷達(dá)信號處理技術(shù)的不斷發(fā)展以及現(xiàn)代國防對雷達(dá)技術(shù)的需求,系統(tǒng)對雷達(dá)信號處理的要求也越來越高,需要實(shí)時(shí)處

2009-11-28 15:07:38 922

922

基于FPGA嵌入式系統(tǒng)的雷達(dá)信號模擬器

在現(xiàn)代雷達(dá)系統(tǒng)的研制和調(diào)試過程中,對雷達(dá)性能和指標(biāo)的測試是一個(gè)重要環(huán)節(jié),在這個(gè)環(huán)節(jié)中,利用模擬目標(biāo)信號的方式與外場

2010-02-06 09:25:45 772

772

WRZSP2(Weather Radar Zauto Signal Processor2)是潮流公司在原WRZSP1常規(guī)天氣雷達(dá)信號處理器基礎(chǔ)上開發(fā)的第二代高性能低成本常規(guī)天氣雷達(dá)信號處理器,主要面向低端的常規(guī)天氣雷達(dá)系統(tǒng)市

2011-02-25 11:36:52 35

35 應(yīng)用領(lǐng)域: 6U VME TigerSHARC201FPGA信號處理機(jī)主要面向雷達(dá)、聲納、通信、圖象處理等高速信號處理領(lǐng)域。采用專用DSP與FPGA可編程邏輯器組成陣列化并行處理機(jī),已經(jīng)越來越成為當(dāng)前數(shù)字信號處理發(fā)展的趨勢。 雷航科技的6U VME TigerSHARC201FPGA信號處理機(jī)就

2011-02-28 12:05:32 64

64 本文介紹了一種模目信號設(shè)計(jì)方法,利用FPGA產(chǎn)生時(shí)序及控制,DSP實(shí)時(shí)計(jì)算所需要的回波,從而實(shí)現(xiàn)對雷達(dá)目標(biāo)回波的模擬,這樣可以在沒有陣面數(shù)據(jù)的情況下,使信號處理分系統(tǒng)調(diào)試能

2011-07-05 09:46:27 1111

1111

目前雷達(dá)信號采集通常由專用設(shè)備完成,其分析可利用設(shè)計(jì)師自己編制的軟件進(jìn)行。但存在通用性差,費(fèi)用高等問題。所以本文通提出了數(shù)字存儲(chǔ)示波器進(jìn)行 雷達(dá) 信號采集。

2011-07-07 17:02:14 167

167 為了解決 雷達(dá)信號處理 中的高速運(yùn)算, 大容量存儲(chǔ)和高速數(shù)據(jù)傳輸?shù)膯栴}, 提出采用 TS201 芯片實(shí)現(xiàn)雷達(dá)信號處理機(jī)設(shè)計(jì), 利用其超高性能的處理能力和易于構(gòu)造多處理并行系統(tǒng)的特

2011-07-20 17:20:13 65

65 在雷達(dá)系統(tǒng)的 數(shù)字信號處理 中,其主要特點(diǎn)是數(shù)據(jù)流量大、運(yùn)算量大和處理的實(shí)時(shí)性,單片高性能的DSP芯片也不能滿足處理要求,必須采用多DSP板作為數(shù)字信號處理平臺(tái)。 開發(fā)復(fù)雜的

2011-08-26 14:38:39 42

42 本文提出基于FPGA的數(shù)字收發(fā)機(jī)信號處理研究與實(shí)現(xiàn)

2011-11-01 18:20:42 50

50 本設(shè)計(jì)的信號處理機(jī)是希望以他為主體構(gòu)成一個(gè)完整的便攜式雷達(dá)系統(tǒng),除了信號處理的任務(wù)之外,采樣、顯示、通信等多種任務(wù)也必須由他來完成。

2012-01-10 14:17:12 2204

2204 本文提出了一種基于FPGA的雷達(dá)數(shù)字信號處理機(jī)設(shè)計(jì),接收機(jī)采用了脈沖多普勒、數(shù)字波束形成等主流雷達(dá)技術(shù)。

2012-03-31 09:53:13 2559

2559

為滿足雷達(dá)數(shù)據(jù)處理系統(tǒng)目標(biāo)跟蹤算法的測試需求,介紹了一種基于USB和FPGA技術(shù)的雷達(dá)目標(biāo)信號模擬器設(shè)計(jì)方案。文中重點(diǎn)討論了模擬器的結(jié)構(gòu)和目標(biāo)數(shù)據(jù)形成、傳輸、存儲(chǔ)、信號波形

2013-09-02 14:41:00 76

76 基于FPGA的雷達(dá)信號處理系統(tǒng)設(shè)計(jì)的論文

2015-10-30 10:38:12 6

6 基于FPGA數(shù)字信號處理,本文主要探討了基于FPGA數(shù)字信號處理的實(shí)現(xiàn)

2015-10-30 10:39:38 30

30 本書比較全面地闡述了fpga在數(shù)字信號處理中的應(yīng)用問題。本書共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設(shè)計(jì)中常用軟件簡介、用fpga實(shí)現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 介紹雷達(dá)信號處理的基本知識的課件

有需要的朋友下來看看

2015-12-24 10:45:46 0

0 本書譯自國際著名雷達(dá)信號處理專家Mark A. Richards教授編寫的教科書。該書介紹了雷達(dá)系統(tǒng)與信號處理的基本理論和方法,主要內(nèi)容包括:雷達(dá)系統(tǒng)導(dǎo)論、雷達(dá)信號模型、脈沖雷達(dá)信號的采樣和量化

2016-04-05 14:20:35 25

25 本書譯自國際著名雷達(dá)信號處理專家Mark A. Richards教授編寫的教科書。該書介紹了雷達(dá)系統(tǒng)與信號處理的基本理論和方法,主要內(nèi)容包括:雷達(dá)系統(tǒng)導(dǎo)論、雷達(dá)信號模型、脈沖雷達(dá)信號的采樣和量化

2016-04-05 14:23:26 18

18 本書譯自國際著名雷達(dá)信號處理專家Mark A. Richards教授編寫的教科書。該書介紹了雷達(dá)系統(tǒng)與信號處理的基本理論和方法,主要內(nèi)容包括:雷達(dá)系統(tǒng)導(dǎo)論、雷達(dá)信號模型、脈沖雷達(dá)信號的采樣和量化

2016-04-05 14:30:38 25

25 第一章雷達(dá)信號分析與處理,有需要的下來看看

2016-08-05 17:32:53 0

0 基于FPGA的某型雷達(dá)視頻采集預(yù)處理模塊設(shè)計(jì)

2016-08-30 15:10:14 34

34 雷達(dá)信號處理的小程序

2016-12-15 22:43:16 65

65 基于FPGA數(shù)字信號處理

2016-12-14 22:08:25 20

20 數(shù)字信號處理的FPGA實(shí)現(xiàn)

2016-12-14 22:08:25 32

32 基于DSP_FPGA的LFMCW雷達(dá)測距信號處理系統(tǒng)設(shè)計(jì)_陳林軍

2017-03-19 19:07:17 4

4 隨著AESA體系結(jié)構(gòu)的擴(kuò)展,它們將突破雷達(dá)信號處理專業(yè)應(yīng)用,延伸到其他應(yīng)用中。在外部應(yīng)用中,這些設(shè)計(jì)會(huì)遇到典型的嵌入式設(shè)計(jì)流程:以CPU和軟件為中心的,基于C的以及與硬件無關(guān)的。本文中,我們

2017-09-15 14:33:48 2

2 基于Cortex_A8和FPGA的嵌入系統(tǒng)在雷達(dá)信號處理中的應(yīng)用

2017-10-26 08:27:50 3

3 針對信號處理數(shù)據(jù)量大、實(shí)時(shí)性要求高的特點(diǎn),從實(shí)際應(yīng)用出發(fā),設(shè)計(jì)了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務(wù)需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2373

2373

介紹了直接數(shù)字頻率合成(DDS)的基本原理,并基于Xilinx公司的FPGA設(shè)計(jì)出產(chǎn)生連續(xù)波、重頻參差抖動(dòng)、頻率捷變、線性調(diào)頻以及二相編碼等雷達(dá)信號的系統(tǒng)方案。實(shí)驗(yàn)結(jié)果表明,該設(shè)計(jì)靈活且性能良好

2017-11-18 12:50:12 6172

6172 提出了一種基于FPGA的雷達(dá)回波實(shí)時(shí)模擬器的實(shí)現(xiàn)方法。該模擬器采用cPCI 標(biāo)準(zhǔn)總線,以FPGA 為核心計(jì)算單元,配有高速數(shù)模、模數(shù)轉(zhuǎn)換模塊,可實(shí)現(xiàn)雷達(dá)回波信號實(shí)時(shí)在線注入模擬。該模擬器可實(shí)現(xiàn)多種

2017-11-18 13:00:01 2444

2444

近年來,雷達(dá)在軍用和民用領(lǐng)域都獲得了巨大的發(fā)展。雷達(dá)信號處理系統(tǒng)是雷達(dá)的關(guān)鍵模塊,對雷達(dá)定位精度起著決定性作用。FPGA 以其眾多的優(yōu)點(diǎn),在雷達(dá)信號處理系統(tǒng)中被廣泛使用。本文探究FPGA 在雷達(dá)信號

2017-11-22 07:25:02 4251

4251

信號。要提高毫米波雷達(dá)的作用距離,中頻信號的頻率就必須提高,對雷達(dá)信號采樣及處理提出了更高的要求。信號處理的點(diǎn)數(shù)和運(yùn)算速度已經(jīng)成為了制約毫米波雷達(dá)信號發(fā)展的主要因素。高精度、大帶寬和實(shí)時(shí)性必將成為雷達(dá)信號處理系統(tǒng)發(fā)展的主流。 目前采用的方

2018-01-18 17:01:51 12

12 FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動(dòng) 基于FPGA灰度圖像高斯濾波算法的實(shí)現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:49:00 1479

1479 FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 2449

2449

現(xiàn)代雷達(dá)特別是機(jī)載雷達(dá)數(shù)字信號處理機(jī)的特點(diǎn)是輸入數(shù)據(jù)多,工作模式復(fù)雜,信息處理量大。因此,在一個(gè)實(shí)時(shí)信號處理系統(tǒng)中,雷達(dá)信號處理系統(tǒng)要同時(shí)進(jìn)行高速數(shù)據(jù)分配、處理和大量的數(shù)據(jù)交換

2018-10-14 08:27:00 2262

2262

芯片進(jìn)行基因體定序與優(yōu)化語音辨識所需的深度學(xué)習(xí),察覺FPGA 的耗能低于GPU 且處理速度較快。相較于GPU 只能處理運(yùn)算,FPGA 能以更快速的速度一次處理所有與AI 相關(guān)資訊。

2019-01-18 14:14:42 499

499 FPGA相對于CPU和GPU,在進(jìn)行感知處理等簡單重復(fù)的任務(wù)的時(shí)候的優(yōu)勢很明顯,按照現(xiàn)在的趨勢發(fā)展下去,FPGA或許會(huì)在未來取代機(jī)器人開發(fā)中GPU的工作。

2019-09-06 17:48:10 2115

2115 針對某型高炮射擊檢查分析系統(tǒng),介紹了一種適用于某型雷達(dá)的視頻采集預(yù)處理模塊,其主要功能是利用雷達(dá)攝像頭識別彈跡并標(biāo)記其坐標(biāo)。該模塊選用視頻解碼芯片和FPGA對視頻信號進(jìn)行控制讀取,通過對動(dòng)目標(biāo)的檢測

2021-02-01 16:11:00 12

12 多速率技術(shù)已廣泛應(yīng)用于數(shù)字音頻處理、語音處理、頻譜分析、無線通信、雷達(dá)等領(lǐng)域。作為一項(xiàng)常用信號處理技術(shù),FPGA攻城獅有必要了解如何應(yīng)用該技術(shù),解決實(shí)際系統(tǒng)中的多速率信號處理問題。 01什么是多速率

2021-06-01 11:02:19 2799

2799

數(shù)字信號處理的FPGA實(shí)現(xiàn).第3版英文

2021-10-18 10:55:32 0

0 說到異步時(shí)鐘域的信號處理,想必是一個(gè)FPGA設(shè)計(jì)中很關(guān)鍵的技術(shù),也是令很多工程師對FPGA望 而卻步的原因。但是異步信號的處理真的有那么神秘嗎?那么就讓特權(quán)同學(xué)和你一起慢慢解開這些所謂的難點(diǎn)

2021-11-01 16:24:39 11

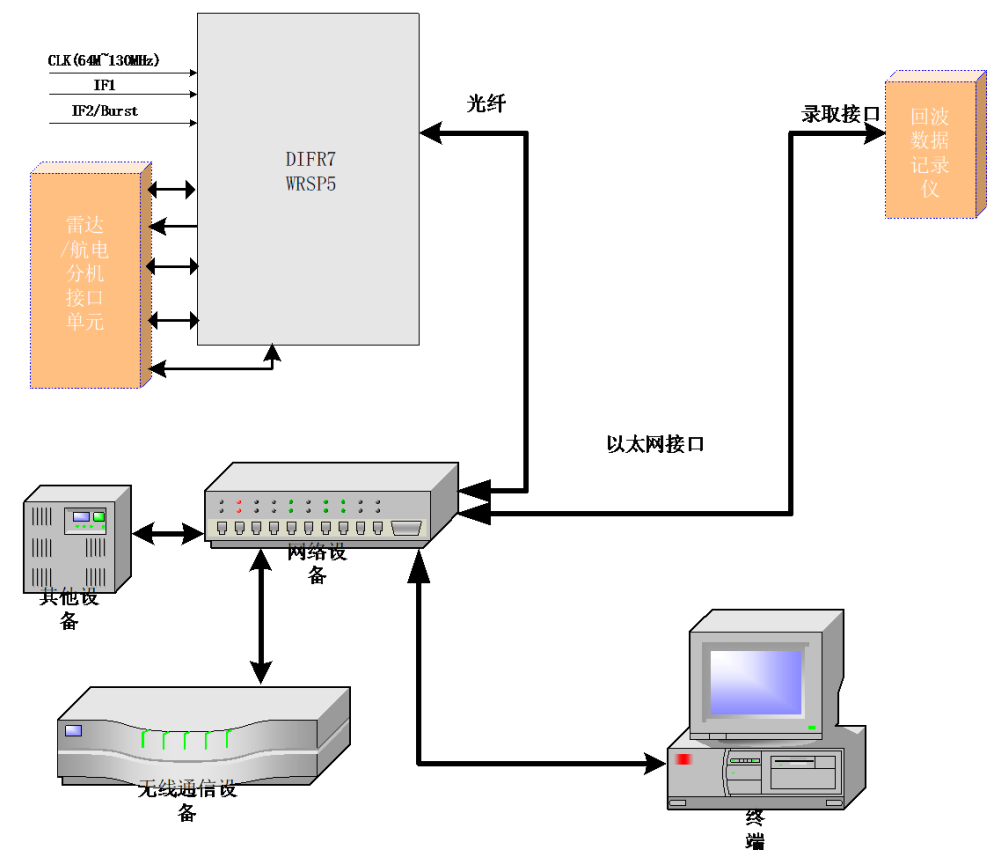

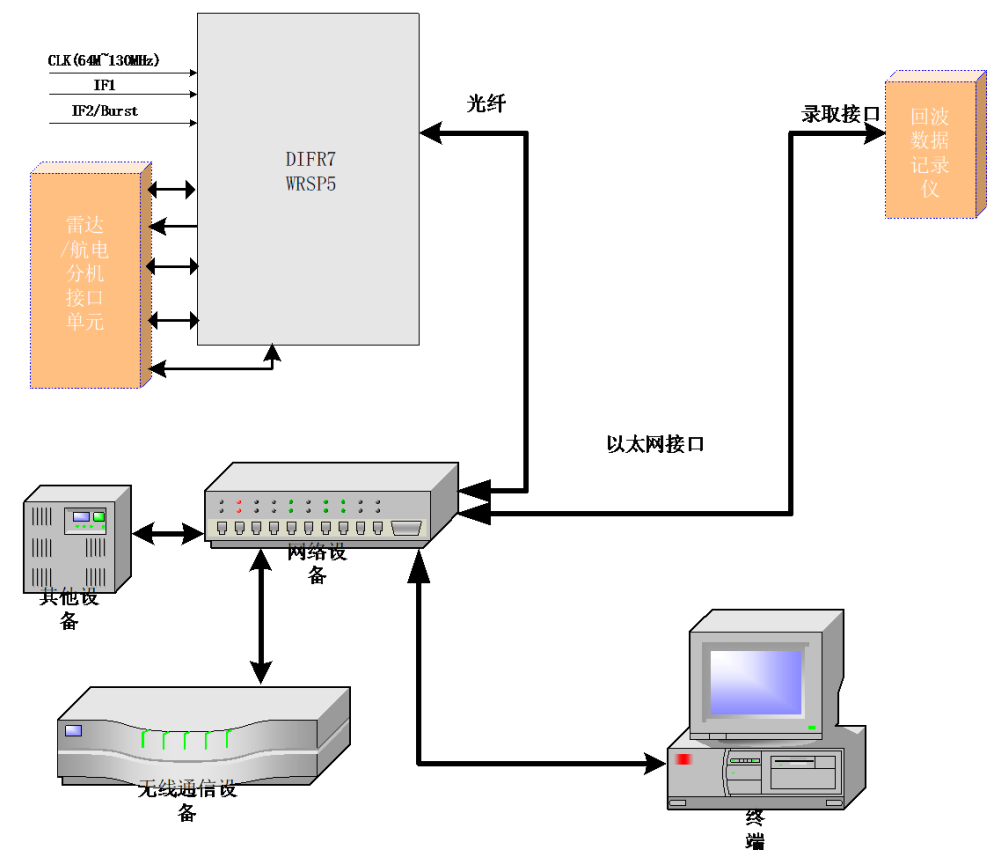

11 毫米波雷達(dá)信號處理系統(tǒng)(WRSP)是杭州淞柏科技公司研制的全功能高端雷達(dá)信號處理器,該處理器采用了脫機(jī)運(yùn)行、網(wǎng)絡(luò)接口,采用 DIFR硬件平臺(tái),為機(jī)載、艦載船載、車載等各種平臺(tái)雷達(dá)。在設(shè)計(jì)上采用高集成方案,高速DSP+FPGA 完成雷達(dá)信號處理模式,可支持各種不同方式的脈沖壓縮和補(bǔ)盲。

2021-11-24 15:26:28 969

969

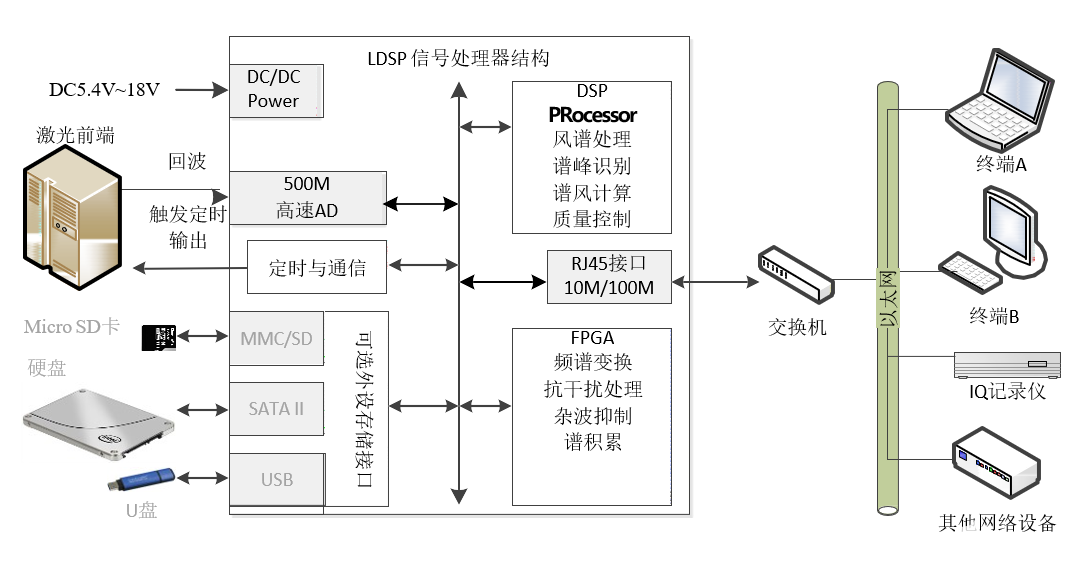

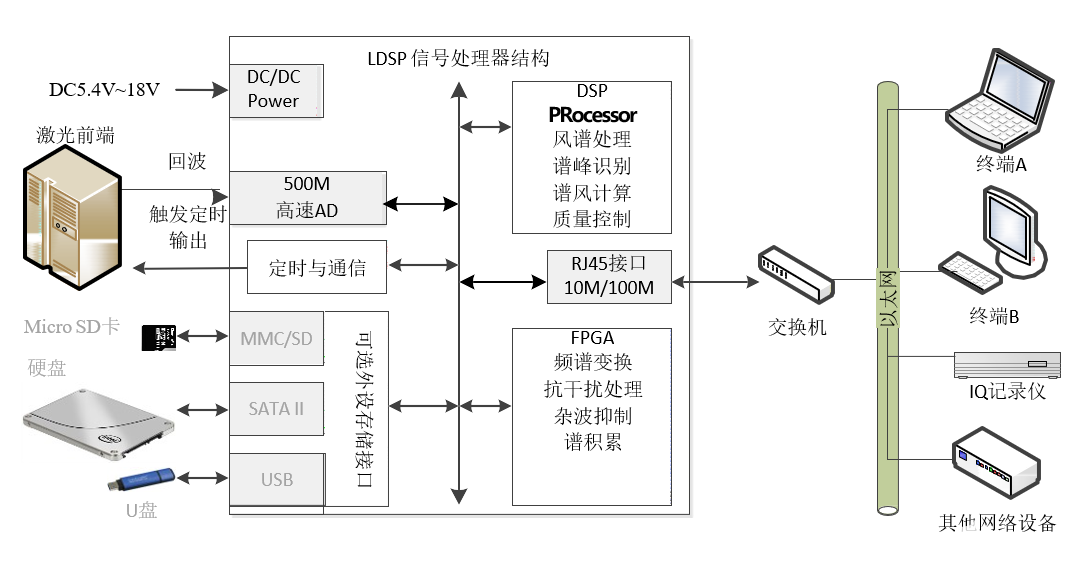

激光雷達(dá)信號處理系統(tǒng)(LDSP )是專為激光雷達(dá)研發(fā)的高性能、高集成、低功耗數(shù)字信號處理器。該信號處理器采用高速高精度 ADC、大規(guī)模 FPGA及高速 DSP等處理芯片,處理功能強(qiáng)大、速度高、功耗

2021-11-24 15:24:20 2142

2142

雷達(dá)信號處理基礎(chǔ)英文原版

2022-03-07 16:17:49 0

0 FPGA和CPU一直是雷達(dá)信號處理不可分割的組成部分。傳統(tǒng)上FPGA用于前端處理,CPU用于后端處理。隨著雷達(dá)系統(tǒng)的處理能力越來越強(qiáng),越來越復(fù)雜,對信息處理的需求也急劇增長。為此,FPGA不斷在提高處理

2022-12-14 11:46:09 1268

1268 對于信號處理來說,雷達(dá)和通信一直是一體兩面,從MIMO通信到MIMO雷達(dá),從OFDM通信到Multicarrier雷達(dá),很多通信和雷達(dá)領(lǐng)域的前沿技術(shù)都存在事實(shí)上的相互影響。本篇文章將會(huì)介紹劉凡博士

2023-04-19 17:43:42 1605

1605

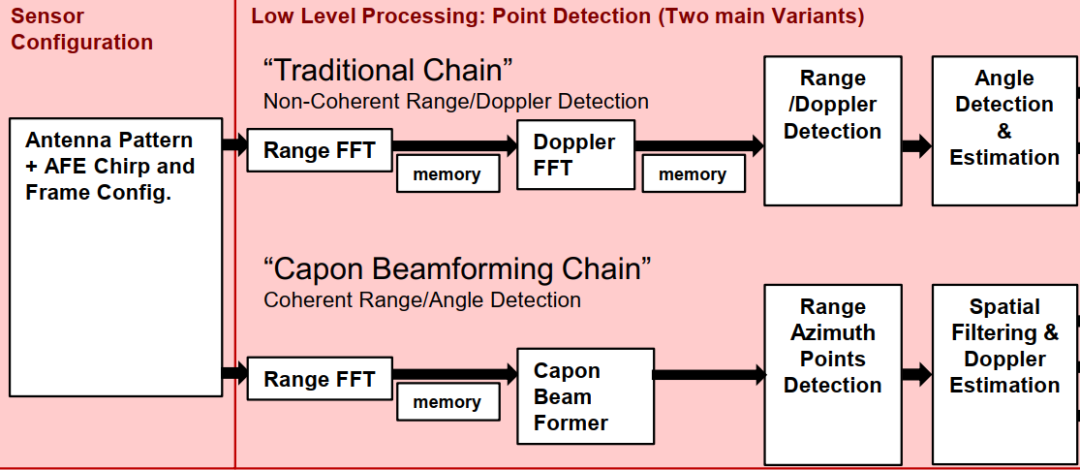

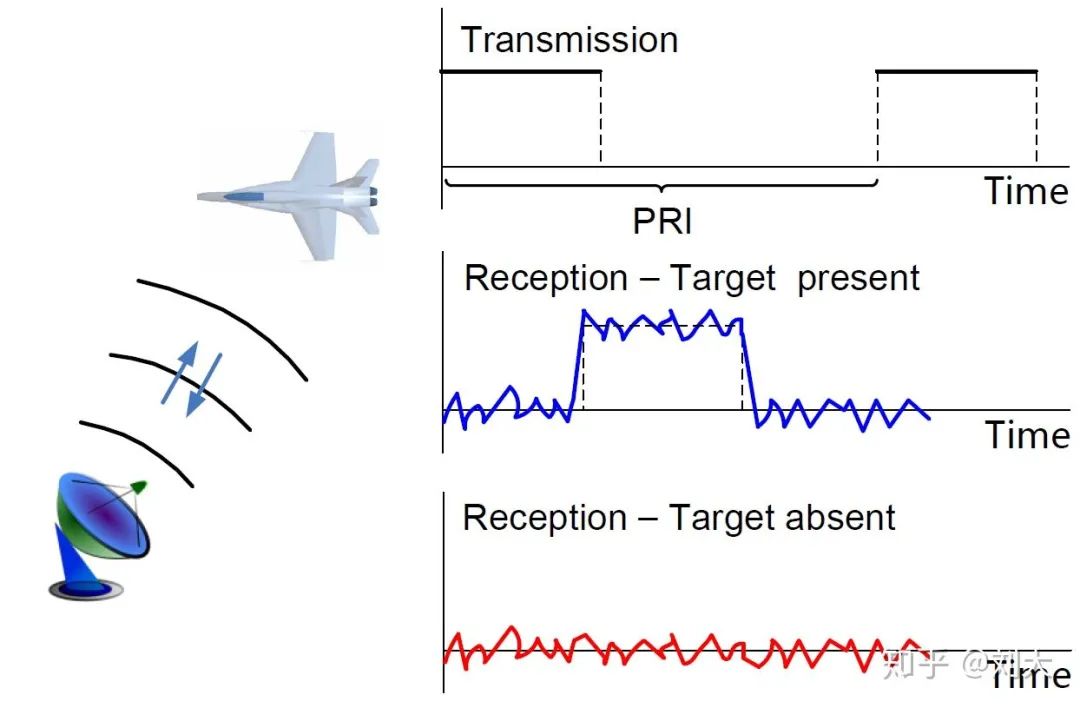

本文利用雷達(dá)作為傳感器,給出了當(dāng)前和未來的一些重要的汽車應(yīng)用。在汽車應(yīng)用中,需要處理的信號可以通過超聲傳感器

(Sonar)、雷達(dá)傳感器(radar)、相機(jī)(CV)、激光雷達(dá)(Lidar)、GPS

2023-06-07 14:28:20 1

1 雷達(dá)信號處理框架是整個(gè)信號處理的骨架,只有建立了合適的處理框架,往里添加子模塊反而是相對容易的事情。

2023-06-20 15:04:09 730

730

今天給大家介紹下Weibel公司的RTP-2100-MBPA雷達(dá)系統(tǒng),該系統(tǒng)采用基于GPU的處理技術(shù),可以輕松擴(kuò)展處理能力,支持多達(dá)8個(gè)GPU并行工作。

2023-08-04 09:33:05 604

604

"本課件主要展示了一些基本的雷達(dá)信號處理內(nèi)容!

2023-10-08 10:21:23 254

254

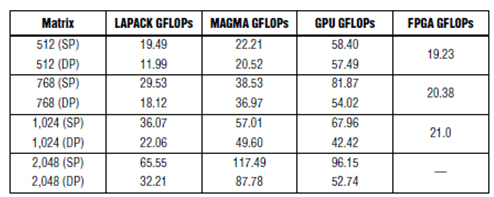

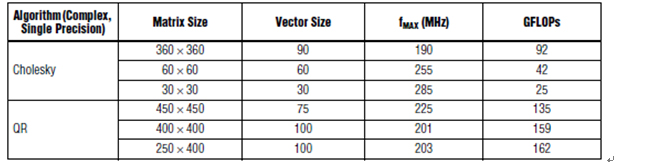

雷達(dá)信號處理算法對計(jì)算機(jī)架構(gòu)提出了很高的實(shí)時(shí)性要求。好在這些算法具有數(shù)據(jù)并行性,可以在大規(guī)模并行架構(gòu)(如圖形處理單元(GPU))上獲得出色的性能。

2023-10-17 10:07:37 459

459

電子發(fā)燒友網(wǎng)站提供《使用SoC FPGA,實(shí)現(xiàn)汽車雷達(dá)的數(shù)字化處理.pdf》資料免費(fèi)下載

2023-11-10 10:52:45 0

0 FPGA(現(xiàn)場可編程門陣列)和GPU(圖形處理器)是兩種常見的硬件加速器,用于提高計(jì)算和處理速度。盡管它們在很多方面都有重疊,但在架構(gòu)、設(shè)計(jì)和應(yīng)用上存在許多區(qū)別。在本文中,我們將詳細(xì)探討FPGA

2023-12-25 15:28:00 715

715

電子發(fā)燒友App

電子發(fā)燒友App

評論