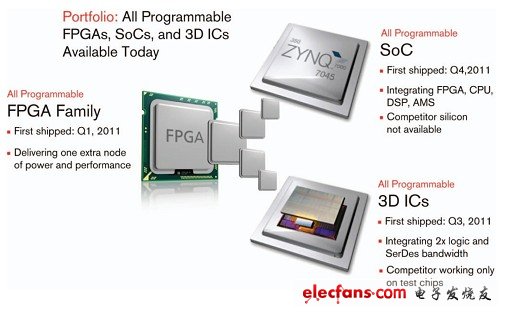

今天推出的 All Programmable 產品采用了各種形式的可編程技術,包括可編程硬件和軟件、數字信號和模擬混合信號(AMS)、單晶片和多片 3D IC 方案(圖 1)。有了這些全新的 All Programmable 器件,設計團隊就能進一步提升可編程系統的集成度,提高整體系統性能,降低 BOM 成本,并以更快的速度向市場推出更具創新性的智能產品。

圖 1:賽靈思超越邏輯范疇在 28nm 節點上對“可編程性”進行擴展,推出了一系列 All Programmable 器件

2008 年,賽靈思在新任 CEO Moshe Gavrielov 的領導下開始對產品系列實施轉型。賽靈思啟動了一套全面戰略,用以擴展技術組合,擴大市場范圍,并引入了最先進的 28nm 節點技術。其中,賽靈思實驗室和產品設計團隊經過多年原型設計和評估而開發出的兩種全新器件也即將投入量產。公司還同臺積電合作推出了全新的 28nm 芯片工藝。這種被稱為 HPL(含義是高性能、低功耗)的新工藝實際是為 FPGA 量身打造,具有最佳的高性能和低功耗特性。賽靈思認識到功耗是客戶的首要關注點,因此整個 All Programmable 產品線都采用這種先進的工藝制造。賽靈思還組建了一只頂級的 EDA 設計團隊來開發全新的現代化設計套件,其目標不僅是為了提高客戶在使用 5 個 28nm 器件系列時的工作效率,還有一個目的是為了滿足今后 10年內 All Programmable 器件的可擴展性要求。

Zynq-7000 All Programmable SoC#e#

ZYNQ-7000 ALL PROGRAMMABLE SOC

Zynq-7000 All Programmable SoC(片上系統)是首批推出的新型產品,它獲得了《EE Times》雜志評選的年度創新大獎,是一款改變業界格局的重要產品。All Programmable SoC 整合了 3 種適用于大規模定制化的可編程功能,分別是硬件、軟件和 I/O 可編程性。賽靈思已經推出了數代采用片上軟核與硬核處理器的 FPGA 產品,在此基礎之上并結合多年來廣泛收集的客戶反饋,最終形成了 Zynq-7000 All Programmable SoC 產品理念。

從上世紀 90 年代末開始,賽靈思和競爭對手都推出了軟處理器內核,客戶可將這種內核綜合到 FPGA 邏輯結構中。這樣,設計團隊就能在統一的架構中將處理與邏輯功能緊密整合,從而進一步降低 BOM 成本。在實踐中,許多軟處理器都被用于嵌入式狀態機,而不是運行在更為復雜的操作系統和軟件堆棧系統中。2005 年左右,新的半導體工藝使得 FPGA 廠商能夠推出更高容量的器件,于是廠商開始將硬處理器內核與 FPGA 邏輯配合使用,從而顯著改善了 FPGA 的處理性能。例如,賽靈思先后推出的 Virtex?-4 FX 和 Virtex-5 FX 系列都在 FPGA 邏輯中嵌入了 PowerPC? CPU 內核。

Virtex FX 系列相對于軟實現方案大幅提高了處理器性能,設計團隊要先對 FPGA 邏輯進行編程才能對處理器編程。一旦 FPGA 邏輯進行了編程,設計團隊就需要創建自己的外設、存儲器子系統并最終創建“嵌入式系統”和相關的進出邏輯的管道。熟悉 FPGA 設計的專家設計團隊當然希望實現處理器性能的提升,不過這種架構相對于更受歡迎的傳統嵌入式系統設計方法而言更復雜。在此經驗基礎上,賽靈思于 2008 年開始進行 Zynq-7000 All Programmable

SoC 的架構設計,同樣重要的是,公司還開始設計相關的生態系統,包括固件和軟件開發工具以及基礎設施,從而協助器件的編程工作。

對 Zynq-7000 All Programmable SoC 而言, 賽靈思選擇了非常受歡迎而且得到很好支持的 1-GHz ARM? A9 雙核處理器系統,并協同 ARM 創建 AXI4 接口標準,在架構的邏輯部分實現第三方、賽靈思和客戶開發的內核的即插即用。此外,賽靈思還對 Zynq 系列進行架構設計,使其能夠從處理器直接啟動,這樣系統設計人員就能以熟悉的方式開展工作,幫助設計團隊盡快啟動軟件開發工作,從而加快產品上市進程。由于處理器首先啟動,所以軟件設計人員即便不熟悉 FPGA 邏輯或硬件設計也能開始使用器件,或許還能擴展編程范圍。賽靈思還為 Zynq-7000 提供了豐富的外設IP核以及可編程的高速I/O,不僅能為客戶帶來 FPGA 和處理器,而且能實現真正的 All Programmable SoC。

賽靈思于 2010 年推出該架構,有力推動了客戶和生態系統合作伙伴的產品開發工作。公司于2011 年冬天向客戶推出首款 All Programmable SoC。某家公司作為最早獲得該產品的客戶之一一年多以來一直在用 Zynq 仿真平臺進行設計方案的定義和開發,收到芯片之后幾個小時之內就讓設計方案成功運行。今天,Zynq 的需求跟其它賽靈思 FPGA 系列一樣高,大多數應用都集成了不同 CPU、DSP、FPGA 和 AMS 組件中使用的系統功能。截至 2012 年 9 月,已有一家公司宣布了推出競爭性器件的計劃,但還沒有宣布交付芯片,而且也沒有成規模的生態系統為其提供足夠的支持。

ALL PROGRAMMABLE 3D ICs

賽靈思率先在 28 nm 工藝節點上推出的另一類全新器件就是所謂的“All Programmable 3D IC”。早在 2004 年,賽靈思實驗室就開始探索多芯片在統一 IP 配置中的堆棧,并最終推出了原型設計,以突破摩爾定律的限制,開創可編程系統集成的全新高度。賽靈思的科學家創建了各種 3D IC 架構的測試芯片,探索堆棧芯片的各種方法,并通過 TSV 給芯片供電,支持芯片間通信。通過廣泛的原型設計,并致力于可靠的制造,該公司判定近期商業上可行的最實用架構就是賽靈思的 SSI 技術。就此架構而言,多芯片在無源硅中介層頂部并行放置,有助于多芯片之間的互聯和通訊。芯片通過編程可支持超過 10000 個互聯,而且每個芯片和 I/O 都具有可編程性,這樣賽靈思所推出的就不光是首款商業 3D IC,而是首款 All Programmable 3D IC 了。

2012 年初,賽靈思為客戶推出首款 3D IC。Virtex-7 2000T 器件并行協議棧 4 個 FPGA 邏輯slice。該器件建立了一項 28nm 工藝節點上 IC 晶體管數量的新紀錄(超過 68 億個晶體管),也突破了 FPGA 邏輯容量的記錄,可提供 200 萬個邏輯單元(相當于 2 千萬個 ASIC 門)。該器件的尺寸相當于同類競爭器件最大型 FPGA 尺寸的兩倍,其邏輯容量比該工藝節點上通常預期的水平整整領先了一代。此外,該 SSI 技術架構還幫助賽靈思提供的容量超越了摩爾定律設想未來新一代的產品水平。

Virtex-7 2000T 器件深受客戶歡迎,并廣泛應用在包括 ASIC 原型設計、存儲和高性能計算系統在內的各種設計應用中。這些應用都需要業界能夠提供的最高容量的可編程邏輯。不過,賽靈思還進一步擴展了其 3D IC 技術,能夠充分滿足通信市場中最高性能的應用需求,整整領先同類競爭解決方案一代的水平。

2012 年夏季,賽靈思推出了面向通信市場的三款異構 All Programmable 3D IC中的首款產品:Virtex-7 H580T。Virtex-7 2000T 是一款同質 3D IC,其所有四個芯片/slice 都主要由 FPGA 邏輯構成,而 Virtex-7 H580T 則是首款異構 3D IC。

為了推出 Virtex-7 H580T,賽靈思在無源硅中介層上將專用的 28G 收發器芯片與兩個 FPGA 芯片并行放置。這樣一來,賽靈思推出的器件就能提供 8 個 28-Gbps 收發器、48 個 13.1-Gbps收發器和 580k 邏輯單元。對于基于 CFP2 光學模塊的 2x100G 光學傳輸線路卡等應用而言,Virtex-7 H580T 不僅可將材料清單成本銳減五分之一,還能相對于上一代實現方案而言顯著減少板級空間。

Virtex-7 H580T 只是賽靈思 28nm 系列中推出的首款異構 3D 器件。Virtex-7 H870T 器件在同一芯片上集成了 2 個八通道收發器芯片以及 3 個 FPGA 邏輯芯片,從而實現了在一個芯片上總共有 16 個 28-Gbps 收發器、72 個 13.1-Gbps 收發器和 876,160 個邏輯單元。Virtex-7 H870T 器件可全面支持新一代有線通信,也就是 400G 市場。此外,賽靈思的 3D IC 技術將幫助客戶在市場成型之初就能開始 400G 應用的開發工作,并獲得顯著的市場優勢,甚至有望比同類競爭對手整整領先一代技術。

All Programmable 3D IC 是 All Programmable 器件又一個遙遙領先于同類競爭解決方案的系列。雖然近期有一家公司宣布同臺積電代工廠合作生產了測試芯片,但該公司還沒有公開宣布面向客戶推出樣片或量產器件。

ALL PROGRAMMABLE FPGA

自賽靈思推出業界首款 FPGA(1985 年推出相當于 1000 個 ASIC 門的 XC2064)以來,FPGA 已經取得了長足的發展。最早的 FPGA 定位于門陣列和 ASIC 的替代品,主要用作“粘性邏輯”,協助兩個最初設計不相互通信的器件進行對話,此外也能在設計最后時刻為大型 ASIC 補充此前缺失的功能。

時光快進到當下,顯然,現代 FPGA 產品已經遠遠超越了門陣列的水平。今天的 All Programmable FPGA 不僅包含數百萬個可編程邏輯門,還嵌入了存儲器控制器、高速 I/O 以及模擬 / 混合信號電路系統。就過去的 FPGA 而言,設計團隊能用它解決系統中的問題,或者把系統元素“粘合”在一起。而就今天的 All Programmable FPGA 而言,能夠幫助客戶創建高性能數據包處理、波形處理、圖象 / 視頻處理或高性能計算功能,而且能在系統中進行動態重編程,也能在產品部署后進行升級。

賽靈思在 All Programmable SoC 和 3D IC 市場中還沒有遇到過競爭對手,要是能在傳統的FPGA 市場中領先競爭對手整整一代的水平當然也是一個巨大的成就。為了實現這個目標,賽靈思制定了一個明確的戰略,首先推出 28nm 的 FPGA 芯片,通過擴展組合涵蓋低端、中端乃至高端產品的各種不同要求。賽靈思還制定了區分所有 28nm 工藝芯片特色化的目標,一是在系統性能和集成度方面領先對手一代的水平,二是功耗降低再領先一代的水平,三是串行解串器大躍進實現最低抖動和無與倫比的通道均衡,四是新一代工具套件為未來的需求提供高效率、結果質量(QoR)和可擴展性優勢。

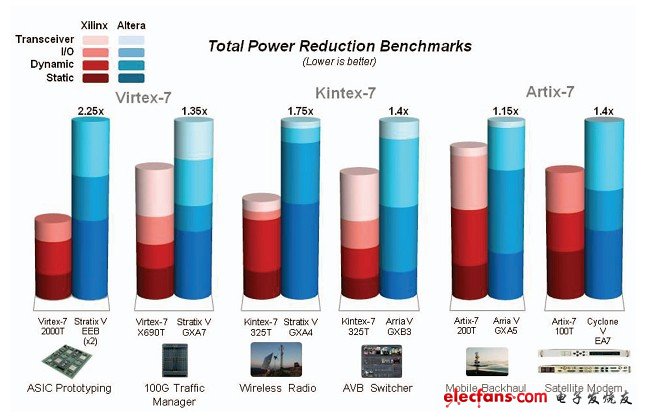

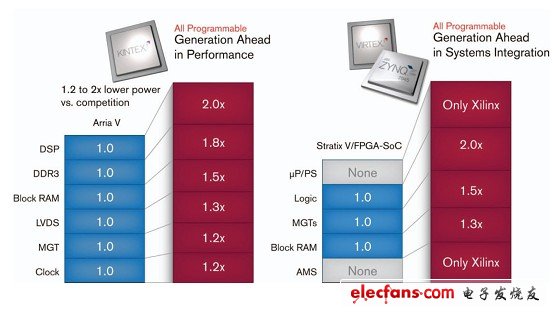

事實上,賽靈思已經實現了上述所有目標,于 2011 年 3 月推出了首款 28nm 系列產品Kintex ? -7 K325T(同時也是首款中端產品)。賽靈思實際上是整個半導體產業中首個推出 28nm 芯片的企業。賽靈思決定基于臺積電的 HPL 工藝實施全系列 28 nm All Programmable器件,而且為進一步降低功耗采用關鍵的架構創新,這使得公司目前為客戶提供的 All Programmable FPGA 產品對同類性能的競爭產品而言能將功耗降低 35% 到 50%,在用電效率上領先了整整一代的水平(圖 2)。賽靈思的 28nm FPGA 還實現了無與倫比的高性能和高集成度(圖 3)。系統性能和集成度(包括 BRAM、DSP、存儲器接口、收發器和邏輯元件的集成)都超越競爭對手 1.2 倍到 2 倍,平均優勢達 1.5 倍,也相當于領先整整一代的水平。

圖 2:客戶設計顯示相同性能水平下的功耗平均比競爭對手降低 35%

圖 3:賽靈思的 28nm FPGA 相對于競爭對手而言在性能和集成度方面領先了整整一代的水平。公司已經根據規范推出了 All Programmable 器件,FPGA 量產器件還沒有勘誤表。

此外,賽靈思的 All Programmable FPGA 還可提供競爭對手所沒有的特性。舉例來說,所有賽靈思的 28nm FPGA 都包含靈活混合信號模塊,通過支持在 FPGA 中實現的模擬系統功能(而不是采用外部分離式的模擬器件)進一步降低材料清單成本。

采用 VIVADO 提高工作效率

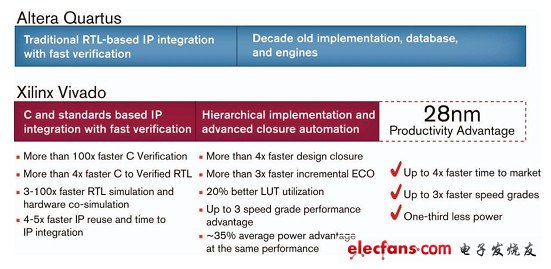

為了提高設計人員采用 28 nm 及其更高 All Programmable 器件的工作效率,賽靈思還全新開發了新一代設計環境和工具套件 Vivado ?(圖 4)。開發工作耗時 4 個日歷年以上,凝聚 500 人多年的努力。沒有這款設計套件,設計團隊就不能有效地發揮賽靈思 3D IC 的潛力。對 FPGA 和 SoC 而言,Vivado Design Suite 將設計質量結果提升了三個速度等級,將動態功耗降低了高達 50%,可路由性和資源利用率提升了 20% 以上,集成和實現速度翻了兩番之多。

圖 4:賽靈思的 Vivado 為設計人員帶來一流的設計套件,大幅提升工作效率,顯著加速產品上市進程。

Vivado 對支持新型 All Programmable 器件組合、實現可編程系統高度集成發揮著至關重要的作用。因此,我們關注的重點大大超越了加速實施流程和 QoR、利用尖端分析引擎和關閉自動化。為了實現出色的集成度,Vivado 支持分層架構、IP 核封裝和重用、自動化 IP 核拼接以及高速驗證。為了進一步加快產品上市進程,提高設計抽象化水平,Vivado 支持基于 C 設計和驗證的流程,能通過高層次綜合和自動化 AXI 接口生成來加速從 C 到 RTL IP 的創建和集成速度。這樣,Vivado 不僅加速了實現速度,也在設計前端加快了 C 到 RTL 的集成速度。

總結

賽靈思如今開發了各種形式的可編程技術,超越了可編程硬件而涵蓋軟件領域,超越了數字而涵蓋 AMS,超越單芯片而涵蓋多芯片 3D IC 實施方案。賽靈思將這些技術整合到 All Programmable FPGA、SoC 以及 3D IC 中,可幫助設計團隊提高可編程系統集成度,改進整體系統性能,降低材料清單成本,并加快向市場推出創新型產品的速度。賽靈思產品組合的變革轉型可追溯到 2008 年,部分創新技術則能進一步上溯到 2006 年,其成果則是如今的產品組合技術已整整領先競爭對手一代的水平,為客戶帶來增值。

放眼 20nm 工藝節點,賽靈思將推出更高級的 FPGA、第二代 SoC 以及 3D IC 產品,進一步擴大領先地位,同時還將推出 Vivado 設計系統,使賽靈思的技術水平始終領先一代之遙。賽靈思開始同客戶合作調節改進 SoC 和 3D IC 技術的舉措領先競爭對手多年,重新定義了高速串行收發器等關鍵核心技術的開發和交付,改進了設計方法和工具,擴展了系統級生態系統和供應鏈,并確保其質量和可靠性。

電子發燒友App

電子發燒友App

評論