通過(guò)上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過(guò)以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

嗨,我使用的是virtex 5 FPGA。我正在運(yùn)行外部10Mhz時(shí)鐘信號(hào)來(lái)運(yùn)行二進(jìn)制計(jì)數(shù)器。當(dāng)我嘗試使用DCM時(shí),它表示最低頻率為32MHz。可以將此信號(hào)運(yùn)行到FPGA的i / o輸入并通過(guò)全局

2019-02-21 10:32:51

28377D的I/O輸出響應(yīng)時(shí)間受系統(tǒng)時(shí)鐘影響嗎?最近在使用2M*16的FLASH,但是28377D 得EMIF地址只能夠訪問(wèn)到1M地址空間,此時(shí)用I/O做其高位地址線,現(xiàn)在想知道I/O響應(yīng)

2020-05-29 09:41:39

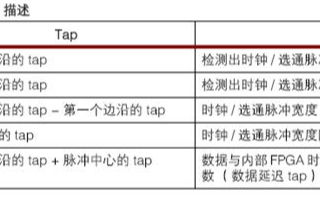

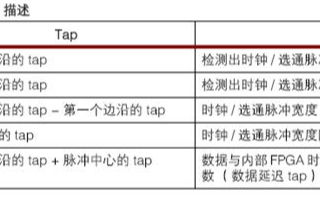

能夠?qū)@些數(shù)據(jù)進(jìn)行處理。以下兩個(gè)例子說(shuō)明了FPGA的I/O結(jié)構(gòu)的發(fā)展。源同步接口在源同步接口中,發(fā)送器芯片發(fā)送數(shù)據(jù)字和數(shù)據(jù)采樣時(shí)鐘至接收器。接收器芯片使用時(shí)鐘來(lái)采集數(shù)據(jù)。從理論上說(shuō),源同步接口的速度

2018-11-26 11:17:24

FPGA 時(shí)鐘分配網(wǎng)絡(luò)設(shè)計(jì)技術(shù)

2012-08-20 17:15:27

,這就按照連線最短的原則將對(duì)應(yīng)的信號(hào)分配到與外部器件連線最近的BANK 中,2 、 掌握FPGA 內(nèi)部BANK 的分配的情況。 現(xiàn)在FPGA 內(nèi)部都分成幾個(gè)區(qū)域,每個(gè)區(qū)域中可用的I/O 管腳數(shù)量各不相同

2012-08-11 10:27:54

說(shuō)說(shuō)專用時(shí)鐘引腳,它的出現(xiàn)具體原因可以說(shuō)是FPGA自身的實(shí)現(xiàn)結(jié)構(gòu)引起的,FPGA實(shí)現(xiàn)時(shí),具體的時(shí)鐘大概有外部供給FPGA的工作時(shí)鐘,由DCM或者PLL產(chǎn)生的時(shí)鐘,和FPGA輸入輸出數(shù)據(jù)的隨路時(shí)鐘;再說(shuō)

2019-07-09 08:00:00

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對(duì)接,此時(shí)IPO接口的時(shí)序問(wèn)題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問(wèn)題。

2012-08-12 11:57:59

`引腳分配規(guī)劃和擴(kuò)展I/O電路本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 核心板上專門留了一個(gè)LED

2015-05-06 11:31:16

電路設(shè)計(jì)的可選擇性豐富而言的。話說(shuō)回來(lái),這里的“自由”也還是要建立在一定的基礎(chǔ)之上的。筆者根據(jù)多年的工程經(jīng)驗(yàn),對(duì)于I/O與外設(shè)的連接擴(kuò)展,歸納出以下一些要點(diǎn):●輸入和輸出時(shí)鐘信號(hào)盡量分配到專用的引腳

2019-04-12 06:35:33

FPGA的I/O結(jié)構(gòu)的發(fā)展的怎么樣了?

2021-04-29 06:12:52

喜我對(duì)時(shí)鐘門控有一些疑問(wèn)。從我所讀到/學(xué)到的東西 - 時(shí)鐘門控可用于低功率fpga設(shè)計(jì)(關(guān)閉時(shí)鐘以防止元件切換以節(jié)省功率)。但是,我還讀到時(shí)鐘門控很糟糕,因?yàn)樗赡軙?huì)引起系統(tǒng)故障。我想我已經(jīng)看到了

2019-02-21 10:21:41

FPGA 內(nèi)部 BANK 的分配的情況。現(xiàn)在 FPGA 內(nèi)部都分成幾個(gè)區(qū)域,每個(gè)區(qū)域中可用的 I/O 管腳數(shù)量各不相同。在 IC 驗(yàn)證中都是采用了ALTERA 與XILINX系列的FPGA ,這兩個(gè)廠商

2024-01-10 22:40:14

的 BANK 中。 2、 掌握 FPGA 內(nèi)部 BANK 的分配的情況。現(xiàn)在 FPGA 內(nèi)部都分成幾個(gè)區(qū)域,每個(gè)區(qū)域中可用的 I/O 管腳數(shù)量各不相同。在 IC 驗(yàn)證中都是采用了ALTERA 與XILINX系列

2017-03-25 18:46:25

/O信號(hào)分配 可提供最多的多功能引腳、I/O標(biāo)準(zhǔn)、端接方案和差分對(duì)的FPGA在信號(hào)分配方面也具有最復(fù)雜的設(shè)計(jì)指導(dǎo)原則。盡管Altera的FPGA器件沒(méi)有設(shè)計(jì)指導(dǎo)原則(因?yàn)樗鼘?shí)現(xiàn)起來(lái)比較容易),但賽靈思

2020-09-07 11:01:46

:圖2:Spartan-7 FPGA同一bank連接1.8V SPI Flash和1.35V DDR3L雖然這不是一個(gè)標(biāo)準(zhǔn)的解決方案,只是限于有限的I/O資源,但是對(duì)于小型系統(tǒng)設(shè)計(jì)不失為一種好的方法。具體設(shè)計(jì)細(xì)節(jié)如器件選型、原理圖、確定時(shí)鐘頻率等要求請(qǐng)參看官方文檔`

2018-08-02 09:37:08

你好,我是新的virtex 4設(shè)計(jì)師。有人可以告訴I / O和時(shí)鐘區(qū)域之間的關(guān)系。這可能是一個(gè)時(shí)鐘能夠i / o驅(qū)動(dòng)多個(gè)BUFIO和更進(jìn)一步的BUFR?提前致謝。求愛(ài)

2020-06-03 07:22:35

fpga I/O 引腳都一樣嗎?為什么有些管腳只能分配為輸入,有的只能為輸出?求大神指點(diǎn)

2015-05-27 08:12:40

PIC32MX795F512L,所有PIC管腳都有斷路,8個(gè)LED可以跳到,一個(gè)開(kāi)關(guān),SPI連接的微SD卡和USB端口。運(yùn)行代碼配置器,設(shè)置時(shí)鐘,定時(shí)器0和PORTA 0-7上的I/O管腳作為輸出。當(dāng)我生成代碼

2019-10-21 06:38:23

分配fpga管腳時(shí)該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個(gè)屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

通過(guò)前面的輸入輸出的內(nèi)容(LED控制與按鍵的使用),我們對(duì)控制I/O口有了一個(gè)基本的了解。如果需要輸出高低電平,可以對(duì)該引腳進(jìn)行寫(xiě)"1"或者"0";如果需要

2022-01-24 07:38:13

嗨, 我想把晶體振蕩器的CLK帶到FPGA里面的數(shù)字設(shè)計(jì)。該CLK連接到FPGA的I / O引腳。如果我在映射中運(yùn)行Impliment設(shè)計(jì),我將得到錯(cuò)誤。所以我將在UCF文件中將網(wǎng)名命名如下。NET

2019-01-29 10:05:43

控制系統(tǒng)為核電廠提供了各種控制和保護(hù)手段及監(jiān)控信息,保證了核電廠在正常啟動(dòng)、停堆、異常和事故工況下能夠安全、可靠和有效運(yùn)行。DCS系統(tǒng)I/O分配原則及I/O分配方法 yunrun.com.cn/tech

2018-02-22 13:18:08

使用INIT_B引腳(內(nèi)部路由)作為標(biāo)記非FPGASEU檢查結(jié)果的通用I / O,此外還可以根據(jù)積分配置錯(cuò)誤檢查結(jié)果進(jìn)行驅(qū)動(dòng)。我看到INIT_B被描述為“Dedicated”(UG362,表2-2,第27頁(yè)),所以我不確定它是否可以作為通用I / O運(yùn)行。如果沒(méi)有,我需要專門為此目的的另一個(gè)輸出引腳。

2020-06-10 15:09:16

將這些信號(hào)和FPGA的引腳進(jìn)行映射。 如圖所示,點(diǎn)擊ISE菜單上的“Tools à PlanAhead à I/O Pin Planning(PlanAhead) – Pre-Synthesis…”選項(xiàng)

2015-10-14 12:23:31

labview怎么實(shí)現(xiàn)像plc一樣的通過(guò)輸入輸出I/O量,控制開(kāi)關(guān)量,比如通過(guò)I/O點(diǎn)控制繼電器的吸合。怎么給I/O量分配地址,怎么在程序里使用這些變量實(shí)現(xiàn)一系列有序的動(dòng)作。希望能附上一份樣例程序,讓小弟學(xué)習(xí)領(lǐng)會(huì),請(qǐng)多指教,謝謝。

2016-04-25 00:51:33

我想使用外部1K Hz時(shí)鐘或?qū)懭胗龅酱a將時(shí)鐘分配到K Hz電平,它會(huì)起作用嗎? 第二個(gè)問(wèn)題是如何定義I / O類型,我想使用單個(gè)lvcmos3.3V作為I / O標(biāo)準(zhǔn)。我應(yīng)該在哪里定義I / O標(biāo)準(zhǔn)?在代碼中我還是需要將供應(yīng)跳線改為3.3位置?感謝您的幫助!

2020-04-29 09:22:03

外部時(shí)鐘信號(hào)。? rst_I 同步重起信號(hào)。? arst_I 異步重起信號(hào)。? adr_I 從節(jié)點(diǎn)地址。? dat_I 輸入數(shù)據(jù)。? dat_o 輸出數(shù)據(jù)。? we_I 寫(xiě)有效信號(hào)。? stb_I

2018-10-09 11:28:28

時(shí)鐘XCLK引腳用定時(shí)器來(lái)控制I/O做10M時(shí)鐘,沒(méi)行通,也不知道這種方法可不可行。想問(wèn)下官網(wǎng)工程師們能不能替我解決下問(wèn)題。。

2020-04-09 15:39:38

I/O控制對(duì)于單片機(jī)而言是最基礎(chǔ)最核心的東西,其實(shí)單片機(jī)除了模/數(shù)轉(zhuǎn)換之外的事情。其他大部分的事情I/O口都能做的到。I/O控制簡(jiǎn)單卻能千變?nèi)f化。單片機(jī)在大部分應(yīng)用中做的事情,莫過(guò)于 輸入高低

2021-11-24 06:47:23

美國(guó)國(guó)家儀器有限公司(National Instruments,簡(jiǎn)稱NI)近日針對(duì)PXI平臺(tái),推出了一個(gè)全新的、開(kāi)放式的、基于FPGA的產(chǎn)品系列。NI FlexRIO系列產(chǎn)品是工業(yè)領(lǐng)域首款成熟商用現(xiàn)成產(chǎn)品,它為工程師們提供了同時(shí)結(jié)合高速、工業(yè)級(jí)I/O和NI LabVIEW FPGA技術(shù)的解決方案。

2019-10-29 07:03:11

(從而將輸入輸出時(shí)延控制在允許的范圍內(nèi)),需要在時(shí)鐘驅(qū)動(dòng)器和負(fù)載之間插入時(shí)鐘緩沖器。DCM可用作時(shí)鐘輸入引腳和邏輯塊之間的時(shí)鐘緩沖器。 最后,還可以使用DCM將輸入時(shí)鐘信號(hào)轉(zhuǎn)換為差分I/O標(biāo)準(zhǔn)

2020-04-25 07:00:00

嗨,我使用的是Virtex-7 FPGA。我們通過(guò)專用時(shí)鐘引腳等成功設(shè)置了多個(gè)時(shí)鐘輸入。然而,當(dāng)我使用標(biāo)準(zhǔn)I / O引腳作為時(shí)鐘輸入時(shí),我無(wú)法獲得synplify-rpo 2014.09將輸入識(shí)別為“聲明”時(shí)鐘。我總是得到一個(gè)推斷時(shí)鐘,這打破了門控時(shí)鐘樹(shù)構(gòu)建下來(lái)。任何幫助贊賞。西蒙

2020-07-30 08:30:40

,而是指著電路設(shè)計(jì)的可選擇性豐富而言的。話說(shuō)回來(lái),這里的“自由”也還是要建立在一定的基礎(chǔ)之上的。筆者根據(jù)多年的工程經(jīng)驗(yàn),對(duì)于I/O與外設(shè)的連接擴(kuò)展,歸納出以下一些要點(diǎn):● 輸入和輸出時(shí)鐘信號(hào)盡量分配到專用

2016-07-30 18:19:39

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載49:PWM蜂鳴器驅(qū)動(dòng)之引腳分配特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i

2018-02-27 21:50:07

CPU、ASIC 或 FPGA 等數(shù)字電路。電源旁路將幫助過(guò)濾掉其中一部分噪聲,而剩下的噪聲則將影響器件性能。在剩余噪聲影響時(shí)鐘分配器件電源時(shí),會(huì)導(dǎo)致窄帶相位調(diào)制以及時(shí)鐘輸出的幅度調(diào)制。在 100kHz

2018-09-17 16:12:25

走線將CCLK輸出引腳連接到另一個(gè)FPGA I / O引腳,還是可以在內(nèi)部連接到它?我沒(méi)有看到有CCLK的原理圖庫(kù)部件。有沒(méi)有辦法做到這一點(diǎn)?謝謝你,-J以上來(lái)自于谷歌翻譯以下為原文If i read

2019-05-07 13:40:54

大家好,我剛開(kāi)始學(xué)習(xí)FPGA并試圖弄清楚哪些FPGA引腳可以分配我的數(shù)據(jù)信號(hào)。我正在使用FPGA Spartan 6封裝TQG114器件LX9。查看產(chǎn)品規(guī)格,有102個(gè)可用的用戶I / O.這是

2019-04-23 06:55:23

先分配差分I/O。然后,分配電壓參考I/O和相關(guān)的VREF管腳,它們可以從任何綁定的I/O中進(jìn)行配置。最后,對(duì)所有其它單端I/O進(jìn)行分配。Altera:雖然靈活的管腳分配對(duì)FPGA很重要,但某種程度

2012-02-27 15:18:09

的 BANK 中2、 掌握 FPGA 內(nèi)部 BANK 的分配的情況。現(xiàn)在 FPGA 內(nèi)部都分成幾個(gè)區(qū)域,每個(gè)區(qū)域中可用的 I/O 管腳數(shù)量各不相同。在 IC 驗(yàn)證中都是采用了ALTERA

2015-01-06 17:38:22

TinyOS系統(tǒng)下的I/O控制程序,并給出在CC2340芯片上實(shí)現(xiàn)的結(jié)果,可用來(lái)控制對(duì)Sink節(jié)點(diǎn)的輸入和輸出.對(duì)該程序進(jìn)行一定的擴(kuò)展和改進(jìn)便可以實(shí)現(xiàn)對(duì)Sink節(jié)點(diǎn)與節(jié)點(diǎn)通信和數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">控制. 0

2018-11-13 16:27:39

同步數(shù)字系統(tǒng)中的時(shí)鐘信號(hào)(如遠(yuǎn)程通信中使用的)為系統(tǒng)中的數(shù)據(jù)傳送定義了時(shí)間基準(zhǔn)。一個(gè)時(shí)鐘分配網(wǎng)絡(luò)由多個(gè)時(shí)鐘信號(hào)組成,由一個(gè)點(diǎn)將所有信號(hào)分配給需要時(shí)鐘信號(hào)的所有組件。因?yàn)?b class="flag-6" style="color: red">時(shí)鐘信號(hào)執(zhí)行關(guān)鍵的系統(tǒng)功能,很顯然應(yīng)給予更多的關(guān)注,不僅在時(shí)鐘的特性(即偏移和抖動(dòng))方面,還有那些組成時(shí)鐘分配網(wǎng)絡(luò)的組件。

2019-10-16 07:11:33

大家好,我使用PIC18F4620 40PIN DIP封裝,大約30的I/O引腳沒(méi)有使用。我不知道我應(yīng)該把它們留在硬件中,還是應(yīng)該把它們綁定到VDD或VSS?在軟件中也推薦使用未使用的I/O引腳

2019-01-25 14:33:08

我是使用virtex 4的先行者。我正在使用ISE xilinx13.1和verilog。我通過(guò)配置LVCOM33,拉式無(wú),轉(zhuǎn)換速率快,為j6端口的pin2分配了一個(gè)時(shí)鐘輸入信號(hào)。但我無(wú)法觀察到波形。任何人都可以指導(dǎo)我 - 如何使用I / O?

2019-09-04 10:35:35

如何克服FPGA I/O引腳分配挑戰(zhàn)?

2021-05-06 08:57:22

如何在PlanAhead I / O引腳分配中啟動(dòng)LVDS系統(tǒng)時(shí)鐘? I / O STD列中沒(méi)有LVDS選項(xiàng)?

2019-09-17 08:19:59

正確。我的問(wèn)題是 - 1)警告可以被忽略嗎?如果沒(méi)有,我怎么能擺脫上述警告?我只在CPLD實(shí)施的情況下看到它。如果我將設(shè)備更改為virtex FPGA,警告就會(huì)消失2)如何約束內(nèi)部生成的i2s_o時(shí)鐘

2019-04-12 14:24:54

你好先生:我有一個(gè)關(guān)于Spartan-6時(shí)鐘I / O引腳的問(wèn)題,數(shù)據(jù)表“UG382第24頁(yè)”就是說(shuō)“P和N輸入遵循與時(shí)鐘輸入引腳上的標(biāo)準(zhǔn)輸入相同的配置”,但我不知道其含義這個(gè)描述。我想這意味著

2019-07-15 14:04:11

嗨專家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平臺(tái)線USB II。你能告訴我如何通過(guò)JTAG監(jiān)控PC中FPGA I / O的狀態(tài)嗎?謝謝,V。Prakash以上來(lái)自于谷歌翻譯

2019-06-18 09:05:14

一定能夠滿足特殊 I/O 的需要。 近期最值得一提的技術(shù)躍進(jìn),即為適用于 PXI 的 NI FlexRIO 硬體;不僅整合了其他 NI 系統(tǒng)中的 LabVIEW FPGA 技術(shù),并具有開(kāi)放式的使用者客

2019-04-28 10:04:14

嗨,我是第一次在Fpga工作。我為所有32個(gè)收發(fā)器提供125 MHz差分時(shí)鐘。現(xiàn)在我需要為I / O bank提供125 MHz差分時(shí)鐘。有沒(méi)有辦法使用GTX時(shí)鐘用于這個(gè)目的(正如我讀到的,MRCC

2020-07-15 09:48:46

使用器件XC2S100E-6TQ144,我需要將4個(gè)GCK引腳中的3個(gè)配置為通用I / O引腳。第4個(gè)GCK用作100MHz時(shí)鐘。當(dāng)我使用其他3個(gè)GCK引腳作為通用I / O引腳時(shí),在“器件

2019-05-08 08:00:24

圖片一是我需要110個(gè)I/O接口,圖片二是板子的所有接口,問(wèn)一下我該如何分配接口?????

2016-10-25 15:05:04

我想用布爾開(kāi)關(guān)來(lái)控制I/O輸出的高低電平,請(qǐng)問(wèn)出現(xiàn)圖片這種情況,該怎么解決。還有如果要用8個(gè)開(kāi)關(guān)控制8個(gè)口要用8個(gè)DAQ助手還是可以合在一起的。

2017-05-13 23:01:59

大家好,物理封裝引腳分配完成后,ISE自動(dòng)推斷I / O芯片分配使用LOC約束。有沒(méi)有辦法明確分配特定的I / O芯片墊?謝謝。以上來(lái)自于谷歌翻譯以下為原文Hi All, ISE

2019-02-14 12:12:04

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應(yīng)用程序中,我可以使用哪些方法來(lái)檢查這些?請(qǐng)?zhí)峁┮恍┫敕āVx謝

2019-04-01 12:33:26

FPGA的I/O口如果作為input,輸入外部控制信號(hào),電平還有其他設(shè)置等等,與作output時(shí)有什么區(qū)別?

2016-06-21 12:50:04

求西門子PLC控制沼氣發(fā)電程序 I\o分配表謝謝

2016-10-15 16:16:11

您好,最近在設(shè)計(jì)一款雷達(dá),發(fā)射板、接收板、和信號(hào)處理板,發(fā)射板使用的是FPGA控制+PLL產(chǎn)生發(fā)射波形和本振,想知道這個(gè)FPGA的時(shí)鐘、PLL的時(shí)鐘,信號(hào)處理板的時(shí)鐘,是使用一個(gè)晶振的來(lái)分配時(shí)鐘呢

2019-01-02 15:36:07

輕松實(shí)現(xiàn)高速串行I/OFPGA應(yīng)用設(shè)計(jì)者指南輸入/輸出(I/O)在計(jì)算機(jī)和工業(yè)應(yīng)用中一直扮演著關(guān)鍵角色。但是,隨著信號(hào)處理越來(lái)越復(fù)雜,I/O通信會(huì)變得不可靠。在早期的并行I/O總線中,接口的數(shù)據(jù)對(duì)齊

2020-01-02 12:12:28

使用LabVIEW FPGA 模塊和可重新配置I/O 設(shè)備開(kāi)發(fā)測(cè)量與控制應(yīng)用通過(guò)使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

FPGA怎么選擇?針對(duì)功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 本文闡述了用于FPGA的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探討了FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案。

2010-08-06 16:08:45 12

12 摘要:介紹了為PET(正電子發(fā)射斷層掃描儀)的前端電子學(xué)模塊提供時(shí)間基準(zhǔn)而設(shè)計(jì)的一種新型高頻時(shí)鐘扇出電路。該電路利用FPGA芯片來(lái)實(shí)現(xiàn)對(duì)高頻時(shí)鐘的分頻

2009-06-20 12:41:04 1238

1238

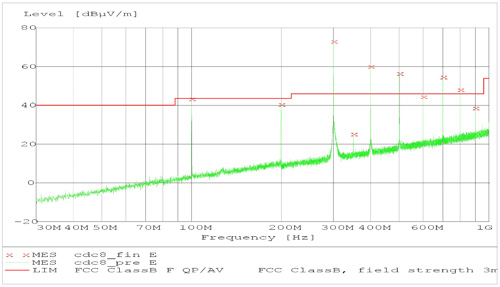

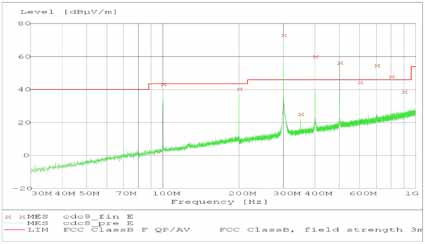

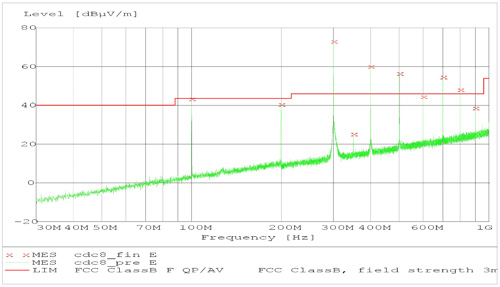

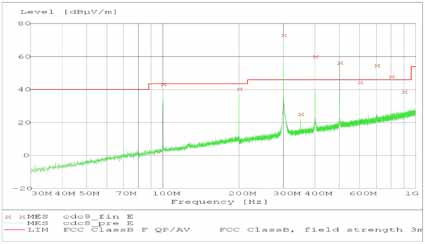

控制板級(jí)時(shí)鐘分配期間出現(xiàn)的EMI

今天,我們來(lái)談?wù)勊须娮酉到y(tǒng)都存在的一種常見(jiàn)問(wèn)題——電磁干擾也即 EMI,并側(cè)重討論時(shí)鐘的影響。

從廣義來(lái)講,EMI&n

2010-01-19 11:13:14 1958

1958

控制板級(jí)時(shí)鐘分配期間出現(xiàn)的 EMI

今天,我們來(lái)談?wù)勊须娮酉到y(tǒng)都存在的一種常見(jiàn)問(wèn)題——電磁干擾也即 EMI,并側(cè)重討論時(shí)鐘的影響。

從廣義來(lái)講,EMI 是

2010-01-21 09:36:19 874

874

在FPGA設(shè)計(jì)中,為了成功地操作,可靠的時(shí)鐘是非常關(guān)鍵的。設(shè)計(jì)不良的時(shí)鐘在極限的溫度、電壓下將導(dǎo)致錯(cuò)誤的行為。在設(shè)計(jì)PLD/FPGA時(shí)通常采用如下四種類型時(shí)鐘:全局時(shí)鐘、門控時(shí)鐘

2011-09-21 18:38:58 3472

3472

設(shè)計(jì)過(guò)FPGA的原理圖,看FPGA的手冊(cè),說(shuō)管腳的分配問(wèn)題,如時(shí)鐘管腳要用GC類管腳,而且單端時(shí)鐘輸入時(shí)要用P類型的管腳,不能用N類型管腳等等。

2017-02-11 03:48:34 10684

10684

本文檔的主要內(nèi)容詳細(xì)介紹的是spartan-6 FPGA的時(shí)鐘資源的用戶指南資料免費(fèi)下載。

2019-02-15 16:39:07 27

27 ,并與內(nèi)部 FPGA 時(shí)鐘實(shí)現(xiàn)中心對(duì)齊。在這個(gè)方案中,內(nèi)部 FPGA時(shí)鐘采集傳出的數(shù)據(jù)。存儲(chǔ)器傳出的時(shí)鐘/ 選通脈沖用于決定與數(shù)據(jù)位相關(guān)的延遲值。因此,與選通脈沖相關(guān)的數(shù)據(jù)位的數(shù)量不受限制。由于無(wú)需將選通脈沖分配給相關(guān)數(shù)據(jù)位,所以不需要其他時(shí)鐘資源。

2020-11-26 10:01:31 1219

1219

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之理解FPGA時(shí)鐘資源的工程文件免費(fèi)下載。

2020-12-10 14:20:11 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之FPGA時(shí)鐘資源的工程文件免費(fèi)下載。

2020-12-10 15:00:29 15

15 超低抖動(dòng)時(shí)鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì)畢業(yè)設(shè)計(jì)論文免費(fèi)下載。

2021-05-28 10:49:19 56

56 本章的主要內(nèi)容: 分析時(shí)鐘驅(qū)動(dòng)器、時(shí)鐘信號(hào)的特殊布線 改進(jìn)時(shí)鐘信號(hào)分配的特殊電路

2022-09-20 14:55:40 0

0 如何優(yōu)化 PCIe 應(yīng)用中的時(shí)鐘分配

2022-11-07 08:07:15 0

0 控制板級(jí)時(shí)鐘分配期間出現(xiàn)的 EMI

2022-11-07 08:07:32 0

0 電子發(fā)燒友網(wǎng)站提供《使用FPGA的數(shù)字時(shí)鐘(計(jì)時(shí)表).zip》資料免費(fèi)下載

2022-11-23 10:38:36 5

5 基于FPGA的高頻時(shí)鐘的分頻和分頻設(shè)計(jì)

2023-08-16 11:42:47 0

0 第11章時(shí)鐘分配

2022-12-30 09:21:58 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論