從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過將配

2011-10-12 15:16:25 1414

1414

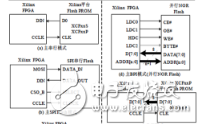

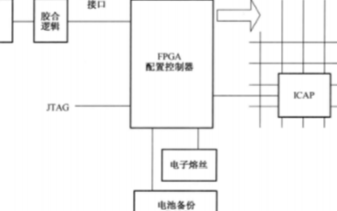

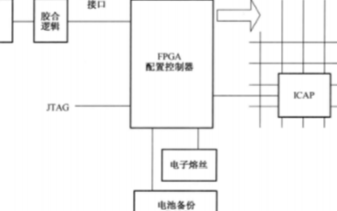

通過FPGA的多重配置可以有效地精簡(jiǎn)控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開發(fā)板和配置存儲(chǔ)器SPI FLASH為基礎(chǔ),從硬件電路

2014-01-24 14:17:22 13670

13670

利用FPGA可重復(fù)編程的特性,通過脫機(jī)配置,建立BIST邏輯,即使由于線路被操作系統(tǒng)的重新配置而令BIST結(jié)構(gòu)消失,可測(cè)性也可實(shí)現(xiàn)。本文給出一種基于BIST利用ORCA(Optimized

2018-11-28 09:02:00 4021

4021

測(cè)試,而且基本上可以達(dá)到不用敲代碼就可以完成測(cè)試的目的。 下面按步驟,一步一步實(shí)現(xiàn)。重點(diǎn)的地方我會(huì)標(biāo)注出來(lái)。 (1)新建工程,只需選擇好與板卡對(duì)應(yīng)的FPGA型號(hào)即可,無(wú)須添加任何文件。 (2)添加ibert IP。 (3)配置IP: 這里我們先只配置一個(gè)quad,也

2020-12-31 15:36:04 6617

6617 我們所說的FPGA配置電路,一方面要完成從PC上把bit文件下載到FPGA或存儲(chǔ)器的任務(wù),另一方面則要完成FPGA上電啟動(dòng)時(shí)加載配置數(shù)據(jù)的任務(wù)。

2023-06-10 10:09:52 317

317

FPGA(Field-Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)是一種特殊的集成電路,其內(nèi)部結(jié)構(gòu)由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來(lái)實(shí)現(xiàn)各種數(shù)字系統(tǒng)功能

2024-01-26 10:03:55

配置電路本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 上世紀(jì)八十年代,聯(lián)合測(cè)試行為組織(Joint

2019-01-30 02:34:52

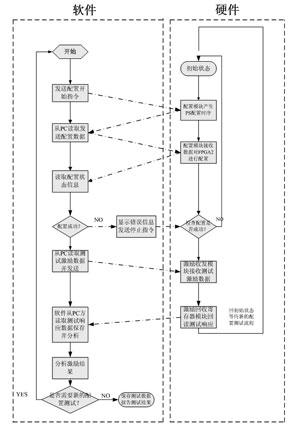

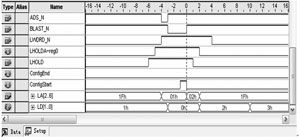

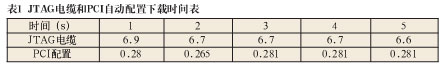

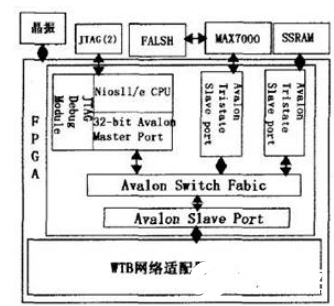

數(shù)據(jù)的分析來(lái)診斷故障。因此,用于FPGA測(cè)試的儀器或系統(tǒng)的關(guān)鍵技術(shù)在于:如何加快單次配置的時(shí)間,以節(jié)省測(cè)試過程中的配置時(shí)間開銷;如何實(shí)現(xiàn)自動(dòng)重復(fù)配置和測(cè)試,將FPGA較快速度的在線配置和快速測(cè)試結(jié)合起來(lái)

2020-05-14 07:00:00

配置電路本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 上世紀(jì)八十年代,聯(lián)合測(cè)試行為組織(Joint

2015-04-13 12:29:55

配置歷史回顧當(dāng)FPGA首次面世時(shí),可選擇的配置存儲(chǔ)器是并行EPROM或并行EEPROM產(chǎn)品。隨著時(shí)間的推移,NOR閃存技術(shù)應(yīng)運(yùn)而生,同時(shí)因其系統(tǒng)內(nèi)可重復(fù)編程性和高性價(jià)比而被廣泛采用。在第二次革命性轉(zhuǎn)折

2021-09-03 07:00:00

用vhdl實(shí)現(xiàn)cpld配置fpga,配置成功后在usermode下設(shè)置一個(gè)重新配置信號(hào),當(dāng)信號(hào)有效時(shí)對(duì)fpga進(jìn)行重新配置;fpga配置程序放在flash內(nèi);現(xiàn)在遇到的問題是,上電cpld能夠正常配置fpga并且進(jìn)入usermode ,但是加上重新配置語(yǔ)句過后就不能成功配置fpga,求高人指點(diǎn)~

2013-01-17 22:35:39

摘要針對(duì)FFT算法基于FPGA實(shí)現(xiàn)可配置的IP核。采用基于流水線結(jié)構(gòu)和快速并行算法實(shí)現(xiàn)了蝶形運(yùn)算和4k點(diǎn)FFT的輸入點(diǎn)數(shù)、數(shù)據(jù)位寬、分解基自由配置。使用Verilog語(yǔ)言編寫,利用ModelSim

2019-07-03 07:56:53

例說FPGA連載13:靈活定制——配置電路特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 上世紀(jì)八十年代,聯(lián)合測(cè)試行為組織(Joint

2016-07-27 16:45:59

FPGA可重復(fù)配置和測(cè)試系統(tǒng)結(jié)構(gòu)概述FPGA重復(fù)配置和測(cè)試的實(shí)現(xiàn)

2021-04-29 06:58:20

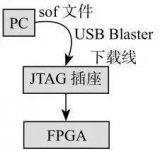

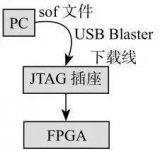

訪問端口和邊界掃描結(jié)構(gòu)標(biāo)準(zhǔn)。隨著芯片設(shè)計(jì)和制造技術(shù)的快速發(fā)展,JTAG越來(lái)越多的被用于電路的邊界掃描測(cè)試和可編程芯片的在線系統(tǒng)編程。 FPGA器件都支持JTAG進(jìn)行在線配置,JTAG邊界掃描的基本原理

2017-10-24 21:26:26

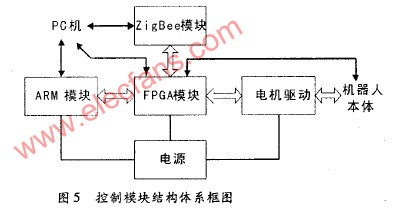

基于JTAG接口實(shí)現(xiàn)ARM的FPGA在線配置設(shè)計(jì)

2012-08-19 23:17:24

從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。

2019-10-31 06:26:05

如何實(shí)現(xiàn)自動(dòng)重復(fù)配置和FPGA測(cè)試,將FPGA較快速度的在線配置和快速測(cè)試結(jié)合起來(lái)。

2021-04-08 06:14:46

配置歷史回顧當(dāng)FPGA首次面世時(shí),可選擇的配置存儲(chǔ)器是并行EPROM或并行EEPROM產(chǎn)品。隨著時(shí)間的推移,NOR閃存技術(shù)應(yīng)運(yùn)而生,同時(shí)因其系統(tǒng)內(nèi)可重復(fù)編程性和高性價(jià)比而被廣泛采用。在第二次革命性轉(zhuǎn)折

2021-05-26 07:00:00

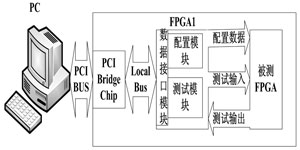

本文的設(shè)計(jì)是基于FPGA實(shí)現(xiàn)邏輯芯片的功能故障測(cè)試。由于FPGA芯片價(jià)格的不斷下降和低端芯片的不斷出現(xiàn),使用FPGA作為主控芯片可以更適合于市場(chǎng),且有利于對(duì)性能進(jìn)行擴(kuò)展。實(shí)驗(yàn)表明,該系統(tǒng)設(shè)計(jì)合理,能對(duì)被測(cè)芯片進(jìn)行準(zhǔn)確的功能測(cè)試。

2021-04-30 06:13:48

本文介紹了通過處理機(jī)用CPLD和Flash實(shí)現(xiàn)FPGA配置文件下載更新的方法。

2021-04-28 06:11:19

Xilinx FPGA的配置方式何用PowerPC860實(shí)現(xiàn)FPGA配置

2021-04-08 06:46:46

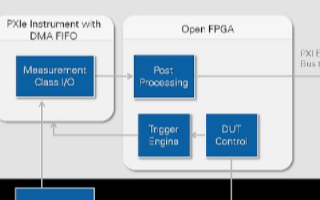

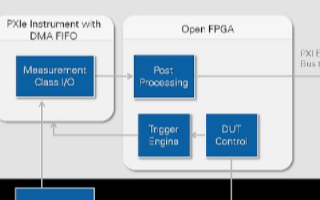

列出了在測(cè)試應(yīng)用中使用FPGA的一些關(guān)鍵特性:● 確定性,實(shí)時(shí)處理● 真正并行的執(zhí)行● 可重配置● 低延時(shí)更進(jìn)一步講,利用開放式FPGA可以實(shí)現(xiàn)哪些以前不能實(shí)現(xiàn)的功能呢?為了描述這些可能性,下面將介紹

2021-07-13 08:00:00

怎么實(shí)現(xiàn)基于FPGA的VRLA蓄電池測(cè)試系統(tǒng)的設(shè)計(jì)?

2021-05-10 06:22:19

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號(hào)發(fā)生器,一路虛擬存儲(chǔ)示波器,具有外部觸發(fā)信號(hào)和采樣時(shí)鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

基于ARM的嵌入式系統(tǒng)從串配置FPGA的實(shí)現(xiàn)

2021-03-03 06:16:30

我一直在嘗試讓GPIO(RA4)在PIC32MX274F256D的SOSCO管腳上工作。實(shí)際上我正在嘗試的是讓SDO1工作,但是在確定無(wú)法完成工作之后,將管腳配置為GPIO并重復(fù)測(cè)試。請(qǐng)注意,我可以

2020-03-25 10:45:01

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠實(shí)現(xiàn)端口0的外部回環(huán)測(cè)試。fpga端的協(xié)議還沒做通,我想用dsp直接給fpga發(fā)包,fpga根據(jù)收到

2018-06-21 10:45:13

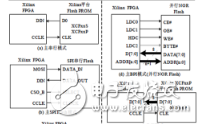

XC2S200型FPGA器件實(shí)現(xiàn)。采用Spansion公司的NOR Flash存儲(chǔ)器來(lái)存放配置文件,其型號(hào)為S29GL512N,容量為512 Mb。系統(tǒng)總體框圖如圖3所示。上位機(jī)軟件包括Flash燒寫

2019-05-30 05:00:05

非易失可重復(fù)編程FPGA的應(yīng)用有哪些?

2021-05-08 08:17:26

介紹如何用PowerPC860(MPC860)進(jìn)行FPGA(Xilinx 的Virtex-II 系列)的配置;給出進(jìn)行FPGA 配置所需的詳細(xì)時(shí)序圖和原理圖。本配置基本原理對(duì)其它FPGA 的配置也適用。

2009-04-16 14:11:36 18

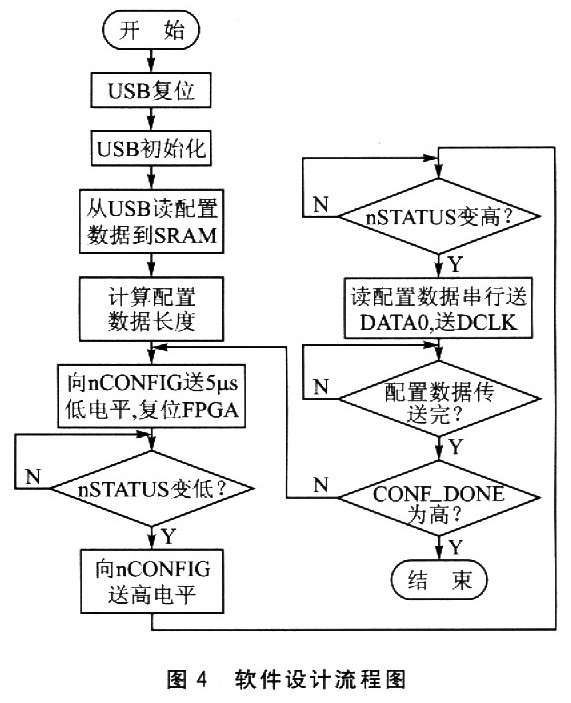

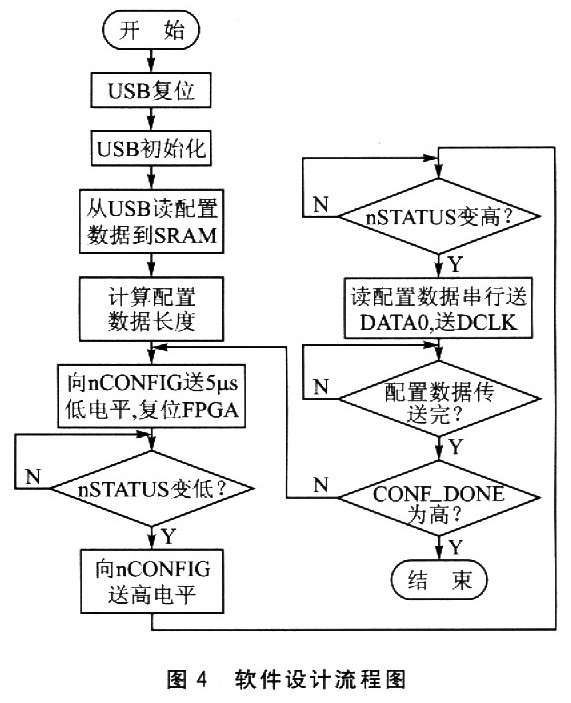

18 本文提出了一種基于USB 接口的FPGA SelectMap 配置方式的實(shí)現(xiàn)方案。方案以大容量Spartan3 FPGA 作為配置目標(biāo),選用Cypress EZ-USB FX2LP 作為USB 設(shè)備芯片,采用其內(nèi)置的端點(diǎn)FIFO 和GPIF 狀態(tài)

2009-05-26 10:25:33 28

28 本文提出了一種使用FPGA 實(shí)現(xiàn)誤碼率測(cè)試的設(shè)計(jì)及實(shí)現(xiàn)方法。該設(shè)計(jì)可通過FPGA 內(nèi)建的異步串行接口向主控計(jì)算機(jī)傳遞誤碼信息,也可以通過數(shù)碼管實(shí)時(shí)顯示一段時(shí)間內(nèi)的誤碼率。文

2009-06-26 17:32:46 55

55 本文提出了在uClinux 嵌入式操作系統(tǒng)中應(yīng)用MCU 實(shí)現(xiàn)對(duì)FPGA 的一種配置方案。該方案實(shí)現(xiàn)了FPGA 配置數(shù)據(jù)的加密、壓縮,減少了配置文件對(duì)嵌入式存儲(chǔ)資源的占用,并且實(shí)現(xiàn)了FPGA 資源

2009-08-13 09:16:53 6

6 AMCC 公司出品的鏈路層處理芯片S19202 在實(shí)際應(yīng)用中需要先進(jìn)行硬件配置。通過在FPGA 內(nèi)部編程將其實(shí)現(xiàn)。本文介紹其實(shí)現(xiàn)方法,并給出了時(shí)序仿真波形和測(cè)試結(jié)果

2009-08-31 17:43:07 8

8 針對(duì)基于SRAM 結(jié)構(gòu)的FPGA,詳細(xì)介紹了一種采用可在線升級(jí)的SST89V564RD微處理器對(duì)其進(jìn)行上電PPA(被動(dòng)并行異步)配置,不僅實(shí)現(xiàn)了FPGA 的在線配置,而且通過微處理器的IAP 技術(shù)

2009-09-15 16:27:50 23

23 基于單片機(jī)的CPLD/FPGA被動(dòng)串行下載配置的實(shí)現(xiàn):介紹采用AT89S2051單片機(jī)配合串行E2PROM存儲(chǔ)器,實(shí)現(xiàn)CPLD/FPGA器件的被動(dòng)串行模式的下載配置,闡述了其原理及軟硬件設(shè)計(jì)。 &nb

2009-10-29 21:57:22 19

19 用可再配置FPGA實(shí)現(xiàn)DSP功能

2010-07-16 17:56:43 10

10 本文介紹了基帶測(cè)試系統(tǒng)中,如何應(yīng)用FPGA實(shí)現(xiàn)后臺(tái)計(jì)算機(jī)與測(cè)試環(huán)境數(shù)據(jù)交互以及存儲(chǔ)的電路設(shè)計(jì)流程,并已在某基站測(cè)試系統(tǒng)中成功應(yīng)用。

2010-08-09 15:00:32 27

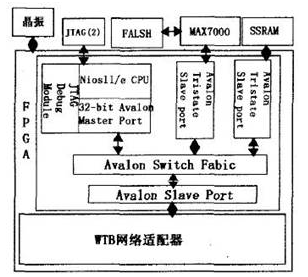

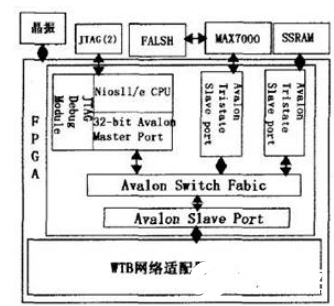

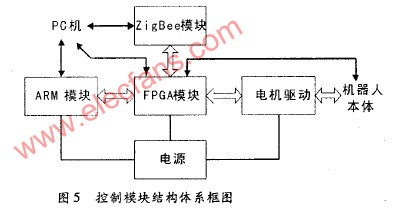

27 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺(tái)設(shè)計(jì)方法。給出了系統(tǒng)設(shè)計(jì)的硬件結(jié)構(gòu)和重要接口, 提出了由ARM微處理器通過JTAG在系統(tǒng)配置FPGA的方法, 以滿足重配置系統(tǒng)中軟件

2010-09-14 16:40:09 21

21 在當(dāng)今復(fù)雜數(shù)字電路設(shè)計(jì)中,大多采用以“嵌入式微控制器+FPGA”為核心的體系結(jié)構(gòu)。提出了一種對(duì)現(xiàn)有傳統(tǒng)FPGA配置方案硬件電路稍做調(diào)整并增加部分軟件功能,即可實(shí)現(xiàn)FPGA動(dòng)態(tài)

2010-12-08 15:52:01 19

19 設(shè)計(jì)了一種基于FPGA的單板單片主控器件的低成本即插即用虛擬測(cè)試系統(tǒng)。系統(tǒng)包括兩路分立信號(hào)源、一路虛擬存儲(chǔ)示波器和16路高速虛擬邏輯分析儀,結(jié)合FPGA、高速DAC/ADC設(shè)計(jì)特點(diǎn),

2010-12-14 10:07:12 16

16 FPGA的全局動(dòng)態(tài)可重配置技術(shù)主要是指對(duì)運(yùn)行中的FPGA器件的全部邏輯資源實(shí)現(xiàn)在系統(tǒng)的功能變換,從而實(shí)現(xiàn)硬件的時(shí)分復(fù)用。提出了一種基于System ACE的全局動(dòng)態(tài)可重配置設(shè)計(jì)方法,

2011-01-04 17:06:01 54

54 摘要:介紹如何用PowerPC860(MPC860)進(jìn)行FPGA(Xilinx的Virtex-II系列)的配置;給出進(jìn)行FPGA配置所需的詳細(xì)時(shí)序圖和原理圖。本配置基本原理對(duì)其它FPGA的配置也適用。

2009-06-20 11:02:38 942

942

摘要: 在反輻射導(dǎo)彈的雷達(dá)導(dǎo)引頭中,信號(hào)跟蹤器的實(shí)時(shí)性是影響系統(tǒng)性能的重要因素之一。介紹了利用高性能FPGA豐富的資源實(shí)現(xiàn)的多路脈沖重復(fù)頻率跟

2009-06-20 15:34:23 523

523

FPGA 重復(fù)配置和測(cè)試的實(shí)現(xiàn)

從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括

2009-09-03 11:17:08 528

528

用于系統(tǒng)級(jí)測(cè)試和PCB配置的高級(jí)拓?fù)浣Y(jié)構(gòu)

本文討論的SELEX 空中雷達(dá)使用了可擴(kuò)展設(shè)計(jì),它具有動(dòng)態(tài)可重復(fù)配置的活動(dòng)背板,為

2009-11-17 13:46:32 463

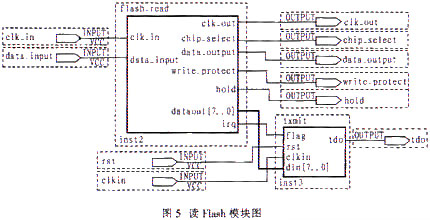

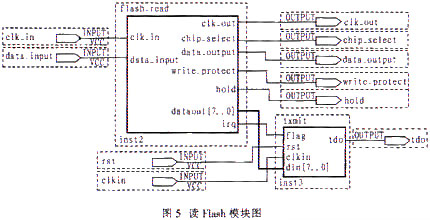

463 基于FPGA的串行Flash擴(kuò)展實(shí)現(xiàn)

FPGA憑借其方便靈活、可重復(fù)編程等優(yōu)點(diǎn)而日益被廣泛應(yīng)用;閃速存儲(chǔ)器(Flash Memory)以其集成度高、成本低、使用方便等優(yōu)點(diǎn),在眾多領(lǐng)域中

2010-01-12 10:39:55 1363

1363

基于U盤和單片機(jī)的FPGA配置??

引 言FPGA廣泛應(yīng)用在電子通信領(lǐng)域,其安全性引起了注意,本文針對(duì)安全配置提出了解決方案。

現(xiàn)場(chǎng)可編程門陣列FPGA(F

2010-01-14 09:27:24 1175

1175

基于FPGA的新型誤碼測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

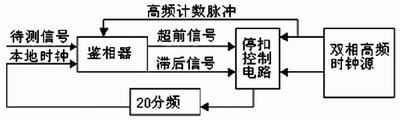

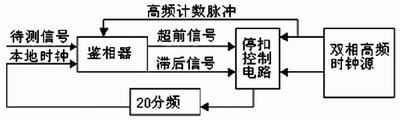

本文設(shè)計(jì)實(shí)現(xiàn)了一種用于測(cè)量基帶傳輸信道的誤碼儀,闡述了主要模塊的工作原理,提出了一種新的積分鑒相同步時(shí)鐘提取的實(shí)

2010-02-09 10:42:01 876

876

摘要:文中詳述了FPGA被動(dòng)串行配置方式的時(shí)序,給出配置流程圖及實(shí)現(xiàn)的程序代碼,并通過實(shí)例驗(yàn)證了該方法的優(yōu)越

2010-07-21 14:48:48 1326

1326

本文介紹了通過處理機(jī)用CPLD和Flash實(shí)現(xiàn)FPGA配置文件下載更新的方法。與傳統(tǒng)的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點(diǎn)

2018-10-25 05:51:00 8194

8194

傳統(tǒng)的距離門控電路多采用分立元器件,工作頻率和控制精度均十分有限,難于滿足重復(fù)頻率高的測(cè)距需求.通過分析高重復(fù)率距離門控的時(shí)序,提出并實(shí)現(xiàn)了一種基于FPGA的高重復(fù)率距離門控電路方法.該方法充分發(fā)揮了FPGA在運(yùn)算、存儲(chǔ)、時(shí)鐘管理等方面的優(yōu)勢(shì):采

2011-03-15 15:05:00 24

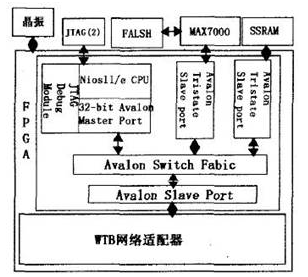

24 本文結(jié)合具體應(yīng)用需求,介紹了利用嵌入式CPU Leon3軟核處理器對(duì)Virtex系列FPGA的配置進(jìn)行控制的方法。此系統(tǒng)能夠實(shí)現(xiàn)FPGA配置數(shù)據(jù)的重構(gòu),并且減少了外圍CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3151

3151

FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設(shè)模式可以將FPGA作為微處理器的外設(shè),由微處理

2011-09-08 17:50:27 1734

1734 基于對(duì)FPGA系統(tǒng)失效機(jī)理的深入分析, 提出了軟件測(cè)試技術(shù)在FPGA測(cè)試中的應(yīng)用, 并分析了其可行性; 通過對(duì)比FPGA與軟件系統(tǒng)的異同, 歸納出FPGA特有的測(cè)試要求,從而在軟件測(cè)試技術(shù)的基礎(chǔ)

2011-09-29 17:41:21 65

65 基于SD卡的FPGA配置,本文給出了對(duì)Virtex FPGA 進(jìn)行配置的情 況,該方案也可以適用于Spartan 系列FPGA。

2011-12-13 10:02:42 6095

6095

本文核心提示: 隨著FPGA接口的速度提高,高速接口的測(cè)試、PCB板級(jí)的測(cè)試、EMI/EMC的測(cè)試等,這些測(cè)試的難度會(huì)越來(lái)越突出。想要實(shí)現(xiàn)FPGA的自動(dòng)化測(cè)試的話,就需要提高軟件的可控性和

2012-08-27 10:09:08 972

972 一種密鑰可配置的DES加密算法的FPGA實(shí)現(xiàn)

2016-05-11 11:30:19 11

11 基于DSP的FPGA配置方法研究與實(shí)現(xiàn)

2017-10-19 16:15:19 36

36 通過SELECTMAP32接口配置和回讀XILINX公司生產(chǎn)的V5系列SRAM型FPGA,被配置的FPGA以下簡(jiǎn)稱DUT,產(chǎn)生配置時(shí)序的FPGA簡(jiǎn)稱配置FPGA。首先硬件上應(yīng)將M[2:0]接成110

2017-11-17 10:16:01 8730

8730 NI可重復(fù)配置I/O(RIO)技術(shù)能夠讓您通過使用可重復(fù)配置的現(xiàn)場(chǎng)可編程門陣列(FPGA)芯片和NI LabVIEW圖形化開發(fā)工具,實(shí)現(xiàn)自定義的測(cè)量硬件電路。RIO核心包括FPGA芯片和外圍電路

2017-11-18 02:29:13 1731

1731 VeriStand是一個(gè)基于配置的實(shí)時(shí)測(cè)試軟件,它擁有與labVIEW類似的前面板,但無(wú)需任何編程工作。用戶可以使用labVIEW、matlab等其他軟件生成的模型文件導(dǎo)入VeriStand,方便快捷的實(shí)現(xiàn)硬件在環(huán)等實(shí)時(shí)測(cè)試應(yīng)用。 在VeriStand系統(tǒng)瀏覽器中,可以對(duì)NI的硬件設(shè)備實(shí)現(xiàn)參數(shù)配置。

2017-11-18 06:36:48 4323

4323

)等部分組成。對(duì)FPGA進(jìn)行測(cè)試要對(duì)FPGA內(nèi)部可能包含的資源進(jìn)行結(jié)構(gòu)分析,經(jīng)過一個(gè)測(cè)試配置(TC)和向量實(shí)施(TS)的過程,把FPGA配置為具有特定功能的電路,再?gòu)膽?yīng)用級(jí)別上對(duì)電路進(jìn)行測(cè)試,完成電路的功能及參數(shù)測(cè)試。 2 FPGA的配置方法 對(duì)FPGA進(jìn)行配置有多種方法可以選擇,包括邊界掃描配置方法等。

2017-11-18 10:44:37 2001

2001

反熔絲FPGA制造困難且多用在特殊用途領(lǐng)域,因此有關(guān)其位流文件的研究很少.本文首先介紹了反熔絲FPGA 及FPGA CAD軟件流程, 接著描述了反熔絲FPGA具體結(jié)構(gòu)并通過一個(gè)具體例子說明了如何配置

2017-11-18 11:19:01 10165

10165

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失(斷電不丟數(shù)據(jù))性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)(稱為

2017-11-22 09:24:02 6452

6452 的應(yīng)用。在主流的FPGA中,絕大多數(shù)都采用了SRAM來(lái)存放配置數(shù)據(jù),稱為SRAM FPGA。這種FPGA的突出優(yōu)點(diǎn)是可以進(jìn)行多次配置。通過給FPGA加載不同的配置數(shù)據(jù),即可令其實(shí)現(xiàn)不同的邏輯功能.FPGA這種可重配置的能力將給數(shù)字系統(tǒng)的設(shè)計(jì)帶來(lái)很大的方便。

2018-07-18 12:50:00 2407

2407

從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過

2017-11-24 20:55:53 5922

5922

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為

2017-11-26 08:12:51 7889

7889

在FPGA中實(shí)現(xiàn)在應(yīng)用編程(In Application Programming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來(lái)接收配置數(shù)據(jù),在被動(dòng)串行(PS)模式

2017-12-13 13:58:10 24009

24009

FPGA有多種配置/加載方式。粗略可以分為主動(dòng)和被動(dòng)兩種。主動(dòng)加載是指由FPGA控制配置流程,被動(dòng)加載是指FPGA僅僅被動(dòng)接收配置數(shù)據(jù)。

2018-10-05 10:12:00 17251

17251 介紹了采用CPLD和Flash器件對(duì)FPGA 實(shí)現(xiàn)快速并行配置,并給出了具體的硬件電路設(shè)計(jì)和關(guān)鍵模塊的內(nèi)部編程思路。

2018-10-24 15:15:49 7

7 Altera FPGA支持AS,PS,JTAG等幾種較常見的配置方法。 當(dāng)為AS配置模式時(shí),FPGA為主設(shè)備,加載外部FLASH中的數(shù)據(jù)至內(nèi)部RAM中運(yùn)行。當(dāng)為PS配置模式時(shí),FPGA為從設(shè)備,外部

2018-11-18 18:05:01 481

481 )來(lái)實(shí)現(xiàn)的,具有可重復(fù)編程性,可以靈活實(shí)現(xiàn)各種邏輯功能。由于FPGA器件采用的是SRAM 工藝,在斷電的情況下FPGA內(nèi)的配置數(shù)據(jù)將丟失。所以,在典型的采用FPGA器件的電子系統(tǒng)中通常將FPGA

2019-01-04 14:15:02 643

643

本文檔詳細(xì)介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細(xì)資料說明主要內(nèi)容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 )來(lái)實(shí)現(xiàn)的,具有可重復(fù)編程性,可以靈活實(shí)現(xiàn)各種邏輯功能。由于FPGA器件采用的是SRAM 工藝,在斷電的情況下FPGA內(nèi)的配置數(shù)據(jù)將丟失。所以,在典型的采用FPGA器件的電子系統(tǒng)中通常將FPGA

2020-01-21 17:10:00 764

764

Spartan-6 FPGA 利用CCL 支持布線線路與邏輯單元之間的可配置互聯(lián)功能。Spartan-6 FPGA 是易失性器件- 電源移除時(shí),不能保留原有配置。為了配置Spartan-6

2020-01-10 15:28:51 25

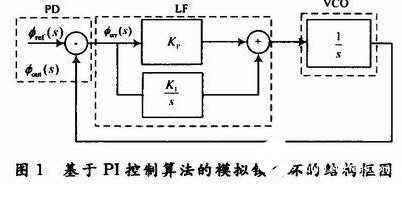

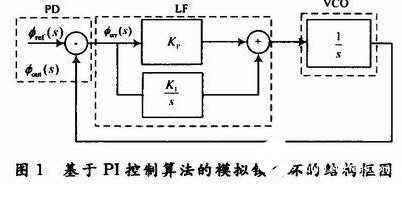

25 的鎖定、編譯適配下載到FPGA芯片,實(shí)現(xiàn)所設(shè)計(jì)的帶寬自適應(yīng)全數(shù)字鎖相環(huán),并完成硬件測(cè)試。在硬件測(cè)試中需要用到信號(hào)發(fā)生器和示波器,信號(hào)發(fā)生器用來(lái)產(chǎn)生鎖相環(huán)的輸入測(cè)試信號(hào),示波器用來(lái)觀測(cè)鎖相環(huán)的輸入/輸出波形。圖7為輸入信號(hào)Phi_ref取不同頻率時(shí)的實(shí)測(cè)波形。

2020-08-21 10:55:00 2158

2158

目前大多數(shù)儀器采用封閉式FPGA(現(xiàn)場(chǎng)可編程門陣列)和固定的固件實(shí)現(xiàn)儀器的功能。如果你曾見過示波器的拆解,你也許見過里面的FPGA。FPGA可以增加測(cè)試儀器的處理能力,如果你曾使用過儀器的開放式FPGA,你就會(huì)知道可以將自定義的測(cè)試功能編程進(jìn)儀器中。

2020-09-04 09:09:56 947

947

工藝的查找表結(jié)構(gòu),也有一些軍品和宇航級(jí)FPGA采用Flash或者熔絲與反熔絲工藝的查找表結(jié) 構(gòu)。通過燒寫文件改變查找表內(nèi)容的方法來(lái)實(shí)現(xiàn)對(duì)FPGA的重復(fù)配置。

2020-12-29 17:27:23 16

16 (5,3)整數(shù)小波變換的算法,接著闡述了一種多級(jí)二維(5,3)整數(shù)小波變換的FPGA實(shí)現(xiàn)結(jié)構(gòu),最后給出了硬件資源消耗、最大時(shí)鐘頻率和功能測(cè)試結(jié)果等FPGA實(shí)現(xiàn)結(jié)果。為了提高系統(tǒng)的處理速度,降低系統(tǒng)的資源消耗,本設(shè)計(jì)采用了參數(shù)可配置、共享

2021-02-01 11:53:33 9

9 所有現(xiàn)代FPGA的配置分為兩類:基于SRAM的和基于非易失性的。其中,前者使用外部存儲(chǔ)器來(lái)配置FPGA內(nèi)的SRAM后者只配置一次。 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置

2021-07-02 16:01:40 2781

2781

廣義的來(lái)說,FPGA的配置包括直接使用下載電纜對(duì)FPGA器件進(jìn)行編程、對(duì)外部EEPROM和FLASH進(jìn)行編程、使用MPU對(duì)FPGA器件進(jìn)行編程、外部EEPROM和FLASH對(duì)器件進(jìn)行編程

2021-09-06 09:41:56 6052

6052 電子學(xué)報(bào)第七期《一種可配置的CNN協(xié)加速器的FPGA實(shí)現(xiàn)方法》

2021-11-18 16:31:06 15

15 FPGA采用SRAM進(jìn)行功能配置,可重復(fù)編程,但系統(tǒng)掉電后,SRAM中的數(shù)據(jù)丟失,因此,需要在FPGA外加EPROM,將配置數(shù)據(jù)寫入其中,系統(tǒng)每次上電自動(dòng)將數(shù)據(jù)引入SRAM中。

2022-08-10 10:12:16 1119

1119 盡管FPGA的配置模式各不相同,但整個(gè)配置過程中FPGA的工作流程是一致的,分為三個(gè)部分:設(shè)置、加載、啟動(dòng)。

2022-10-10 14:37:57 1272

1272 芯片設(shè)計(jì)工程師根據(jù)功能,完成RTL設(shè)計(jì),添加各種約束,完成綜合、Place Route等一系列工作之后,還需要一些配置數(shù)據(jù),完成寄存器初始化等內(nèi)容,才能開始工作。 今天我們一起來(lái)聊一聊FPGA的配置

2022-11-21 21:45:10 955

955 FPGA 可編程的特性決定了其實(shí)現(xiàn)數(shù)字邏輯的結(jié)構(gòu)不能像專用 ASIC 那樣通過固定的邏輯門電路來(lái)完成,而只能采用一種可以重復(fù)配置的結(jié)構(gòu)來(lái)實(shí)現(xiàn), 而查找表(LUT)可以很好地滿足這一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工藝的查找表結(jié)構(gòu)。

2022-11-29 10:10:57 2833

2833 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置技術(shù),其主要優(yōu)點(diǎn)是系統(tǒng)設(shè)計(jì)更加簡(jiǎn)單、不需要外部存儲(chǔ)器和配置控制器、功耗低、成本低和FPGA配置時(shí)間更快。最大的缺點(diǎn)在于配置是固定的。

2022-12-01 11:08:45 862

862 ForgeFPGA 配置指南

2023-01-09 19:16:34 0

0 HDL 設(shè)計(jì) ? ? ? ? 具有非常高的資源利用率和頻率要求的設(shè)計(jì)要獲得可重復(fù)的結(jié)果是一件最具挑戰(zhàn)性的事情,但是它們也是最需要可重復(fù)結(jié)果的設(shè)計(jì)。獲得可重復(fù)結(jié)果的第一步是良好的設(shè)計(jì)實(shí)現(xiàn)(RTL

2023-02-09 03:05:02 434

434 ForgeFPGA 配置指南

2023-06-30 19:10:57 0

0 電子發(fā)燒友網(wǎng)站提供《基于ARM9平臺(tái)和FPGA的1553B總線測(cè)試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-11-08 10:10:29 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論