VHDL語言應用實例指導

VHDL中的標識符可以是常數、變量、信號、端口、子程序或參數的名字。使用標識符要遵守如下法則:

·標識符由字母(A…Z;a…z)、數字和下劃線字符組成。

·任何標識符必須以英文字母開頭。

·末字符不能為下劃線。

·不允許出現兩個連續下劃線。

·標識符中不區分大小寫字母。

·VHDL定義的保留子或稱關鍵字,不能用作標識符。

·VHDL中的注釋由兩個連續的短線(--)開始,直到行尾。

以下是非法標識符:

-Decoder????????—起始不能為非英文字母

3DOP??????????—起始不能為數字

Large#number???—“#”不能成為標識符的構成符號

Data__bus???????—不能有雙下劃線

Copper_?????????—最后字符不能為下劃線

On????????????—關鍵字不能用作標識符。???????????

注:在AHDL語言中標識符要區分大小寫,但在VHDL語言中不區分大小寫。所以寫程序時,一定要養成良好的書寫習慣,應用關鍵字時用大寫,自己定義的標識符用小寫。

標識符表示的幾種數據對象的詳細說明如下:

1)?常數(Constant?)

常數是一個固定的值,主要是為了使設計實體中的常數更容易閱讀和修改。常數一被賦值就不能在改變。一般格式:

CONSTANT?常數名:數據類型:=表達式;

??例:CONSTANT?Vcc:?REAL:?=5.0;

??????????????????—設計實體的電源電壓指定??

常數所賦得值應與定義的數據類型一致。

常量的使用范圍取決于它被定義的位置。程序包中定義的常量具有最大的全局化特性,可以用在調用此程序包的所有設計實體中;設計實體中某一結構體中定義的常量只能用于此結構體;結構體中某一單元定義的常量,如一個進程中,這個常量只能用在這一進程中。

2)?變量(Variable)

變量是一個局部變量,它只能在進程語句、函數語句和進程語句結構中使用。用作局部數據存儲。在仿真過程中。它不像信號那樣,到了規定的仿真時間才進行賦值,變量的賦值是立即生效的。變量常用在實現某種算法的賦值語句中。

一般格式:

VARIABLE?變量名??數據類型???約束條件:=表達式;

例:VARIABLE?x,y:INTEGER;??—定義x,y為整數變量

VARIABLE?count:??INTEGER?RANGE0?TO255:=10;??—定義計數變量范圍

變量的適用范圍僅限于定義了變量的進程或子程序中。若將變量用于進程之外,必須該值賦給一個相同的類型的信號,即進程之間傳遞數據靠的信號。

變量賦值語句的語法格式如下:

?????????????????????目標變量:=表達式;

變量賦值符號是“:=”。賦值語句右方的表達式必須是一個與目標變量有相同數據類型的數值。變量不能用于硬件連線和存儲元件。

3)?信號(Signal)

信號是描述硬件系統的基本數據對象,它類似于連接線,它除了沒有數據流動方向說明以外,其它性質與實體的端口(Port)概念一致。變量的值可以傳遞給信號,而信號的值不能傳遞給變量。信號通常在構造體、包集合和實體中說明。信號說明格式為:

SIGNAL?信號名:?數據類型;

信號初始值的設置不是必需的,而且初始值僅在VHDL的行為仿真中有效。

1.?變量

變量只能在進程、函數和過程中使用,一旦賦值立即生效。

例:VARIABLE??x,?y:?INTEGER;

???VARIABLE??count:?INTEGER?RANGE?0?TO?255:=10;

2.?信號

信號除了沒有方向的概念以外幾乎和端口概念一致。

例:SIGNAL?sys_clk:?BIT:=’0’;

???SIGNAL?ground:?BIT:=’0’

在程序中,信號值輸入信號時采用代入符”<=”,而不是賦值符“:=”,同時信號可以附加延時。

信號傳送語句:

???s1<=s2?AFTER?10ns

信號是一個全局量,可以用來進行進程之間的通信

3.?信號與變量的區別:

信號賦值可以有延遲時間,變量賦值無時間延遲;

信號除當前值外還有許多相關值,如歷史信息等,變量只有當前值;

進程對信號敏感,對變量不敏感;

信號可以是多個進程的全局信號,但變量只在定義它之后的順序域可見;

???信號可以看作硬件的一根連線,但變量無此對應關系。

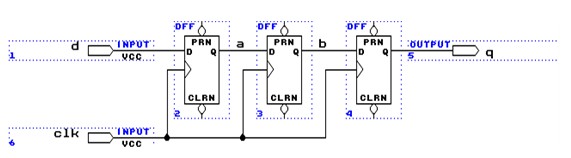

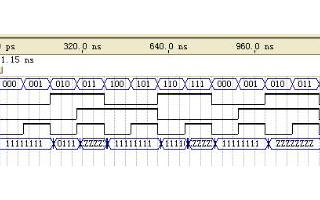

例:ENTITY?reg1?IS

PORT?(?d :?in?BIT;

clk :?in?BIT;

q :?out?BIT);

END?reg1;

ARCHITECTURE?reg1?OF?reg1?IS

SIGNAL?a,?b?:?BIT;

BEGIN

PROCESS?(clk)

BEGIN

IF?clk='1'?AND?clk’event??THEN

a?<=?d;

b?<=?a;

q?<=?b;

END?IF;

END?PROCESS;

END?reg1;

ENTITY?reg1?IS

PORT?(?d :?in?BIT;

clk :?in?BIT;

q :?out?BIT);

END?reg1;

ARCHITECTURE?reg1?OF?reg1?IS

BEGIN

PROCESS?(clk)

VARIABLE??a,?b?:?BIT;

BEGIN

IF?clk='1'?AND?clk’event?THEN

a?:=?d;

b?:=?a;

q?<=?b;

END?IF;

END?PROCESS;

END?reg1;

電子發燒友App

電子發燒友App

評論