視頻采集系統是數字圖像獲取的最基本手段,是進行數字圖像處理、多媒體和網絡傳輸的前提,它可為各種圖像處理算法提供待處理的原始數字圖像和算法驗證平臺。隨著圖像數字化處理技術的高速發展,對圖像采集的要求也越來越高,這包括對采集圖像的速度、主觀質量、靈活性等等的要求。針對這種發展的趨勢,設計了一種基于CPLD和DSP器件的多分辨率圖像采集處理系統,重點介紹了CPLD在采集過程中邏輯控制的靈活應用。

2?? 系統方案設計

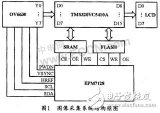

根據系統要求,采取了獨立采集法,采用專用圖像采集芯片自動完成圖像的采集,除了對采集模式進行設定外,處理器不參與采集過程,這種方法的特點是不占用CPU的時間、實時性好、適合活動圖像的采集。系統設計流程如下:DSP發開始采集指令,A./D開始采集,將A/D輸出的控制、狀態信號接入CPLD,由CPLD控制將轉換后的數字信號存儲到高速大容量SRAM(ODD和EVEN)中,直到一幀圖像數據存儲完畢后,其間CPLD產生SRAM地址、SRAM讀寫信號、中斷信號、總線切換信號等等;CPLD交出總線控制權,DSP占用總線從SRAM中讀出圖像數據進行處理。限于篇幅,本文重點介紹CPLD在數據采集中的靈活設計。系統結構如下圖所示:

圖1:系統結構框圖

3? 系統硬件設計

本系統DSP采用TI公司生產的54x系列中的TMS320VC5416,CPLD是ALTERA公司MAX7000系列中的EPM7128A。A/D芯片選用飛利浦公司出品的SAA7111A視頻A/D轉換芯片,這里利用DSP多通道緩沖串行口McBSP來模擬I2C總線時序對SAA7111A進行初始化。

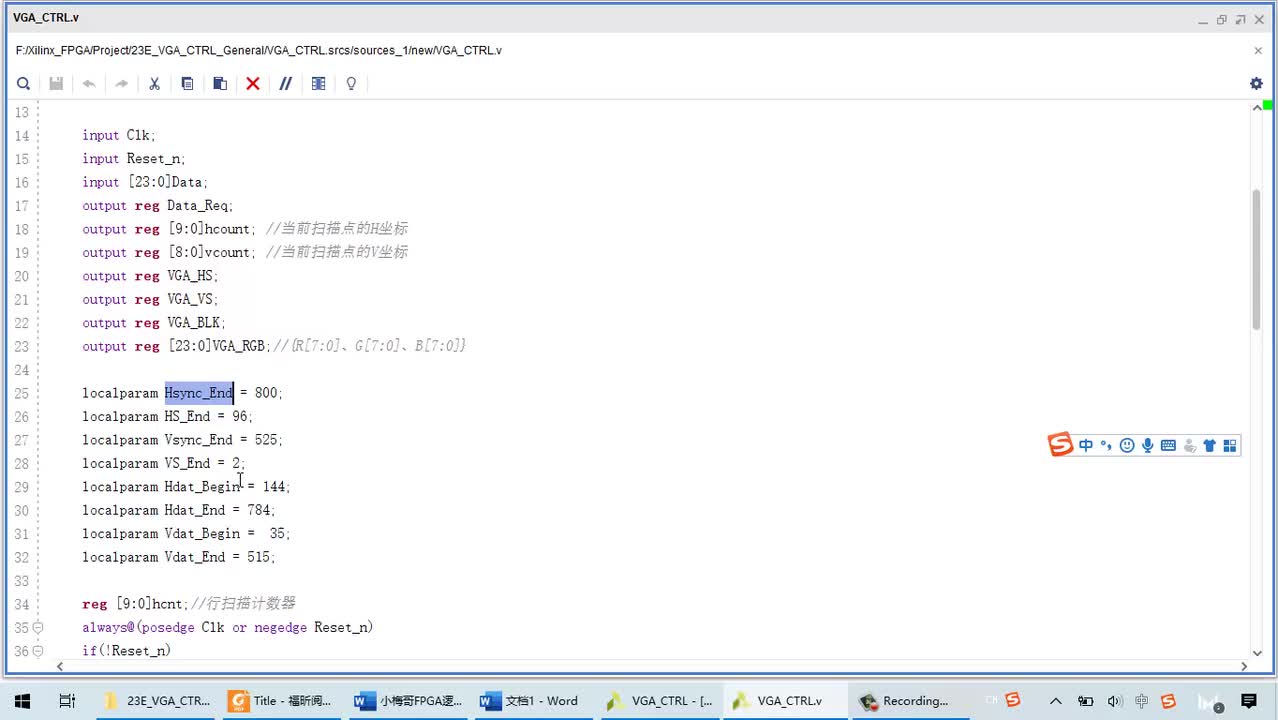

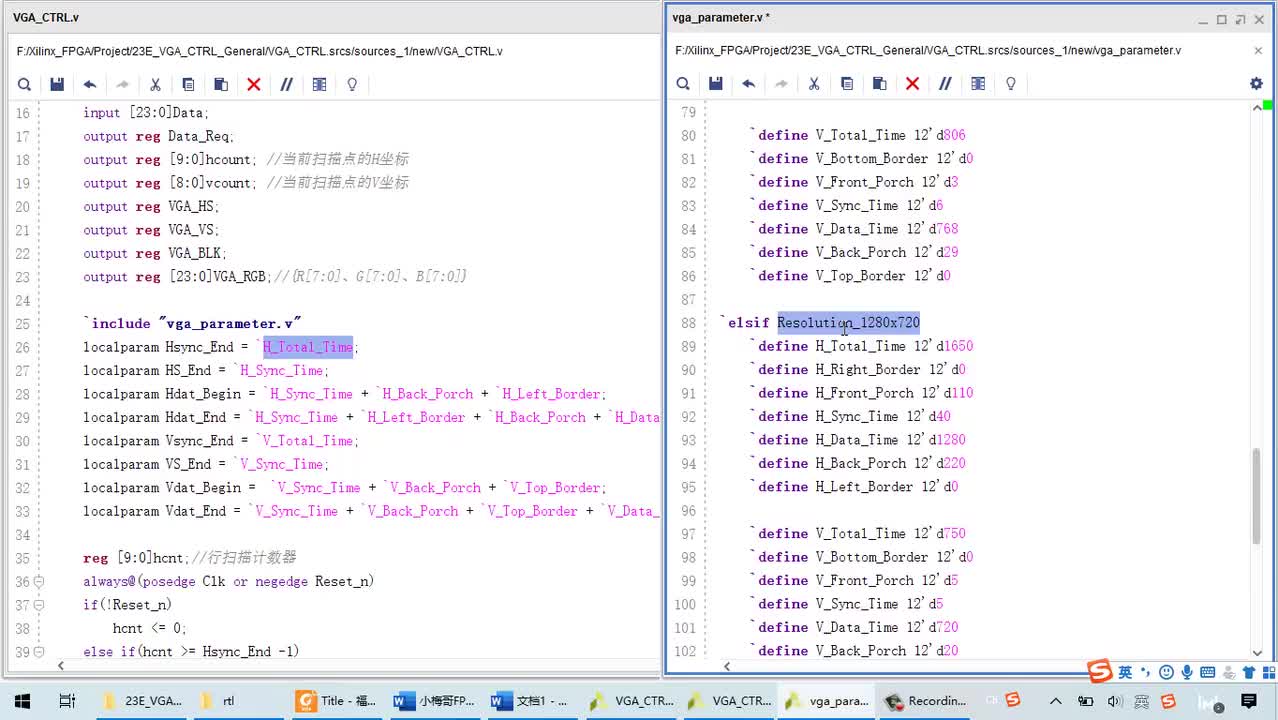

3.1? 數據采集的邏輯功能設計

本設計方案通過利用CPLD控制視頻采集芯片SAA7111A實現行、場數據延時[2],并分奇、偶場數據分離存放,DSP選擇讀取采集到的奇、偶場數據統一或分別進行處理,從而得到多分辨率圖像數據。將SAA7111A產生的控制信號和狀態信號與CPLD連接,即把垂直同步信號VREF、水平同步信號HREF、奇偶場標志信號RTS0、片選信號CE、場同步信號VS、象素同步信號LLC2等連接到CPLD上,CPLD通過這些控制和狀態信號進行譯碼和產生存儲地址等操作。垂直同步信號VREF的兩個正脈沖之間為掃描一幀(幀掃描方式)或一場(場掃描方式)的定時,即完整的一幀或一場圖像在兩個正脈沖之間掃描完。水平同步信號HREF為掃描該幀或該場圖像中各行象素的定時,即高電平時為掃描一行象素的有效時間。若當前圖像窗口大小為640×480,則在VREF兩個正脈沖之間有480個HREF的正脈沖,即480行;在每個HREF正脈沖期間有640個LLC2正脈沖,即每行640個象素,即VREF、HREF、LLC2這三個同步信號之間的關系。

為了體現本系統多分辨率的特點,需要改變SAA7111A的默認采樣分辨率,通過CPLD的邏輯控制就可以得到多分辨率圖像數據。本文選擇從默認分辨率720×625到設定分辨率640×480的采集,因此就需要進行、場延遲,舍棄部分像素。通過寫SAA7111A中I2C寄存器行同步開始寄存器(子地址06)和行同步結束寄存器(子地址07)可以直接控制行同步有效時間,因此可以省略行延遲電路設計,而場延遲是在CPLD中實現。

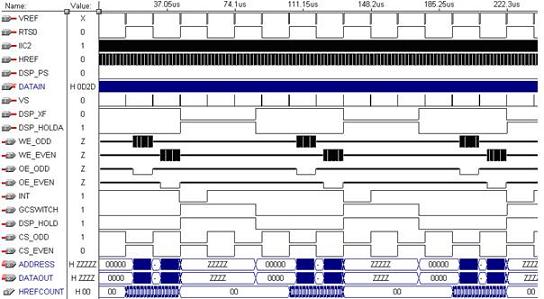

邏輯功能設計大體分為以下幾個部分:DSP與CPLD的總線切換邏輯;場延遲部分(HREF的下降沿進行計數器設計);LLC2控制的SRAM地址產生部分;SRAM片選信號、寫信號以及同步時鐘選擇時序控制部分。其中CPLD和DSP之間的總線管理是設計中的難點。圖像采集時序如下圖所示。

圖2:圖像采集時序圖

具體描述如下:置低DSP的XF引腳產生START采集啟動信號,它向CPLD發出圖像采集命令,當VS上升沿來臨時,如果RTS0為低電平,則表明是奇場即將到來,產生ODD高電平信號,對ODD取反再與DSP輸出的nPS相或后用作SRAM (ODD)的片選信號CS_ODD。在VREF上升沿時刻,啟動場延遲計數器,場延遲是在CPLD中實現的,從每幀625行到480行需要舍棄145行(奇、偶場各采集240行),在CPLD中利用行同步參考信號HREF進行計數器設計(HREF<240)。場延遲結束時,置高HREF145信號,有效圖像數據采集開始接受,當VREF出現下降沿時,置低HREF145信號,奇場圖像采集完成;如果RTS0為高電平,則表明偶場即將到來,產生EVEN高電平信號,對EVEN取反再與DSP輸出的nPS相或后用作SRAM (EVEN)的片選信號CS_EVEN,場延遲仍然利用行同步參考信號HREF進行計數器設計(HREF<240)來實現,場延遲結束時,置高HREF145信號,有效圖像數據采集開始接受,當VREF出現下降沿時,置低HREF145信號,偶場圖像采集完成。此外GCSWITCH信號作為CPLD選擇內部時鐘的控制信號,當GCSWITCH為高電平期間,表示CPLD獲取總線權,系統處于圖像采集階段,CPLD內部時鐘為LLC2;當GCSWITCH為低電平期間,表示DSP收回總線權,系統處于圖像處理階段,此時CPLD內部的時鐘信號為DSP輸出時鐘信號CLOCKOUT。奇、偶場圖像存儲器采用了ISSI公司的l0ns級256K×16高速SRAM,LLC2時鐘為13. 5MHz,即每個像素時鐘大約為74.1ns,每一個LLC2脈沖產生一次SRAM地址,相對于SRAM的10ns級的讀寫周期來說完全可以滿足要求。利用LLC2(約13.5MHz)時鐘進行寫邏輯時序控制設計如下圖所示:

圖3:RAM(ODD,EVEN)寫信號時序圖

同時要注意:如果在處理完一幀圖像后再采集下一幀時,圖像數據已經進入了偶場或奇場,此時若開放圖像采集,由于不是從圖像頭開始采集,所采圖像將不完全,因此需要確定圖像采集開始的基準。這里設計只在RTS0的上升沿才檢測圖像采集開始信號是否產生,這樣每幀圖像只在RTS0的上升沿才開始采集,即每次都從偶場開始,這樣就避免了圖像數據的混亂,保證圖像的開始基準。另外,由于存放圖像數據的SRAM(奇、偶場SRAM)地址是由CPLD控制產生的,那么如果將SAA7111A轉換輸出的VPO[15:0]直接存放在SRAM中,勢必就會影響數據、地址的同步,導致不同的數據寫入同一個地址,同一個數據寫入不同的地址,從而造成讀寫錯誤。因此,考慮將SAA7111A輸出的VPO[15:0]也作為CPLD的輸入信號,在CPLD里通過延時作同步處理后再連接到SRAM的數據線上,這樣就可以滿足時序要求使數據寫入正確的地址。

3.2? 總線邏輯切換設計

在前面提到了CPLD和DSP之間的總線切換管理是設計中的難點,在數據采集過程CPLD必須掌握總線控制權,切換到數據處理過程DSP必須掌握總線控制權。為了解決這個無縫切換問題,這里充分利用DSP的保持請求信號nHOLD和保持響應信號nHOLDA來協調總線切換[3]。

通過置DSP的XF引腳為低電平,告訴CPLD開始控制SAA7111A進行圖像采集。在DSP_XF連接到CPLD為高電平(DSP_XF初始狀態應該為低電平)時,CPLD產生DSP_ HOLD總線請求切換信號,該信號連接到DSP的nHOLD引腳請求DSP進入保持狀態,在3個機器周期后DSP做出響應:產生nHOLDA低電平信號到CPLD,而且外部數據總線、外部地址總線和控制總線都變成高阻態。此時DSP進入保持狀態,CPLD控制各總線操作;當一幀圖像采集、存儲完成后CPLD產生nINT中斷信號通知DSP開始處理處理數據,同時并置高DSP_ HOLD引腳使得DSP的nHOLD腳也置高,并通過對CPLD編程將CPLD與SRAM連接的各個外部數據總線、外部地址總線和控制總線都置成高阻態,而在nHOLD置高3個機器周期后DSP外部數據總線、外部地址總線和控制總線都脫離高阻態,DSP進入正常工作狀態,DSP置XF腳為高電平,收回總線控制權進行數據處理;

當DSP將處理后的一幀數據傳輸到上位機完成后,再次置低XF腳告訴CPLD可以開始采集下一幀了,CPLD產生DSP_ HOLD使DSP進入保持狀態,外部數據總線、外部地址總線和控制總線又都變成高阻態,CPLD掌握總線控制權。如此往復下去即可以解決DSP與圖像采集模塊的總線沖突問題,正確的切換總線邏輯保證了可以循環采集圖像進行處理。

3.3? CPLD邏輯功能仿真驗證

通過利用CPLD控制視頻A/D芯片SAA7111A的圖像采集過程,并利用SAA7111A的輸出狀態信號來控制CPLD實現圖像數據儲存、時序控制、地址譯碼等功能。這樣很好地協調了行、場參考及同步信號、像素時鐘、SRAM讀寫信號和DSP控制信號之間的時序關系,保證了對SRAM讀寫操作時各信號的時序配合,很好的解決了行、場延時問題,使圖像分辨率從720×625過渡到640×480,并且正確生成SRAM寫地址,DSP中斷信號以及總線切換信號的產生。

由于篇幅有限,故沒有列出VHDL具體代碼,現只給出仿真結果。仿真結果如下所示:

圖4:循環采集處理仿真圖

上面的循環采集處理仿真圖就是實際系統工作時采集模塊中各個信號的時序邏輯關系。從仿真圖可以看出通過對CPLD的編程實現了多點的行、場延時,奇偶場分離存放,從而得到多分辨率的圖像數據,以及DSP中斷產生、邏輯總線切換信號、下一幀的開始觸發信號、奇偶場對齊信號等都能滿足系統時序要求。采集一幀640×480的圖像約需22.75ms,可以滿足實時性的要求。

4? 結論

本文設計了一種基于CPLD的多分辨率圖像采集系統,本文作者創新點:提出一種由CPLD控制圖像的行、場信號延時,奇偶數據分離存儲來得到不同分辨率圖像數據的方法,實現了不占用DSP資源的多分辨率圖像的實時采集。經過大量仿真和電路板調試,證明該方案靈活有效,能夠在工業監測、醫療診斷等圖像實時采集領域得到廣泛應用。

參考文獻

[1] 周霖.? DSP通信工程技術應用 [M]. 北京:國防工業出版社,2003.

[2] 張駿. 基于DSP和CPLD的圖像通信系統設計與實現 [D]. 哈爾濱:哈爾濱工程大學碩士學位論文, 2004, 2.

[3] 趙龍寶, 范天翔, 陸亨立. 基于OV5017和CPLD的圖像采集顯示系統[J]. 微計算機信息, 2005, 21-7: 104-105.

電子發燒友App

電子發燒友App

評論