隨著 MCU 擴展到越來越多的功率受限設計,處理效率成為系統設計人員日益關注的問題。以更低的功率獲得額外處理能力的驅動力不僅在電池供電的產品中很重要,而且在許多“插入式”模塊中,功率也越來越受到模塊規格的限制。在這些情況下,一個高效的設計將能夠提供更多的功能,并相對于效率較低的實施創造競爭優勢。

MCU 設計中一個被忽視的方面是時鐘控制領域。設計人員通常可以通過使用時鐘控制模塊的高級功能來調整 CPU、外設和其他功耗資源的時鐘,從而創建更高效??的設計。本文將探討高級時鐘控制模塊的一些常見特性的功能,并展示它們如何在大多數基于 MCU 的設計中提高處理效率。

時鐘源

MCU 的整體操作由時鐘控制塊管理,許多時鐘控制塊具有可用于選擇、控制和管理 CPU、存儲器、外設和模擬塊的時鐘源的功能。通過控制這些模塊的時鐘,甚至關閉某些處理例程中未使用的功能的時鐘,電源可以僅在 MCU 的需要它的部分以及它們需要時提供,從而實現非常高效執行。時鐘管理和控制的起點是可供各種子模塊使用的各種時鐘源。了解每個時鐘源的優缺點是高效 MCU 實施的起點。

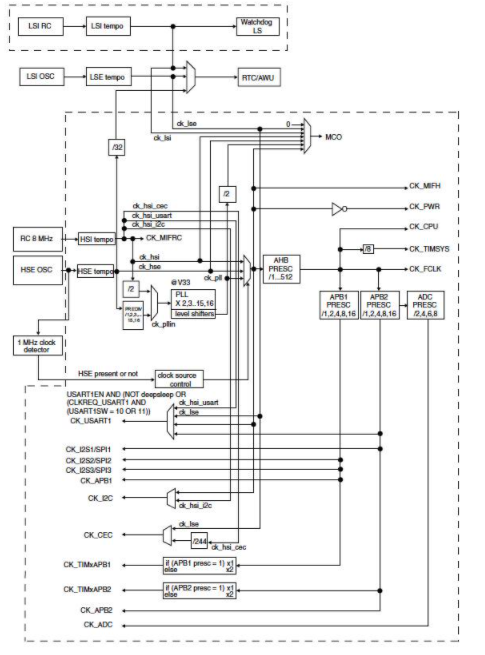

STMicroelectronics ST32F37xx 提供許多常見的時鐘源和控制功能MCU 時鐘控制模塊,如圖 1 所示。ST32F37xx 有多個時鐘源,每個時鐘源都有一個特定的功能,并針對它進行了優化。例如,高速外部 (HSE) 時鐘(如圖 1 左中所示)使用外部晶體/陶瓷諧振器或現有用戶提供的時鐘。外部晶體/陶瓷諧振器的工作頻率范圍為 4 至 32 MHz,并產生非常準確的主時鐘速率。如果現有的外部時鐘已經可用,或者如果用戶希望對時鐘源進行額外的控制(可能停止或減慢時鐘以進行更精細的低功耗操作控制),則可以使用外部時鐘輸入。這也釋放了一個額外的 GPIO 引腳,因為在實現諧振器時需要少一個引腳。

圖 1:STM32F37xx 時鐘控制模塊。(意法半導體提供)

高速內部 (HIS) 時鐘信號由內部 8 MHz RC 振蕩器生成,可直接用作系統時鐘或在被 PLL 使用之前進行二分頻。HIS RC 振蕩器的優點是可以低成本提供時鐘源,因為它不使用外部元件。它還具有比HSE晶振更快的啟動時間;然而,即使經過校準,頻率也不如外部晶體振蕩器或陶瓷諧振器準確。請注意,CPU 時鐘只能由高速時鐘之一或 PLL 的輸出驅動。

STM32F37xx 還有兩個低速時鐘源。低速外部 (LSE) 晶體/陶瓷振蕩器顯示在圖 1 的頂部,它使用高精度 32.768 kHz 諧振器為實時時鐘 (RTC) 外設創建精確的時鐘源。低速內部 RC 振蕩器提供 40 kHz 信號,用于驅動獨立的看門狗定時器和可選的 RTC,用于從低功耗停止/休眠模式自動喚醒。低功耗時鐘獨立于高速時鐘運行,因此即使主系統時鐘關閉,其外圍設備也可以運行,從而節省大量電力。

這些時鐘源是您可以在大多數 MCU 中找到的典型時鐘源。如圖 1 所示,時鐘源只是大多數 MCU 中時鐘架構的起點。通常可以進一步選擇、處理時鐘(通常使用一個或多個鎖相環或 PLL 塊),或在 MCU 控制下啟用所有時鐘。在下一節中,我們將通過查看 PLL 模塊的典型功能來繼續探索時鐘控制。

鎖相環操作

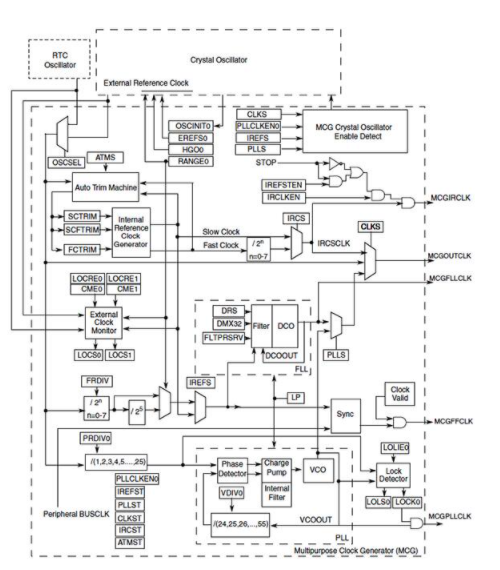

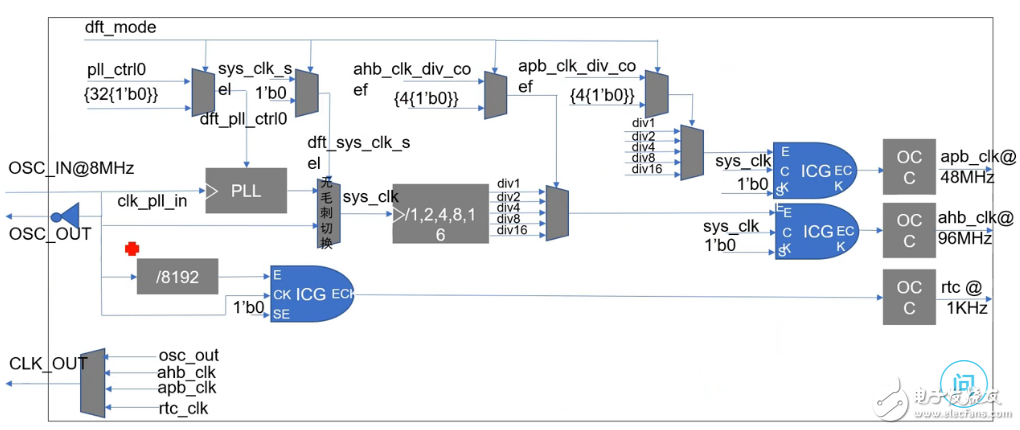

各種時鐘操作模塊,如鎖相環 (PLL) 和鎖頻環 (FLL) 模塊,是時鐘控制模塊中最重要但通常不太了解的元素。飛思卡爾Kinetis K10MCU 子系列具有多用途時鐘發生器 (MCG) 模塊,如圖 2 所示,其中包括 FLL 和 PLL,因此這是一個很好的示例。Kinetis K10 MCG FLL 可由內部或外部參考時鐘控制。PLL 可由外部參考時鐘控制。該模塊可以選擇 FLL 或 PLL 輸出時鐘或內部或外部參考時鐘作為 MCU 系統時鐘源。MCG 與晶體振蕩器一起工作,晶體振蕩器允許外部晶體、陶瓷諧振器或其他外部時鐘源產生外部參考時鐘。

圖 2:飛思卡爾 Kinetis K10 MCU 系列中的多用途時鐘發生器模塊。(由飛思卡爾提供)

FLL 模塊(如圖 2 中間所示)采用選定的時鐘源并對其進行操作以創建所需的時鐘頻率。輸入時鐘可以除以十六個不同的值,從 1 到 1536,以創建介于 31.25 kHz 到 39.0625 kHz 之間的基本頻率。然后將基頻與數控振蕩器 (DCO) 相乘,以產生介于 20 MHz 和 96 MHz 之間的所需輸出頻率。通過使用 FLL 從各種頻率中進行選擇的能力,可以輕松地將時鐘速率調整為特定操作模式所需的正確頻率,從而提高處理效率。PLL 以類似的方式工作,但使用壓控振蕩器 (VCO) 來調整時鐘輸出頻率。PLL 的輸入時鐘可以通過預分頻器進行 2 到 25 倍的分頻。相位檢測器將 PLL 輸入時鐘和 VCO 輸出時鐘相結合,將輸入信號乘以 24 到 55 倍。所有這些除法和乘法的結果是一個時鐘信號,它是應用所需的精確值。通常,PLL 比 FLL 需要額外的功率,但 PLL 具有更精細的調整和更高的精度。請注意,如果不需要 PLL 或 FLL 來生成應用所需的頻率,例如,在外部時鐘信號提供所需的確切頻率的情況下,可以禁用 PLL 或 FLL 以降低功耗。所有這些除法和乘法的結果是一個時鐘信號,它是應用程序所需的精確值。通常,PLL 比 FLL 需要額外的功率,但 PLL 具有更精細的調整和更高的精度。請注意,如果不需要 PLL 或 FLL 來生成應用所需的頻率,例如,在外部時鐘信號提供所需的確切頻率的情況下,可以禁用 PLL 或 FLL 以降低功耗。所有這些除法和乘法的結果是一個時鐘信號,它是應用程序所需的精確值。通常,PLL 比 FLL 需要額外的功率,但 PLL 具有更精細的調整和更高的精度。請注意,如果不需要 PLL 或 FLL 來生成應用所需的頻率,例如,在外部時鐘信號提供所需的確切頻率的情況下,可以禁用 PLL 或 FLL 以降低功耗。

外設時鐘控制

在使用 PLL 或 FLL 調整源時鐘(如果需要)后,時鐘分配網絡將負責為每個關鍵 MCU 模塊提供單獨的時鐘。CPU 及其相關的內存系統將需要自己的時鐘,但通常各種外圍設備也將擁有自己的時鐘。外圍時鐘網絡劃分得越細,就越容易單獨選擇和控制時鐘,并將工作頻率調整到應用所需的頻率。控制時鐘網絡的常用方法是添加時鐘分頻器電路(因為外設運行速度通常比 CPU 慢),如果根本不需要外設,甚至可以添加時鐘禁用電路。可用的控制越多,可以調整的功率和性能就越多,但在某些時候,必須考慮額外的裸片空間(及其相關成本)和所需的額外功率。制造商通常限制時鐘網絡提供完全的靈活性,但試圖為大多數應用提供足夠的能力以獲得顯著的功率和處理效率。

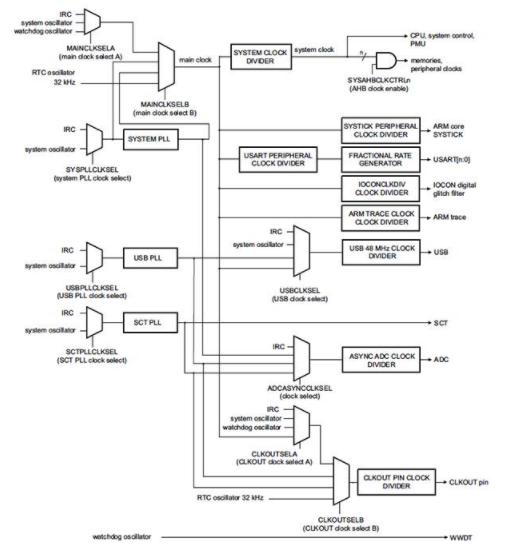

恩智浦,在其LPC15xx上MCU 已將每個關鍵外圍功能的時鐘分頻器按照非常實用的線進行分段,如圖 3 所示,從而可以輕松確定每個子塊使用哪些設置。例如,圖 3 中右側所示的 USART 模塊的時鐘信號來自主時鐘,但可以使用 USART 外設時鐘分頻器進行預分頻(從 1 到 255 或完全禁用) 。 然后,每個 USART 模塊內的各個小數波特率發生器(具有 16 位時鐘分頻值可用)可以使用該時鐘信號,以便輕松單獨設置每個 USART 的波特率。其他外設時鐘分頻器可在通用功能基礎上使用,以便于配置和控制性能,從而降低所有關鍵外設模塊的功耗。

圖 3:NXP LPC15xx MCU 上的外設時鐘分頻器。(恩智浦提供)

沿功能線對外設時鐘進行分組是一個簡單的概念,但是當外設??可以協同工作時,這個概念就變得更加復雜。例如,請注意 ADC 時鐘分頻器可以來自 SC Timer PLL。這似乎是一個不必要的連接,直到您意識到 ADC 可以與 SC 定時器一起工作以在沒有 CPU 干預的情況下進行周期性轉換。在創建所需操作所需的靈活性而不使時鐘控制塊因額外的復雜性而超載時額外注意,這是經過深思熟慮的實現的標志。

動態時鐘控制

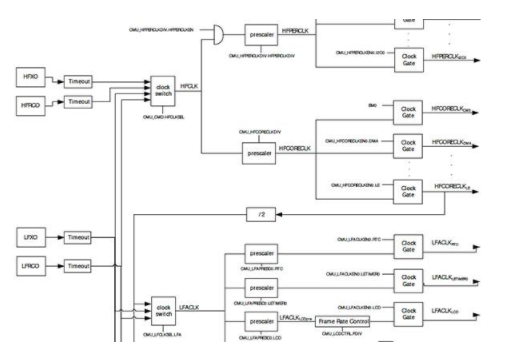

一旦您以最節能和處理效率最高的方式為各種外設選擇了時鐘,您可能會認為您已經完成了。為了獲得更高的性能和功率控制,您可能還需要根據 MCU 所處的功能或模式動態調整某些處理或外圍模塊的速度。靈活的時鐘選擇網絡是使用動態時鐘所需的關鍵特性。 Silicon Labs Gecko MCU的一部分圖 4 所示的時鐘控制模塊說明了這一點。圖中左上方的高頻時鐘開關可以選擇高頻時鐘(HFXO 或 HFRCO)或低頻時鐘(LFXO 或 LFRCO)。這使得根據設備運行的模式類型輕松“混合和匹配”低頻源或高頻源成為可能。

圖 4:Silicon Labs Gecko MCU 的時鐘控制模塊部分。(由 Silicon Labs 提供)

當進入和退出傳統低功耗模式需要太多“啟動”時間時,動態時鐘選擇最有用(即使是節能的 Gecko MCU 系列也可能需要 2 微秒的 EM2 低功耗喚醒時間)功耗狀態,在極低功耗 EM4 狀態下可達 160 μsec)。通過動態選擇低頻時鐘,節省的電量較少,但快速響應時間(通常僅在時鐘周期的數量級上)要快得多。這可以在捕獲異步事件或丟失它之間產生差異。當在操作狀態期間需要中等處理性能時,擁有這種級別的時鐘控制還可以增加低功耗狀態的使用。在您的設計中尋找動態時鐘控制機會,以實現最高的功率和處理效率水平。

總結

高級時鐘控制模塊提供了一些令人驚訝的功能,可以幫助管理 MCU 內的電源使用。控制外圍設備的時鐘、管理 CPU 的時鐘速率以及在處理過程中動態改變時鐘速率只是可用于創建更高效??設計的一些技術。

電子發燒友App

電子發燒友App

評論