本文提出了一種基于FPAG芯片的控制系統(tǒng)設(shè)計(jì)方案。系統(tǒng)中利用FPGA狀態(tài)機(jī)高效地控制ADC進(jìn)行信號(hào)采集。在FPGA中搭建的模糊控制器通過(guò)對(duì)勵(lì)磁電流的連續(xù)調(diào)節(jié),實(shí)現(xiàn)了恒速、恒轉(zhuǎn)矩和恒流

2011-09-30 14:55:08 2667

2667

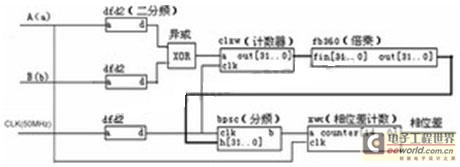

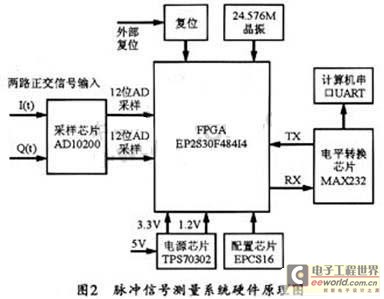

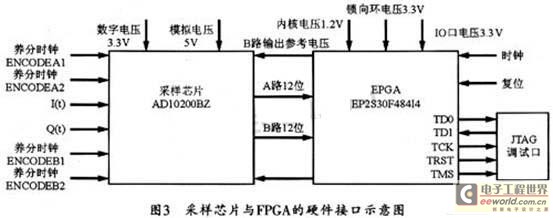

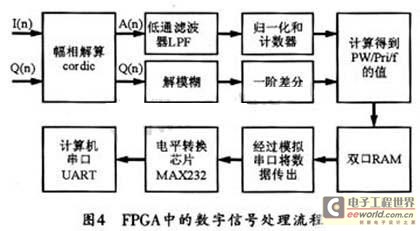

為了實(shí)現(xiàn)激光-水聲淺海地形遙感探測(cè)中水聲信號(hào)的實(shí)時(shí)解調(diào)與處理,本文提出了一種基于FPGA的激光多普勒測(cè)振計(jì)信號(hào)采集與處理系統(tǒng)的設(shè)計(jì)方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結(jié)合

2013-10-29 10:10:02 2157

2157

本文提出了一臺(tái)基于S12的簡(jiǎn)易便攜式數(shù)字示波器的設(shè)計(jì)方案,該設(shè)計(jì)方案中的數(shù)字示波器能對(duì)任意小于1MHz的波形進(jìn)行頻率和峰峰值的測(cè)量,且能夠?qū)Ρ粶y(cè)周期信號(hào)或單次非周期信號(hào)進(jìn)行單次采集與儲(chǔ)存,連續(xù)顯示。該設(shè)計(jì)方案中的以S12為主控單片機(jī),制作出的示波器不僅可以測(cè)量低頻的直流信號(hào),也可以測(cè)量高頻的交流信號(hào)。

2013-11-05 09:10:46 2665

2665

本文介紹了集中式插入法幀同步系統(tǒng)的原理,分析了幀同步系統(tǒng)的工作流程。采用模塊化的設(shè)計(jì)思想,利用VHDL設(shè)計(jì)了同步參數(shù)可靈活配置的幀同步系統(tǒng),闡述了關(guān)鍵部件的設(shè)計(jì)方法,提出了一種基于FPGA的幀同步系統(tǒng)設(shè)計(jì)方案。

2013-11-11 13:36:01 4359

4359

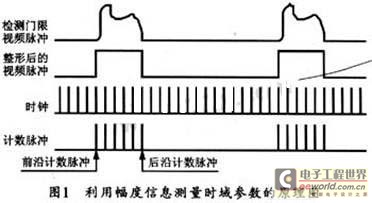

為了研究數(shù)字化γ能譜儀,本文提出一種基于FPGA的數(shù)字核脈沖分析器硬件設(shè)計(jì)方案,該方案采用現(xiàn)場(chǎng)可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計(jì)。用QuartusⅡ軟件在FPGA平臺(tái)上完成了數(shù)字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1947

1947

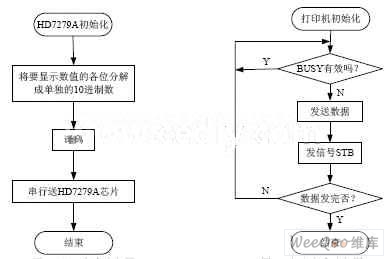

本文介紹了一種基于555定時(shí)器和單片機(jī)的數(shù)顯式電阻和電容測(cè)量系統(tǒng)設(shè)計(jì)方案。該系統(tǒng)利用555和待測(cè)電阻或電容組成多諧振蕩器,通過(guò)單片機(jī)測(cè)量555輸出信號(hào)的周期,根據(jù)周期與待測(cè)電阻或電容的數(shù)學(xué)關(guān)系計(jì)算出

2013-12-02 14:16:49 3485

3485

本文以X射線透射衰減規(guī)律為基礎(chǔ),提出了一種基于DSP的X射線能譜數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案。##經(jīng)過(guò)前置放大和帶通濾波處理后的信號(hào)仍然比較微弱,因此脈沖信號(hào)在送入ADC電路之前還需進(jìn)一步放大。

2014-01-08 11:56:49 2643

2643

不僅測(cè)量方便,而且具有經(jīng)濟(jì)、實(shí)用和便攜等優(yōu)勢(shì)。##發(fā)射端發(fā)射來(lái)的激光通過(guò)采樣空間由硅光電色敏二極管接收轉(zhuǎn)換成電信號(hào),通過(guò)NE5532可調(diào)放大電路放大至0~3.5 V范圍,送入單片機(jī)處理。##本文提出了一種易于操作且參數(shù)可變的透射式能見(jiàn)度測(cè)量裝置的設(shè)計(jì)方案,實(shí)現(xiàn)了對(duì)大氣能見(jiàn)度的分級(jí)檢測(cè)。

2014-01-16 11:02:18 1925

1925

本文以標(biāo)準(zhǔn)的I2C 總線協(xié)議為基礎(chǔ),提出了一種基于FPGA的I2C SLAVE 模式總線的設(shè)計(jì)方案。方案主要介紹了SLAVE 模式的特點(diǎn)。給出了設(shè)計(jì)的原理框圖和modelsim 下的行為仿真時(shí)序

2014-02-26 11:39:13 12336

12336 基于FPGA 的數(shù)字核脈沖分析器硬件設(shè)計(jì)方案,該方案采用現(xiàn)場(chǎng)可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計(jì)。

2015-02-03 09:55:05 1869

1869

FPGA典型設(shè)計(jì)方案精華匯總

2012-08-16 16:29:32

本帖最后由 csuly 于 2011-6-16 22:44 編輯

大俠你好! 菜鳥(niǎo)求助了。我需要檢測(cè)一個(gè)50Hz脈寬為20us的脈沖信號(hào)與一個(gè)15KHz脈寬為5us的脈沖信號(hào)。附件中的程序,我

2011-06-16 22:37:12

各位FPGA設(shè)計(jì)大賽參賽者注意了:小編這里幫大家解釋一下設(shè)計(jì)方案提交規(guī)則和活動(dòng)時(shí)間安排

自4月23日比賽開(kāi)始,參賽者報(bào)名之后即可提交設(shè)計(jì)方案。設(shè)計(jì)方案提交的截止日期是活動(dòng)結(jié)束,暨設(shè)計(jì)方案評(píng)選的最后

2012-05-04 10:27:46

本人想做一個(gè)陣列接收模塊,初步想法是FPGA+adc芯片,采集16Khz左右正弦信號(hào),得到其相位與幅度信息。如果要做64路,adc采用并行ad,這樣需要的IO口會(huì)很多,但如果不用一片fpga就不能同時(shí)采集信號(hào)。想問(wèn)一下有沒(méi)有什么好的解決方案呢?求大佬關(guān)注一下!!!謝謝!!!

2019-03-06 19:01:51

基于PCIE總線的脈沖采集方案-坤馳科技一、概述:為采集高速脈沖輸入信號(hào),并能實(shí)施將采集數(shù)據(jù)傳入PC主內(nèi)存,系統(tǒng)方案規(guī)格如下:1.采用12bit1Gsps高速ADC。2.50歐姆阻抗輸入。直流藕合

2016-08-15 14:59:39

在設(shè)計(jì)中想用上AD9254作為ADC,在設(shè)計(jì)過(guò)程中發(fā)現(xiàn)datasheet內(nèi)部提供了多種時(shí)鐘設(shè)計(jì)方案,由于設(shè)計(jì)的限制,想要省去所有方案中均推薦使用的AD951x芯片,請(qǐng)問(wèn)是否有曾經(jīng)使用過(guò)該款A(yù)D的同仁,使用直接從FPGA差分時(shí)鐘引腳引出的時(shí)鐘信號(hào),是否能夠滿足設(shè)計(jì)的要求?

2018-11-02 09:14:32

現(xiàn)在要做一個(gè)渦輪流量計(jì)脈沖輸出的測(cè)量電路,網(wǎng)上查了下 一般是小于等于0.8V為低電平 大于等于8V為高電平 請(qǐng)問(wèn)怎么設(shè)計(jì)電路才能用STM32來(lái)測(cè)量這個(gè)信號(hào)?就是說(shuō)怎么才能將這個(gè)電平轉(zhuǎn)換為與STM32兼容的電平信號(hào)?

2016-11-07 16:21:35

基于FPGA的簡(jiǎn)易DDS信號(hào)源設(shè)計(jì)設(shè)計(jì)方案背景信號(hào)發(fā)生器又稱(chēng)信號(hào)源或振蕩器,在生產(chǎn)實(shí)踐和科技領(lǐng)域中有著廣泛的應(yīng)用。能夠產(chǎn)生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱(chēng)為函數(shù)信號(hào)

2012-05-12 23:01:54

【推薦】雙脈沖測(cè)量解決方案 現(xiàn)在在越來(lái)越多的功率器件測(cè)量中比如場(chǎng)效應(yīng)晶體管(MOSFET)和絕緣門(mén)雙極晶體管(IGBT),這些功率器件提供了快速開(kāi)關(guān)速度,能夠耐受沒(méi)有規(guī)律的電壓峰值,被廣泛應(yīng)用于電源

2020-02-14 11:16:06

介紹一種包含千兆采樣率ADC的系統(tǒng)設(shè)計(jì)方案

2021-05-14 06:07:02

從ASIC到FPGA的轉(zhuǎn)換系統(tǒng)時(shí)鐘設(shè)計(jì)方案

2011-03-02 09:37:37

FPGA為平臺(tái)怎么測(cè)量脈沖寬度的verilog語(yǔ)言

2017-03-21 15:16:01

一種基于FPGA的簡(jiǎn)易頻譜分析儀設(shè)計(jì)方案,其優(yōu)點(diǎn)是成本低,性能指標(biāo)滿足教學(xué)實(shí)驗(yàn)所要求的檢測(cè)信號(hào)范圍。

2021-04-30 06:43:21

分享一款不錯(cuò)的采用FPGA的集群通信移動(dòng)終端設(shè)計(jì)方案

2021-05-25 06:32:04

本文以星載測(cè)控系統(tǒng)為背景,提出了一種基于 Actel Flash FPGA的高可靠設(shè)計(jì)方案。采用不易發(fā)生單粒子翻轉(zhuǎn)的 flash FPGA芯片,結(jié)合 FPGA內(nèi)部的改進(jìn)型三模冗余、分區(qū)設(shè)計(jì)和降級(jí)重構(gòu),實(shí)現(xiàn)了高實(shí)時(shí)、高可靠的系統(tǒng)。

2021-05-10 06:58:47

利用FPGA的無(wú)線通信收發(fā)模塊設(shè)計(jì)方案[hide][/hide]

2009-11-26 10:25:56

,乃至更高幅度的接口電平,通常為功率型電流驅(qū)動(dòng)信號(hào)。本文提出了一種兩級(jí)測(cè)試系統(tǒng)的設(shè)計(jì)思路,給出了在較寬的范圍內(nèi)兼容不同接口電平的脈沖信號(hào)檢測(cè)系統(tǒng)的設(shè)計(jì)方案,采用標(biāo)準(zhǔn)CPCI總線接口設(shè)計(jì),具有良好的兼容性

2012-09-01 16:09:40

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于FPGA及VHDL的LED點(diǎn)陣漢字滾動(dòng)顯示設(shè)計(jì)方案

2012-08-19 23:20:48

上學(xué)時(shí)做的變頻器設(shè)計(jì)方案,利用simulink仿真,基于FPGA的變頻器設(shè)計(jì)方案。

2014-09-10 10:40:12

基于FPGA的數(shù)據(jù)無(wú)阻塞交換設(shè)計(jì)方案,不看肯定后悔

2021-04-29 06:48:07

1 引言 在學(xué)習(xí)《電子線路》、《信號(hào)處理》等電子類(lèi)課程時(shí),高校學(xué)生只是從理論上理解真正的信號(hào)特征。不能真正了解或觀察測(cè)試某些信號(hào)。而幅頻特性和相頻特性是信號(hào)最基本的特征.這里提出了基于單片機(jī)和FPGA的頻率特性測(cè)試儀的設(shè)計(jì)方案,可使學(xué)生在實(shí)踐中真正觀察和測(cè)試信號(hào)的頻率特性。

2019-07-22 08:19:34

多種EDA工具的FPGA設(shè)計(jì)方案

2012-08-17 10:36:17

有沒(méi)有多通道(數(shù)量在100以上,也可能上千通道)ADC采樣的一個(gè)方案?目前能想到的方案(1)模擬信號(hào)先經(jīng)過(guò)數(shù)字開(kāi)關(guān),然后選通,再到ADC采樣口。(2)有沒(méi)有多通道ADC的cpu(類(lèi)似于fpga)的CPU?希望大家能給點(diǎn)建議。

2019-03-18 09:17:54

動(dòng)態(tài)相位對(duì)準(zhǔn)(DPA)電路和對(duì)新的外部存儲(chǔ)器接口的支持。AD芯片可以穩(wěn)定工作在100 MHz,FPGA速度可高達(dá)幾百M(fèi)Hz,故可保證系統(tǒng)的測(cè)量精度。那么有誰(shuí)知道如何利用ADC和FPGA設(shè)計(jì)脈沖信號(hào)測(cè)量嗎?

2019-07-31 06:25:45

如何用FPGA實(shí)現(xiàn)DVB碼流分析功能的嵌入式設(shè)計(jì)方案?

2021-04-28 06:19:10

“玩轉(zhuǎn)FPGA:iPad2,賽靈思開(kāi)發(fā)板等你拿”活動(dòng)持續(xù)火爆進(jìn)行中……………………活動(dòng)得到了廣大電子工程師積極強(qiáng)烈的支持,為了回報(bào)電子工程師和網(wǎng)站會(huì)員,現(xiàn)在只需提交fpga設(shè)計(jì)方案,就有機(jī)會(huì)獲得賽靈

2012-07-06 17:24:41

求一種便攜式RC測(cè)量儀的設(shè)計(jì)方案

2021-05-11 06:32:02

求一種基于FPGA的HDLC協(xié)議控制器設(shè)計(jì)方案

2021-04-30 06:53:06

求一種基于FPGA的永磁同步電機(jī)控制器的設(shè)計(jì)方案。

2021-05-08 07:02:07

求一種數(shù)字式溫度測(cè)量電路的設(shè)計(jì)方案

2021-05-17 06:16:41

本文主要提出一種集中式插入法幀同步的FPGA的設(shè)計(jì)方案。

2021-06-02 06:07:10

測(cè)溫系統(tǒng)設(shè)計(jì)方案,原理方案都有,有圖有真相!

2014-09-05 16:29:53

如圖所示,一個(gè)直流信號(hào)上疊加上脈沖信號(hào),波形的周期為6.25ms,脈沖信號(hào)共有40個(gè),占的周期是3.75ms,脈沖信號(hào)的占空比可以調(diào)節(jié)。如果測(cè)量這個(gè)波形的有效值。非電氣專(zhuān)業(yè),該向那個(gè)方向努力,求指點(diǎn)。

2016-12-06 17:02:56

一種基于ADC和FPGA脈沖信號(hào)測(cè)量系統(tǒng)的設(shè)計(jì)方案

2021-05-12 06:43:44

。分別測(cè)量每個(gè)電源,以便更好地了解當(dāng)一個(gè)交流信號(hào)施加于待測(cè)電源之上時(shí),ADC的動(dòng)態(tài)特性。開(kāi)始時(shí)使用一個(gè)高容值電容,例如100uF非極化電解質(zhì)電容。采用1mH的電感來(lái)充當(dāng)直流電源的交流阻斷器,一般將它稱(chēng)為

2018-09-30 16:31:56

在介紹了GPS 同步時(shí)鐘基本原理和FPGA 特點(diǎn)的基礎(chǔ)上,提出了一種基于FPGA 的GPS同步時(shí)鐘裝置的設(shè)計(jì)方案,實(shí)現(xiàn)了高精度同步時(shí)間信號(hào)和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40 當(dāng)今科技的發(fā)展,廣譜復(fù)合頻率電脈沖信號(hào)源得到越來(lái)越廣泛的應(yīng)用。通過(guò)對(duì)廣譜復(fù)合頻率電脈沖信號(hào)源的理論和特性分析,提供了對(duì)偽隨機(jī)廣譜復(fù)合頻率脈沖信號(hào)源設(shè)計(jì)方案。

2009-09-07 08:47:39 15

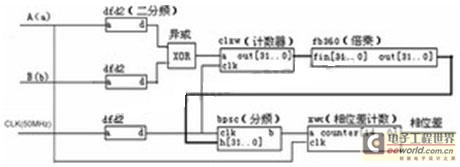

15 基于FPGA的高精度相位測(cè)量儀的設(shè)計(jì)方案

引言

隨著集成電路的發(fā)展,利用大規(guī)模集成電路來(lái)完成各種高速、高精度電子儀器的設(shè)計(jì)已經(jīng)成為一種行之有

2009-11-12 09:52:47 966

966

三選一的信號(hào)開(kāi)關(guān)設(shè)計(jì)方案

本設(shè)計(jì)實(shí)例使用一個(gè)單刀瞬時(shí)接觸開(kāi)關(guān),通過(guò)滾動(dòng)三個(gè)輸出態(tài)選擇三個(gè)信號(hào)源中的一個(gè)。圖1中的電路包括常用的CD4000&

2009-12-24 15:09:57 4633

4633

基于DSP處理器的光纖高溫測(cè)量儀的設(shè)計(jì)方案

摘要:介紹了一種基于DSP處理器的光纖高溫測(cè)量儀的設(shè)計(jì)方案。該測(cè)量儀以TMS320F2812芯片為核心,在硬件設(shè)計(jì)的基礎(chǔ)上,

2010-01-08 10:59:19 899

899

基于FPGA的光電抗干擾電路設(shè)計(jì)方案

光電靶的基本原理是:當(dāng)光幕內(nèi)的光通量發(fā)生足夠大的變化時(shí),光電傳感器會(huì)響應(yīng)這種變化而產(chǎn)生電信號(hào)。這就

2010-02-09 10:31:20 627

627

基于FPGA的高速定點(diǎn)FFT算法的設(shè)計(jì)方案

引 言 快速傅里葉變換(FFT)作為計(jì)算和分析工具,在眾多學(xué)科領(lǐng)域(如信號(hào)處理、圖像處理、生物信息學(xué)、計(jì)算物理

2010-02-09 10:47:50 992

992

多種EDA工具的FPGA設(shè)計(jì)方案

概述:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配

2010-05-25 17:56:59 670

670

示波器測(cè)量脈沖信號(hào)的擴(kuò)展思路為快沿脈沖信號(hào)測(cè)量提供了解決方案。解決,隨著傳輸速度的提升, 脈沖信號(hào) 的上升時(shí)間越來(lái)越短,上升沿覆蓋了更寬的頻譜范圍,需要更短的測(cè)量時(shí)間問(wèn)題

2011-07-25 10:58:39 34

34 電子發(fā)燒友網(wǎng)核心提示:本文提出了基于FPGA的噴油器脈寬處理的設(shè)計(jì)方案。在QuatusII自帶的仿真軟件下可以觀測(cè)到設(shè)置不同的脈寬控制參數(shù)可以達(dá)到輸出信號(hào)的占空比可調(diào)。整個(gè)系統(tǒng)下

2012-11-09 16:04:05 2287

2287 基于FPGA的ADC指標(biāo)測(cè)量及測(cè)試系統(tǒng)。

2016-05-10 11:47:13 13

13 該程序基于stc15單片機(jī),可測(cè)量脈沖信號(hào)的頻率,驅(qū)動(dòng)ads7822測(cè)信號(hào)幅度,并且配置da:tlv5616輸出電壓,設(shè)置窗口比較器的比較電平,配合fpga測(cè)量脈沖信號(hào)的上升沿下降沿時(shí)間,fpga部分的程序在另一個(gè)附件

2016-08-17 11:54:06 17

17 基于FPGA的OLED真彩色顯示設(shè)計(jì)方案

2017-01-18 20:35:09 25

25 數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 電子發(fā)燒友網(wǎng)站提供《基于FPGA的脈沖信號(hào)參數(shù)測(cè)量儀的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2017-05-27 08:00:00 82

82 FPGA及其外圍電路是整個(gè)測(cè)量系統(tǒng)的核心。外圍電路包括以下幾個(gè)部分:1)電源轉(zhuǎn)換電路,將5V電源轉(zhuǎn)換為FPGA工作必需的3.3 V及2.5 V電源;2)程序存儲(chǔ)器電路,負(fù)責(zé)存儲(chǔ)可執(zhí)行邏輯代碼

2018-02-17 03:02:00 2008

2008

脈沖信號(hào)是一種離散信號(hào),形狀多種多樣,與普通模擬信號(hào)(如正弦波)相比,波形之間在時(shí)間軸不連續(xù)(波形與波形之間有明顯的間隔)但具有一定的周期性是它的特點(diǎn)。最常見(jiàn)的脈沖波是矩形波(也就是方波)。脈沖信號(hào)

2018-04-28 11:18:26 59819

59819 基于FPGA的調(diào)焦電路設(shè)計(jì)方案資料下載

2018-05-07 15:53:08 9

9 本文首先介紹了脈沖信號(hào)測(cè)量工具,其次闡述了脈沖信號(hào)測(cè)量的步驟教程,最后介紹了用示波器測(cè)量脈沖信號(hào)的注意事項(xiàng)。

2018-08-21 17:45:19 35982

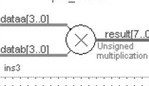

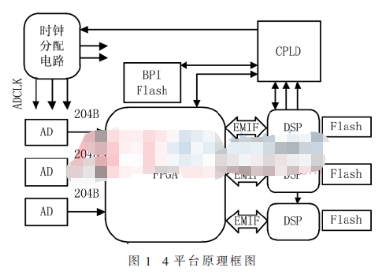

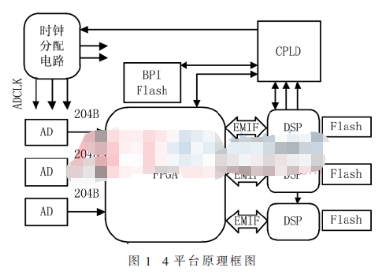

35982 新型多通道通用信號(hào)處理平臺(tái)主要包括高速AD芯片、Xilinx最新UltraScale系列FPGA和TI的多核DSP,原理框圖如圖1所示。其中FPGA和高速ADC之間數(shù)據(jù)傳輸采用JESD204B接口總線。

2020-07-16 09:25:16 2356

2356

用于精密測(cè)量和快速信號(hào)跟蹤的高精度SAR ADC

2021-05-18 09:11:46 7

7 AN-1494:使用AD7982差分脈沖星ADC轉(zhuǎn)換單端信號(hào)

2021-05-27 17:35:28 9

9 基于FPGA的二進(jìn)制相移鍵控設(shè)計(jì)方案

2021-05-28 09:36:50 11

11 為研究脈沖星X射線輻射脈沖信號(hào)的特點(diǎn)需要記錄X射線脈沖信號(hào)的上升沿時(shí)刻與脈沖信號(hào)峰值。設(shè)計(jì)了基于FPGA的X射線脈沖信號(hào)數(shù)據(jù)采集系統(tǒng)。重點(diǎn)介紹了數(shù)據(jù)采集系統(tǒng)的組成、功能及硬件設(shè)計(jì)。其中,系統(tǒng)采用11

2021-06-01 09:37:44 13

13 基于FPGA的嵌入式信號(hào)處理系統(tǒng)設(shè)計(jì)方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號(hào)處理系統(tǒng)設(shè)計(jì)方案

2021-06-02 11:04:33 0

0 基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

2021-06-17 09:37:02 21

21 基于FPGA的偽隨機(jī)數(shù)發(fā)生器設(shè)計(jì)方案

2021-06-28 14:36:49 4

4 小信號(hào)放大電路設(shè)計(jì)方案匯總

2021-09-14 15:01:12 127

127 如何用示波器去測(cè)量脈沖信號(hào)以及測(cè)量脈沖信號(hào)對(duì)示波器有什么要求。

2021-10-04 08:49:00 14201

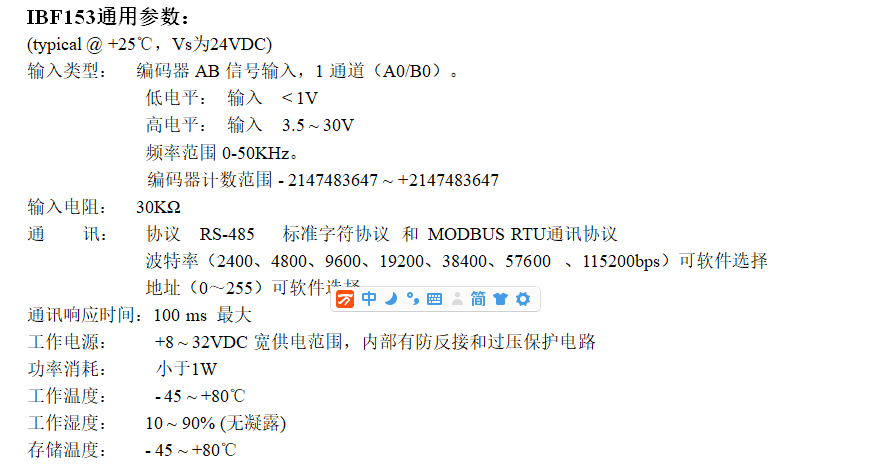

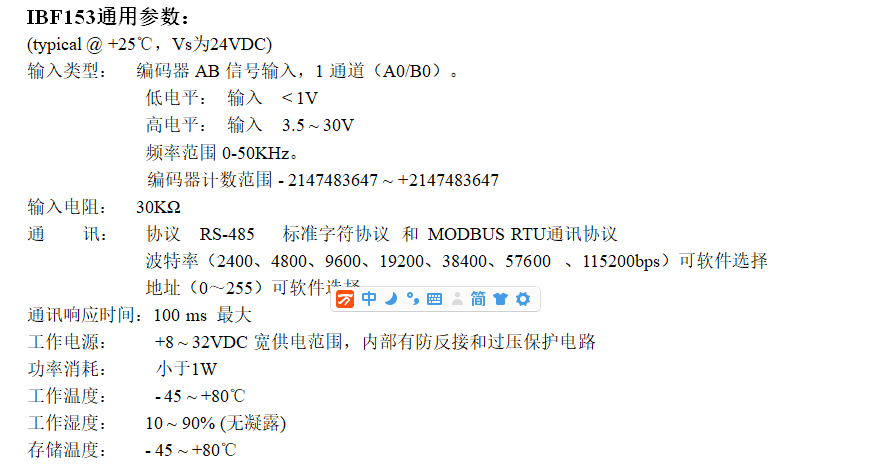

14201 ● 光柵尺脈沖信號(hào)測(cè)量

● 磁柵尺脈沖信號(hào)測(cè)量

● 三坐標(biāo)系統(tǒng)位置測(cè)量

● 球柵尺脈沖信號(hào)測(cè)量

2022-11-26 14:25:06 554

554

● 編碼器脈沖信號(hào)測(cè)量

● 流量計(jì)脈沖計(jì)數(shù)或流量測(cè)量

● 生產(chǎn)線產(chǎn)品計(jì)數(shù)

● 物流包裹數(shù)量

2022-11-28 13:58:35 429

429

本文詳細(xì)描述了FPGA實(shí)現(xiàn)圖像去霧的實(shí)現(xiàn)設(shè)計(jì)方案,采用暗通道先驗(yàn)算法實(shí)現(xiàn),并利用verilog并行執(zhí)行的特點(diǎn)對(duì)算法進(jìn)行了加速;

2023-06-05 17:01:45 862

862

電子發(fā)燒友網(wǎng)站提供《基于FPGA的PCI硬件加解密卡的設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-10-18 11:18:03 0

0 電子發(fā)燒友網(wǎng)站提供《簡(jiǎn)易信號(hào)發(fā)生器設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-10-20 09:43:18 0

0 電子發(fā)燒友網(wǎng)站提供《基于CPLD/FPGA的多串口擴(kuò)展設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-10-27 09:45:17 2

2 電子發(fā)燒友網(wǎng)站提供《高速ADC電源設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-11-10 16:20:26 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論