?

?

?

為實現高速電容耦合器件(CCD)數字圖像采集傳輸,提出一種基于PXIE總線和Camera Link協議的高速圖像采集系統設計方案。設計了Camera Link硬件接口電路,實現了視頻數據信號的接口設計、控制信號的接口設計、串行通信信號接口設計;同時采用Xilinx公司的Vir-tex-5 LX50T型FPGA作為PXIE傳輸控制器,并對IP核進行了開發,減少了外圍電路設計難度。創新性地運用直接內存訪問的工作方式對PXIE傳輸速度進行優化。實驗結果表明,PXIE配置為8通道時,讀取數據速率達到1 504 MB/s,寫入速率達到了1 490 MB/s,可以滿足高速CCD數據的傳輸要求。

電容耦合器件(Charge Coupled Device,CCD),是20世紀70年代初發展起來的新型半導體光電成像器件。由于其具有信號輸出噪聲低、動態范圍大、量子效率和電荷轉移效率高等特點,加之多年來新型半導體材料技術的不斷積累和大規模集成技術的日臻完善,CCD技術目前廣泛應用于國民經濟、國防建設、科學研究等各個領域。隨著上述領域對數字圖像的分辨率以及傳輸速度的要求越來越高,人們對高速圖像采集系統的性能、穩定性和可靠性也提出了新的要求。本文提出了一種基于PXIE總線和Camera Link協議的高速CCD圖像采集系統設計方案,并詳細說明了部分模塊的具體實現方式。

1 系統工作原理及總體設計

1.1 Camera Link協議及PXIE協議介紹

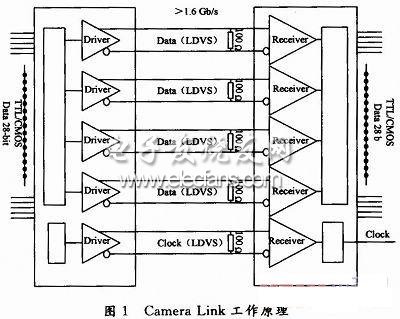

(1)Camera Link協議簡介

Camera Link是一種基于視頻應用發展而來的通信接口。它是NI等13家公司基于Channel Link技術聯合推出的一種新型接口,簡化了相機與其他設備的連接。Camera Link的驅動端將28位并行數據以7:1方式轉化為4組LVDS數據流和1組LVDS時鐘信號,串行發送至接收端進行處理。其最高傳輸速率可達2.38 Gb/s。圖1為Camera Link工作原理圖。

?

Camera Link接口協議提供4類信號:相機控制信號、圖像數據信號、電源和串行通信信號。其接口有3種結構,分別是初級配置(Base)、中級配置(Medium)和高級配置(Full)。Camera Link使用端口定義來區分這些配置。3M 26-pin MDR(Mini D Ribbon)連接器之所以被選擇與Camera Link配套使用是因為它優秀的設計和先前Channel Link高速傳輸的成功經驗。

(2)PXIE協議簡介

PXI(PCI Express for Instrumentation)由NI公司于1997年率先提出。PXIE基于Compact PCI標準,增加了時鐘和同步觸發總線,但其核心仍然是PCI總線。PXI Express相對PXI最顯著的改進和優勢就在于它融入PCI Express的特點,采用串行傳輸,點到點的總線拓撲結構。不同于PXI在所有總線設備間分享帶寬,PXI Express為每一個設備提供單獨的傳輸通道。同時它所增加的時鐘和同步觸發信號以及擁有特殊的接口物理特性使得其在測量、通信、工業自動化等領域擁有更大的技術優勢。本文采用PXIE-8x,最高傳輸速度達到1400Mb/s。

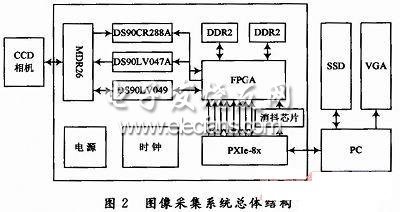

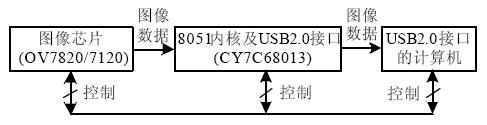

1.2 總體設計

系統總體結構圖,如圖2所示。

?

圖2中,DS90CR288A為NI公司高性能串并轉換器,將Camera Link接口協議的4路LVDS信號和1路LVDS時鐘轉換為28位LVCMOS/LVTTL數據和一路時鐘信號,DS90LV047A為NI公司的3 VLVDS 4路單端轉差分驅動器。DS90LV049為NI公司的3V LVDS雙向線路驅動器和雙向線路接收器。

系統工作流程為:

首先,采集卡通過DS90LV047A對CCD相機發出的控制指令。CCD相機在接到指令后,將采集到的圖像數據分為4路LVDS數據信號和1路LVDS時鐘信號,通過接口連接器MDR26,輸送到圖像采集卡;圖像采集卡將串行數據轉換成38路并行信號和1路隨路時鐘傳送給FPGA進行數據處理。由于數據量很大,為保證數據低誤碼率及提高可靠性,使用了2塊Micron 2 GB DDR2對數據進行緩存和乒乓處理。FPGA根據用戶的需求進行高速的圖像處理。采集卡通過PXIE-8x將圖像數據上傳至PC(上位機)上進行后期處理,同時實現PC(上位機)對圖像采集卡的控制。圖像數據最終通過PC將數據存儲在SSD(Solid-state Drive)電子盤上,以供隨時調用。在讀/寫速度等關鍵性能上,SSD電子盤遠遠優于傳統機械硬盤,因此選用SSD電子盤為數據存儲介質。采集卡還采用DS90LV049(LVDS雙線路驅動器,帶有雙線路接收器)來實現采集卡與相機間的串行通信,用戶可以根據需要對CCD相機進行配置。

2 關鍵模塊設計

2.1 Camera Link接口設計

根據系統功能要求,Camera Link接口設計包括3個部分,即為視頻數據信號接口設計,控制信號接口設計,串行通信命令接口設計。

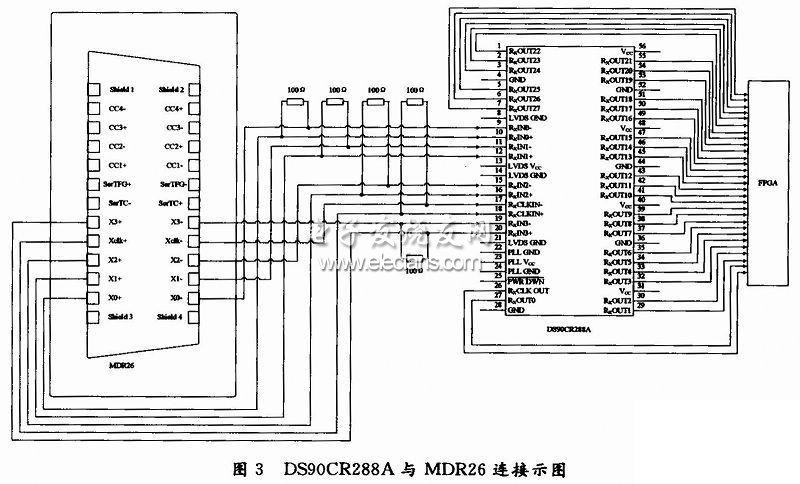

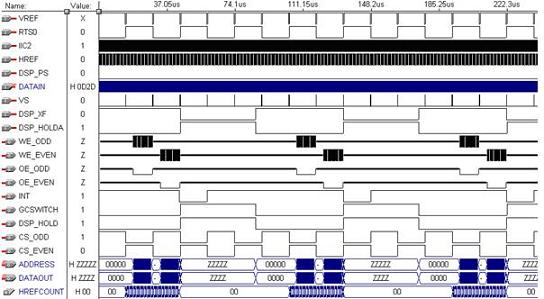

2.1.1 視頻數據信號的接口設計

視頻數據信號為FVAI,LVAL,DVAL和SP,它們分別是幀允許信號、行允許信號、數據允許信號和保留信號,4路均為LVDS數據信號,外加1對LVDS時鐘信號,在此采用了National Semiconductor公司的DS90CR288A芯片,將5路LVDS信號轉換為28路數據信號。具體連接圖如圖3所示。

?

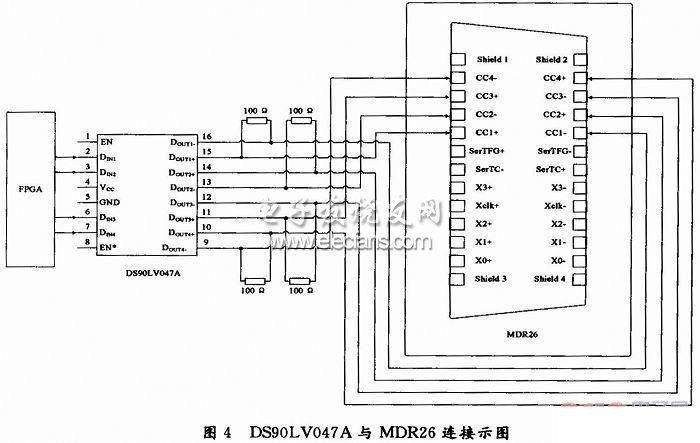

2.1.2 控制信號接口設計

相機控制信號CC1,CC2,CC3,CC4為4路LVDS信號,為節省布線空間,FPGA發出的控制信號均為單端信號,因此采用National Semicon-ductor公司的DS90LV047A芯片將采集卡發出的單端COMS控制信號轉化為LVDS信號,完成對CCD相機的控制。圖4為DS90LV047A與MDR26的連接。

?

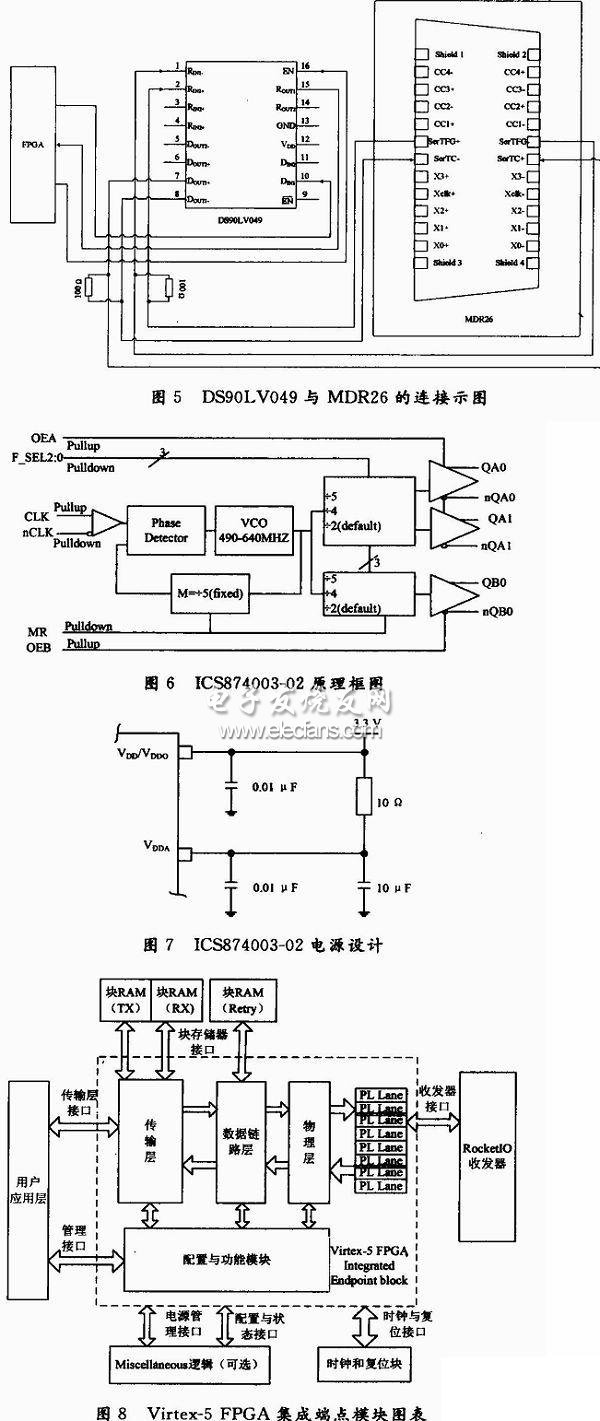

2.1.3 串行通信信號接口設計

串行通信信號由兩對LVDS信號提供,這些信號使相機與其使用者之間可以進行通信。因為是雙向通信,在此采用了National Semicon-ductor公司的DS90LV049芯片實現了LVDS差分信號到單端CMOS信號的雙向轉換。圖5為DS90LV049與MDR26的連接示圖。圖中EN為1時,EN可以不接,4條通路可以全通。

?

2.2 PXIE模塊設計

2.2.1 PXIE的時鐘電路設計

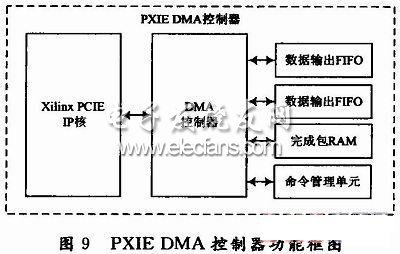

在PXIE規范中,對于時鐘的頻率穩定度要求是100 MHz±300 ppm,抖動(Cycle-to-Cycle)需要小于125 ps,占空比要求50%±5%以內。因此,系統中選用IDT公司的ICS874003-02作為100 MHz參考時鐘的抖動衰減器。ICS874003-02是一款高性能的將差分時鐘轉換為LVDS電平時鐘信號的時鐘抖動衰減器,該元件可支持PXI Express系統,具有衰減或“清除”100 MHz PXIE輸入時鐘抖動,同時將其轉換成250 MHz LVDS輸出能力的時鐘器件。ICS874003-02在芯片內部集成了一個高性能,低相噪的鎖相環。鎖相環的鑒相帶寬為400 kHz,可以快速鎖定時鐘,減小抖動。該器件支持低于1 ps RMS極低相位噪聲的基準時鐘生成,滿足基于PXIE的高速應用的嚴格的抖動要求。它的最大周期抖動為35 ps,占空比變化為50%±2%,完全可以滿足PXIE對時鐘的要求,其內部原理圖如圖6所示。

該系統設計中采用QA0/nQA0和QA1/nQA1兩對差分輸出時鐘,并且將這兩個輸出分頻器的分頻系數設置為5,使輸出時鐘頻率和輸入時鐘頻率相同。

ICS874003-02提供獨立的電源用以隔離內部鎖相環產生的開關噪聲,VDD,VDDA,以及VDDO抑必須單獨通過過孔連接到電源層,并且在每個電源腳上都要加入旁路電容,為了獲得最佳的時鐘抖動特性,電源需要相互隔離。如圖7所示,1個10 Ω的電阻以及1個10 μF和0.01 μF的旁路電容構成了一個電源濾波電路,連接到每個VDDA腳,10 Ω的電阻可以被磁珠所替代。

2.2.2 PXIE的IP core設計

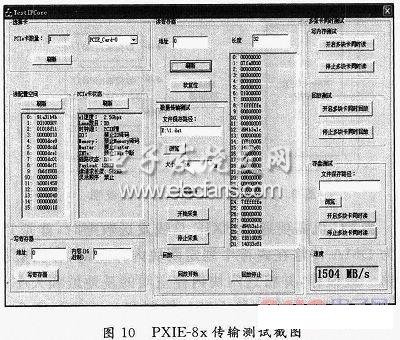

該系統中,采用Virtex-5LX50T型FPGA作為PXIE的傳輸控制器,由于FPGA內部集成了PCIe端點模塊,所以減少了很多外圍硬件電路的設計難度。PCIe端點模塊的IP核框圖如圖8所示。

由圖8可以看出,PXIE IP核采用分層結構,即分別為物理層鏈路模塊、物理層、數據鏈路層、傳輸層和用戶應用層。傳輸層負責處理用戶應用層(User Applieation)提供的傳輸層包(TLP)并安排其傳輸。數據鏈路層負責鏈路管理和數據完整性,包括錯誤的檢測和糾正。物理層負責完成包的成幀和解幀、字節的組合和拆分、鏈路的初始化和訓練、擾碼生成和解擾。發送時,物理層鏈路模塊負責將物理層生成的擾碼應用到傳輸數據中,同時復用到物理層模塊接收到的有序集中,最后把包傳輸給傳輸接口;接收時,負責從傳輸接口上接收TLP字節,從數據中解碼有序集,并且將DLLP和TLP解擾。

2.2.3 PXIE傳輸速度問題及解決情況

由于PXIE傳輸協議是基于PCIe傳輸協議的擴展,所以可以利用目前比較成熟的PCIe傳輸協議實現技術在硬件程序設計層次上實現PXIE傳輸協議,至于PXIE協議的一些擴展接口,都可以在FPGA外圍用基本硬件電路簡易的實現。FPGA生產廠商Xilinx公司提供了一套成熟,穩定并且免費的PCIe傳輸方案,以IP(Intellectual Property)的形式提供給用戶。

PCIe IP核雖然為PXIE傳輸協議提供了解決方案,但是仍然存在問題。首先,在實際測試過程當中,由于PCIe IP一直占用了CPU,使得PC在進行數據傳輸時,主機本身無法進行其他操作,還有一定幾率造成系統崩潰。其次,由于PCIe協議進行傳輸的包載荷過小,在進行大數據量傳輸的時候,會進行多次傳輸,從而浪費大量時間在結束和發起傳輸上,導致平均數據傳輸率下降。最后,由于IP核的重要特性是通用化,所以IP核的接口包括了所有PCIe信號,使得用戶操作非常繁瑣,不利于設計的移交和修改。直接內存訪問(Direct Memory Access,DMA)控制器能夠從根本上解決前兩個問題,經過優化設計也能改善第三個問題。

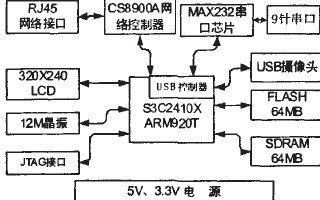

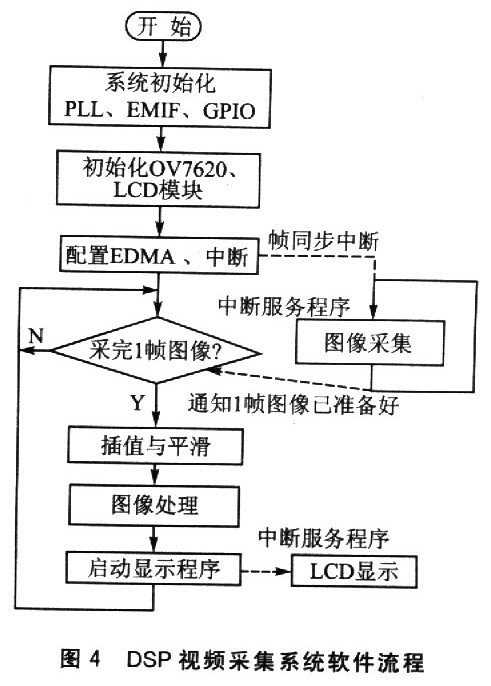

PXIE總線DMA的FPGA功能設計框圖如圖9所示。

?

當PC機需要通過PXIE總線發送數據時,首先PC機為DMA傳輸在內存中劃定兩塊內存空間,作為數據的第一級緩存,并將這兩塊內存空間的基地址和大小輪流通過PXIE總線傳給DMA控制器。這些配置命令通過特定的字符串被識別,并寫入相應的配置命令寄存器。劃定兩塊內存空間是為了在當DMA控制器從一塊內存中讀取數據時,PC機可以向另一塊內存寫入數據,以乒乓操作的形式提高傳輸效率。

接下來,PC機發起對數據的傳輸。PC機上的PCIe控制器從內存中取得數據后,將原始數據封裝,并串轉換往下繼續傳輸,數據包通過吉比特串行收發器傳至FPGA,在進入PCIe IP核后被拆解,剝離的糾錯信息作為包進一步處理的依據,最后在應用層以并行數據的形式推入DMA控制器。

DMA控制器將數據流存人數據輸出FIFO,根據FIFO剩余空間的大小判定是否從PC機中繼續讀取數據,這樣就保證了數據不會因為來不及從FIFO中取走而丟失。當DMA控制器接收到一塊內存大小的數據之后,就會以邊帶信號的形式發送中斷信號給上位機,上位機接收到中斷之后就可以開始下1次DMA傳輸。

當PC機需要通過PXIE總線接收數據時,工作流程與通過PXIE總線發送數據基本類似,主要區別在于從PC機往下發送的包里不包含數據,僅包含路由及其他控制信息,DMA控制器接收到包后,會以完成包的形式將數據打包往上傳回PC機,完成包按照接收到包中的路由信息,逆向尋址回到PC機的內存,PC機就完成了一次通過PXIE總線接收數據。

加入DMA控制器之后的PXIE總線被重新封裝,操作得到簡化。

2.3 測試結果

在測試中,PXIE配置為8通道,測試數據為16 MB,在PC機通過PXIE接口讀取數據的操作過程當中,平均數據率達到1 504 Mb/s。在PC機通過PXIE接口發送數據的操作過程中,平均數據率達到1 490 Mb/s。通過PCIe測速軟件進行傳輸速度測試,其結果如圖10所示。

?

3 結語

本文介紹了一種基于PXIE總線和Camera Link協議的高速CCD圖像采集系統的設計方案。該方案給出了一種Camera Link硬件接口電路的設計思路,并且選用Xilinx公司的Virtex-5 LX50T型FPGA作為整個采集系統的核心處理器,同時對Virtex-5自帶的IPcore進行研究和開發,實現Camera Link采集卡通過PXIE總線與上位機進行串行通信。在試驗過程中,FPGA設計靈活,開發周期短的優點充分得以體現,為下一步的高速圖像采集系統的研制奠定了基礎。

電子發燒友App

電子發燒友App

評論