靜態時序分析是檢查IC系統時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關,有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產品的開發周期

2020-11-25 11:03:09 8918

8918

路徑分析問題作一介紹: 1、時鐘網絡分析 時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 時序分析是FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-10-21 09:28:58 1283

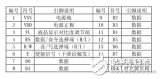

1283 使用SDC命令create_clock創建時鐘,時鐘周期20,占空比50%的時鐘信號;

2022-11-08 09:12:02 5409

5409 同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。

2023-06-28 09:35:37 490

490

特權老師,您好,關于時序分析-尋找PLL相移值,有些問題想請教您:疑問一:在您的《特權和你一起學NIOS II》書中,第五章,5.4 三部曲-時序報告,5.4.1 尋找PLL相移值,第102頁,書中

2013-10-22 22:26:12

前言小梅哥FPGA時序分析和約束實例演練FPGA的基本原理FPGA基本結構Field-Programmable Gate Array現場-可編程 門 陣列現場可編程通過JTAG、AS、PS等方式

2021-07-26 07:52:42

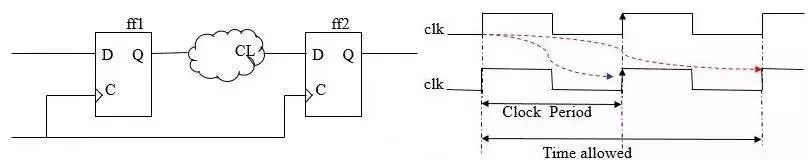

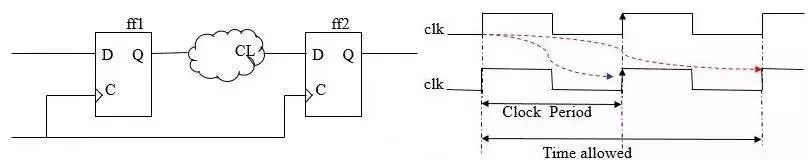

1。時序分析就是分析前級的數據是否在后一個時鐘沿的數據有效窗口里面,就是說在整個窗口內部,數據都應該保持有效,如果不滿足時間窗的前端,就是setup違例,如果不滿足時間窗的后端,那么就是hold違例

2014-12-29 14:53:00

此版只討論時序約束約束理論約束方法約束結果時鐘約束(Clock Specification): 約束所有時鐘(包括你的設計中特有的時鐘)對準確的時序分析結果而言是必不可少的。Quartus II

2013-05-16 18:51:50

不需要確定時序,不進行分析的路徑。set_false_path -from [get_port reset] -to[all_register] set_false_path -from

2018-09-21 12:55:34

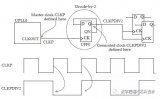

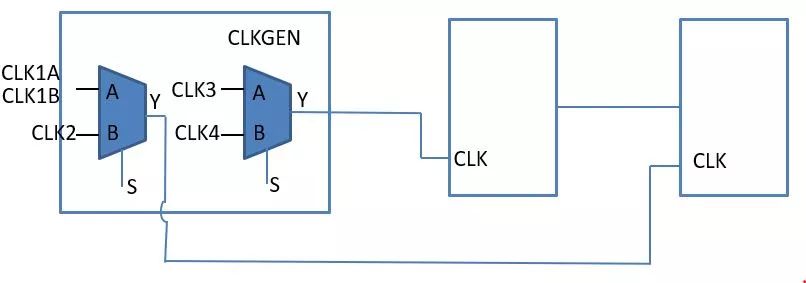

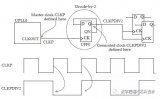

vivado默認計算所有時鐘之間的路徑,通過set_clock_groups命令可禁止在所標識的時鐘組之間以及一個時鐘組內的時鐘進行時序分析。 1.異步時鐘組約束聲明兩時鐘組之間為異步關系,之間不進行時序

2018-09-21 12:40:56

這種時序圖第一次見,不會分析。1.希望技術支持或者哪位大神從編程的角度分析一下這個時序。2.上面的線為什么是曲線,代表什么意思?3.CLK正負的產生源可否是由DSP的引腳產生,經反相器,通過電容,形成兩路互補的信號?附件圖像 1.png35.7 KB

2018-12-03 09:15:27

DAC時序分析

2021-07-29 09:14:26

FPGA時序分析系統時序基礎理論對于系統設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數據傳輸的有效讀寫窗口越來越小,要想在很短的時間限制里,讓數據信號從驅動端完整

2012-08-11 17:55:55

知道“時間分析器”和“planahead”可以幫助我,但我無法理解它的報告。我該怎么做才能解決時間問題。我找不到一些材料來幫助我理解“時序分析”,“代碼風格”,“如何糾正時間問題” ','時序收斂'等等

2019-03-18 13:37:27

時序約束的目的是:規范設計的時序行為,表達設計者所期望滿足的時序條件,指導綜合和布局布線階段的優化算法等,作用:提高系統設計的fmax、得到正確的時序分析報告 1. 系統的最高頻率FmaxFmax

2018-07-03 02:11:23

時序約束的目的是:規范設計的時序行為,表達設計者所期望滿足的時序條件,指導綜合和布局布線階段的優化算法等,作用:提高系統設計的fmax、得到正確的時序分析報告 1. 系統的最高頻率FmaxFmax

2018-07-09 09:16:13

/1pJ5bCtt 下面我們來添加時序約束,打開TimeQuest,點擊菜單欄的ContraintsàCreat Clock,做如圖8.54所示的設置,首先約束CMOS Sensor的同步時鐘VCLK

2015-08-18 21:24:30

(latch edge):數據鎖存的時鐘邊沿,也是靜態時序分析的終點。3.Clock Setup Time (Tsu) 建立時間(Tsu):是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立

2012-01-11 11:43:06

:set_input_delay -clock [get_clocks clkin_adc_a] -max 0.3 [get_ports {datain_adc_a_p }] set

2020-08-06 06:07:05

您好,我正在使用最新的A.09.90.05固件。查看“編程”部分下的幫助文件,在'SENSe:MIXer:'樹下,他們有命令設置RF輸入功率(即'INPut:POWer)和LO功率(即'LO

2019-01-07 16:03:10

嗨,我在N6700B主機中使用了兩個模塊(N6762A和N6784A)。我知道查詢正常(設定或編程)輸出電壓的命令,但我正在尋找查詢電源端子實際輸出電壓的命令。在遠程使用時,電源輸出將略大于編程電壓

2018-12-06 15:56:24

約束文件(XDC文件),它包含用于時序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時鐘向導”的IP來

2019-08-02 09:54:40

某些時鐘是異步的命令:set_clock_groups -name async_ADC_ETH -asynchronous \ -group [get_clocks

2018-11-05 11:31:53

會影響到對 Tsu 的分析,也會影響到對Thold的分析。因此,采用set_clock_uncertainty的參數要多一些。如果要理解這個命令對系統時序分析的影響,就需要對 Altera的延時計算的概念

2012-03-05 15:02:22

自己做了一個工程,靜態時序分析的結果CLK信號的SLACK是負值(-7.399ns),書上說該值是負值時說明時序不對,但是我感覺時序仿真的結果是對的。是不是時序仿真波形正確就不用管靜態時序分析的結果了?請高手指點

2010-03-03 23:22:24

我只有非常有限的知識來使用tcl命令進行時序分析(不用于時序約束,僅用于時序分析)。這些命令如下:check_timingreport_timing_summary我希望知道一些最常見的tcl命令來

2019-03-11 13:41:27

轉自:VIVADO時序分析練習時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

大部分的時序分析和約束都寫在這里了。 一、基本時序路徑1、clock-to-setup周期約束跨時鐘域約束: (1)當源觸發器和目標觸發器的驅動時鐘不同,且時鐘的占空比不是50

2017-03-09 14:43:24

總得來說,FALSE PATH就是我們在進行時序分析時,不希望工具進行分析的那些路徑。一般不需要工具時序分析的路徑指的是異步的路徑,異步路徑就是指的不同時鐘域的路徑。在QuartusII的一個培訓

2017-06-27 06:34:40

總得來說,FALSE PATH就是我們在進行時序分析時,不希望工具進行分析的那些路徑。一般不需要工具時序分析的路徑指的是異步的路徑,異步路徑就是指的不同時鐘域的路徑。在QuartusII的一個培訓

2017-06-27 00:00:41

總得來說,FALSE PATH就是我們在進行時序分析時,不希望工具進行分析的那些路徑。一般不需要工具時序分析的路徑指的是異步的路徑,異步路徑就是指的不同時鐘域的路徑。在QuartusII的一個培訓

2017-06-26 23:54:23

本帖最后由 630183258 于 2017-9-27 10:11 編輯

一、TLC549時序分析1、TLC549管腳圖2、時序圖3、時序分析(1)nCS拉低后需要延時1.4us,然后發送發送

2017-09-27 10:04:22

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

為什么靜態時序分析受組件(符號)名稱的影響?我在示意圖中有一個ISR,當我把它稱為“CuttIsIr”時,靜態時序分析返回一個警告“設置時間違反”,但是當我稱之為“UTHISISR”時,一切都

2019-07-30 10:42:26

就是基于時序進行分析的,而絕大多數的時序路徑的計算又都是以時鐘為基礎的。所謂時鐘定義是指對于設計中所用到的時鐘設定名稱、周期、相位、占空比。在Primetime中用如下命令來實現

2018-08-28 11:58:31

當我實現我的設計時,它會報告警告“沒有找到set_false_path約束的有效對象,帶有選項'-from [get_clock userclk1]'”。但我可以使用TB“get_clocks

2018-11-06 11:29:25

挑戰。本文主要介紹了邏輯設計中值得注意的重要時序問題,以及如何克服這些問題。最后介紹了利用Astro工具進行時序分析的方法。關鍵詞:ASIC;同步數字電路;時序;Astro引言 隨著系統時鐘頻率的提高

2012-11-09 19:04:35

器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。基本的電子系統如圖 1所示,一般自己的設計都需要時序分析,如圖 1所示的Design,上部分為時序組合邏輯,下部分只有組合

2018-04-03 11:19:08

請教如何做時序分析

2013-06-01 22:45:04

新手,求教怎么根據spi時序編程,最好有例子,這是我的時序,真心求教

2016-01-11 16:45:31

了時鐘,也可以使用set_input_transition命令來約束。Clock Uncertainty可以使用set_clock_uncertainty約束來指定時鐘周期的timing

2023-04-20 16:17:54

Cadence高速PCB的時序分析:列位看觀,在上一次的連載中,我們介紹了什么是時序電路,時序分析的兩種分類(同步和異步),并講述了一些關于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的時序分析 1.引言 時序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發了一封 e-mail,希望能夠得到一份時序分析的案

2010-04-05 06:37:13 0

0 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 靜態時序概念,目的

靜態時序分析路徑,方法

靜態時序分析工具及邏輯設計優化

2010-07-09 18:28:18 129

129 使用時鐘PLL的源同步系統時序分析一)回顧源同步時序計算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 跳變點是所有重要時序分析工具中的一個重要概念。跳變點被時序分析工具用來計算設計節點上的時延與過渡值。跳變點的有些不同含義可能會被時序分析工程師忽略。而這

2010-09-15 10:48:06 1461

1461

介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 討論了靜態時序分析算法及其在IC 設計中的應用。首先,文章討論了靜態時序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時的因素。最后通過一個完整的IC 設計

2011-12-20 11:03:16 95

95 _靜態時序分析(Static_Timing_Analysis)基礎及應用[1]。

2016-05-09 10:59:26 31

31 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 靜態時序分析基礎及應用

2017-01-24 16:54:24 7

7 在進行時序分析時片上工藝差別通常會導致嚴重的“時鐘悲觀效應”。這種問題可以通過CPR(Clock Pessimism Reduction)操作來恢復.然而經常有用戶咨詢我們說在他們的設計中CPR操作

2017-02-07 18:04:11 1357

1357 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

時序圖是描述設備工作過程的時間次序圖,也是用于直觀分析設備工作過程的一種圖形。如電子技術中的觸發器、定時器、計數器等均用時序圖來描述其工作原理。在plc順序控制設計法編制梯形圖程序時往往是先畫出時序

2017-10-23 09:39:25 86341

86341

I2C總線的結構、工作時序和模擬編程

2017-10-24 14:34:20 13

13 如何看懂芯片的時序圖,進行編程設計是單片機對外接芯片進行操作的基礎。本文以1602為例,解析單片機對芯片時序圖的編程思路。

2018-01-06 10:13:01 10501

10501

STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。以分析的方式區分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

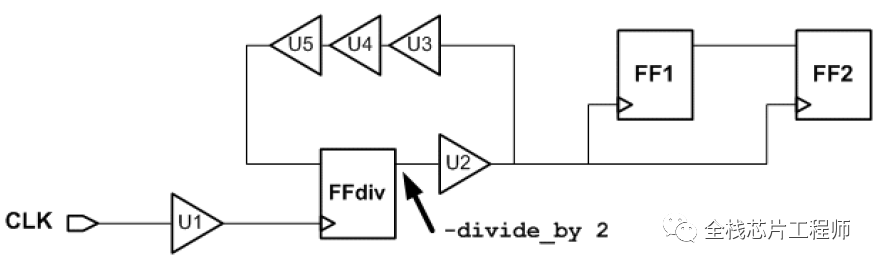

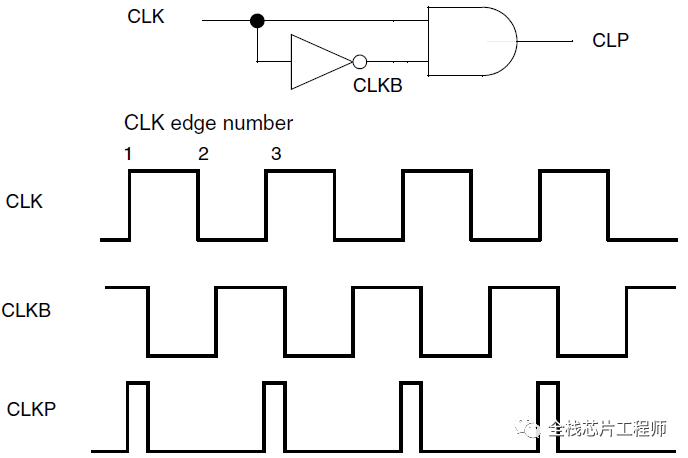

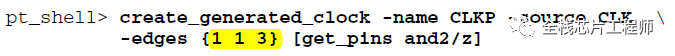

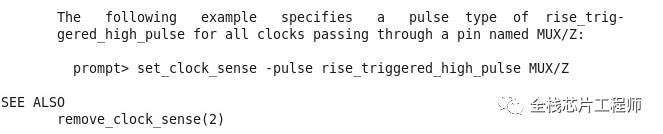

10 今天我們要介紹的時序分析概念是generate clock。中文名為生成時鐘。generate clock定義在sdc中,是一個重要的時鐘概念。

2018-09-24 08:12:00 7990

7990

如果時鐘同時驅動I/O和Slice中的邏輯資源,且負載小于2000時,可通過CLOCK_LOW_FANOUT屬性對相應的時鐘net進行設置,最終可使工具將該時鐘驅動的所有負載放置在同一個時鐘域內。通過命令report_clock_utilization生成的報告可查看每個時鐘的負載,如下圖所示。

2018-11-07 11:08:44 4333

4333

了解report_design_analysis,這是一個新的Vivado報告命令,可以獨特地了解時序和復雜性特征,這些特性對于分析時序收斂問題很有價值。

2018-11-26 07:01:00 3313

3313 FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 1894

1894

靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 時序分析是以分析時間序列的發展過程、方向和趨勢,預測將來時域可能達到的目標的方法。此方法運用概率統計中時間序列分析原理和技術,利用時序系統的數據相關性,建立相應的數學模型,描述系統的時序狀態,以預測未來。

2019-11-15 07:02:00 2570

2570

停止條件即示波器停止“統計分析”的條件,當測試條件滿足預設條件時,時序分析軟件會停止統計完成分析工作。

2020-04-29 15:18:52 2425

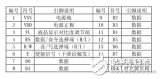

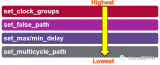

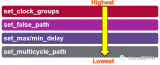

2425 XDC描述的時序約束是有優先級的,尤其是涉及到時序例外的約束,如set_clock_groups、set_false_path、set_max_delay和set_multicycle_path。如果這些約束施加到同一條路徑上,那么其優先級如下圖所示。

2020-09-07 10:53:49 8944

8944

靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 當我們開始精通編程語言時,我們不僅希望實現最終的編程目標,而且還希望可以使我們的程序更高效。在本文中,我們將學習一些 Ipython 的命令,這些命令可以幫助我們對 Python 代碼進行時間分析

2020-11-25 10:43:00 10

10 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文檔的主要內容詳細介紹的是時序分析的靜態分析基礎教程。

2021-01-14 16:04:00 14

14 本文檔的主要內容詳細介紹的是時序分析的Timequest教程免費下載。

2021-01-14 16:04:00 3

3 本文檔的主要內容詳細介紹的是時序分析的Timequest教程免費下載。

2021-01-14 16:04:00 15

15 Clock shew是數字集成電路設計中一個重要的因素。本文比較了在同步電路設計中0clock shew和非0clock shew時鐘分布對電路性能的影響,分析了通過調整時鐘樹中CLOCK SKEW來改善電路性能的方法,從而說明非0clock shew時鐘分布是如何提高同步電路運行的最大時鐘頻率的。

2021-01-14 16:26:52 21

21 基本正確 器件時序, 約束采用的是其中的 tframe = 1.3 - 1.9ns 約束: set_input_delay -clock [get_clocks rxDco_p] -clock

2021-04-10 09:43:02 1556

1556

關于objects1、分類2、包括六類:Design、clock、port、net(模塊與模塊之間的互連線)、cell(例化的模塊)、pin(cell里面的引腳)3、design可以轉換為cell4

2021-11-09 20:51:07 2

2 今天我們要介紹的時序分析基本概念是collection。代表的是一個集合,類似指針。在數字后端工具中,我們可以通過命令get_*來尋找想要的Object。這些get_*命令返回的就是collection。不同類型的object對應不同的get命令。

2021-11-26 10:30:18 3272

3272 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 有一說一,我之前還真不知道set命令這么好用,還傻呵呵地自己寫函數做腳本階段性判斷,判斷上一條命令是否有問題,有問題就直接退出腳本。

2022-11-25 09:10:32 290

290 這個命令指定clock之間是異步關系,時序分析時會完全ignore這些clock之間的path。

2022-12-12 09:49:11 1723

1723 使用SDC命令create_clock創建時鐘,時鐘周期20,占空比50%的時鐘信號

2023-06-18 09:42:13 2273

2273

引言 在同步電路設計中,時序是一個非常重要的因素,它決定了電路能否以預期的時鐘速率運行。為了驗證電路的時序性能,我們需要進行 靜態時序分析 ,即 在最壞情況下檢查所有可能的時序違規路徑,而不需要測試

2023-06-28 09:38:57 714

714

今天我們要介紹的時序分析基本概念是 **clock group,簡稱時鐘組。** 定義完時鐘后,我們也需要通過設置clock group來確認各個時鐘之間的關系。

2023-07-03 14:37:27 716

716

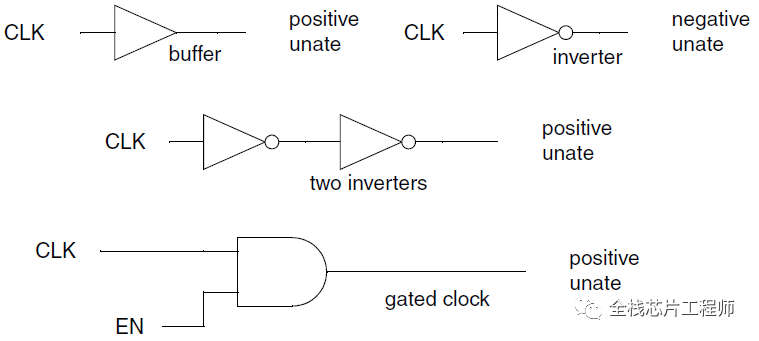

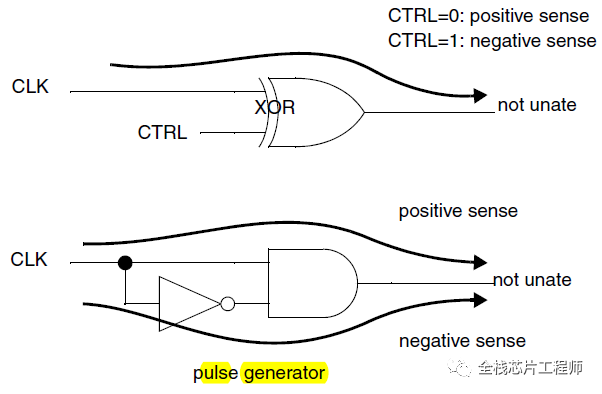

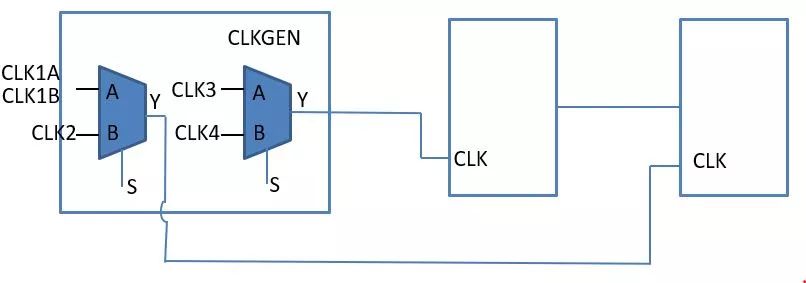

今天我們要介紹的時序分析概念是clock gate。 clock gate cell是用data signal控制clock信號的cell,它被頻繁地用在多周期的時鐘path,可以節省功耗。

2023-07-03 15:06:03 1484

1484

今天我們要介紹的基本sdc是 **時序特例** ,也就是我們常說的Path exception。針對一些路徑需要的一些特殊設定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

2023-07-03 15:34:52 471

471

今天我們要介紹的時序分析概念是 **AOCV** 。全稱Stage Based Advanced OCV。我們知道,在OCV分析過程中,我們會給data path,clock path上設定單一的timing derate值。

2023-07-03 16:29:05 1164

1164

??本文主要介紹了靜態時序分析 STA。

2023-07-04 14:40:06 528

528

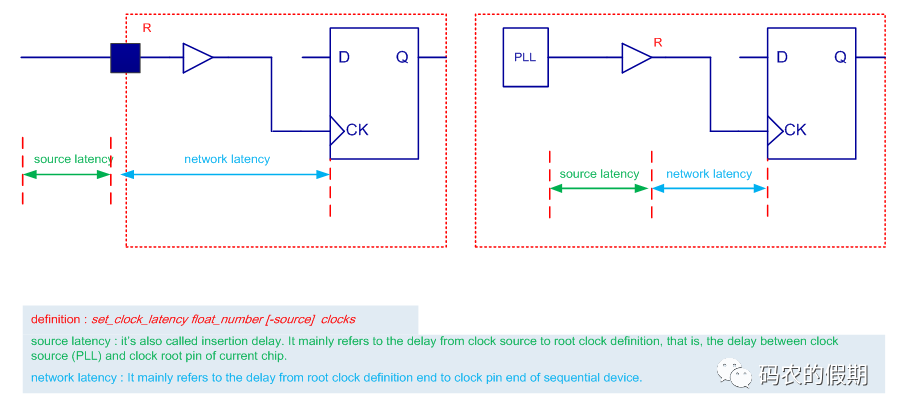

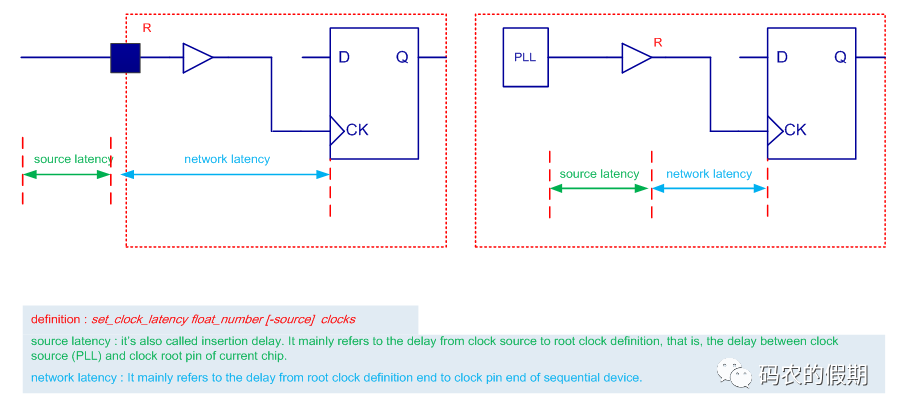

今天要介紹的時序分析基本概念是Latency, 時鐘傳播延遲。主要指從Clock源到時序組件Clock輸入端的延遲時間。

2023-07-04 15:37:08 1311

1311

今天我們要介紹的時序分析概念是generate clock。中文名為生成時鐘。generate clock定義在sdc中,是一個重要的時鐘概念。

2023-07-06 10:34:18 1234

1234

要探討今天的主題,首先需要跟大家一起學習下clock latency這個基本概念。Clock latency通俗意義上是指clock定義點到clock sink point(時序器件的clock

2023-07-06 15:34:44 1644

1644

今天我們介紹的時序分析基本概念是Virtual Clock,中文名稱是虛擬時鐘。

2023-07-07 16:52:55 744

744

今天我們要介紹的時序分析命令是uncertainty,簡稱時鐘不確定性。

2023-07-07 17:23:46 1796

1796

在本篇博文中,我們來聊聊“RQS_CLOCK-12”時鐘設置建議以及它如何幫助達成時序收斂。

2023-07-26 09:53:50 384

384

Linux命令和Shell編程之間存在密切的聯系。 首先,Shell是Linux命令行下的解釋器,它提供了一個用戶界面,使用戶能夠與Linux內核進行交互。Shell解釋器可以解釋和執行用戶輸入

2023-11-08 10:53:26 359

359

電子發燒友App

電子發燒友App

評論