數字電路簡介:

用數字信號完成對數字量進行算術運算和邏輯運算的電路稱為數字電路,或數字系統。由于它具有邏輯運算和邏輯處理功能,所以又稱數字邏輯電路。現代的數字電路由半導體工藝制成的若干數字集成器件構造而成。邏輯門是數字邏輯電路的基本單元。存儲器是用來存儲二進制數據的數字電路。

數字電路特點:

1、 同時具有算術運算和邏輯運算功能

數字電路是以二進制邏輯代數為數學基礎,使用二進制數字信號,既能進行算術運算又能方便地進行邏輯運算(與、或、非、判斷、比較、處理等),因此極其適合于運算、比較、存儲、傳輸、控制、決策等應用。

2、 實現簡單,系統可靠

以二進制作為基礎的數字邏輯電路,可靠性較強。電源電壓的小的波動對其沒有影響,溫度和工藝偏差對其工作的可靠性影響也比模擬電路小得多。

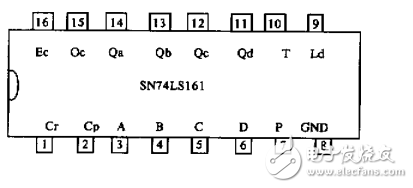

3、 集成度高,功能實現容易

集成度高,體積小,功耗低是數字電路突出的優點之一。電路的設計、維修、維護靈活方便,隨著集成電路技術的高速發展,數字邏輯電路的集成度越來越高,集成電路塊的功能隨著小規模集成電路(SSI)、中規模集成電路(MSI)、大規模集成電路(LSI)、超大規模集成電路(VLSI)的發展也從元件級、器件級、部件級、板卡級上升到系統級。電路的設計組成只需采用一些標準的集成電路塊單元連接而成。對于非標準的特殊電路還可以使用可編程序邏輯陣列電路,通過編程的方法實現任意的邏輯功能。

數字電路的劃分:

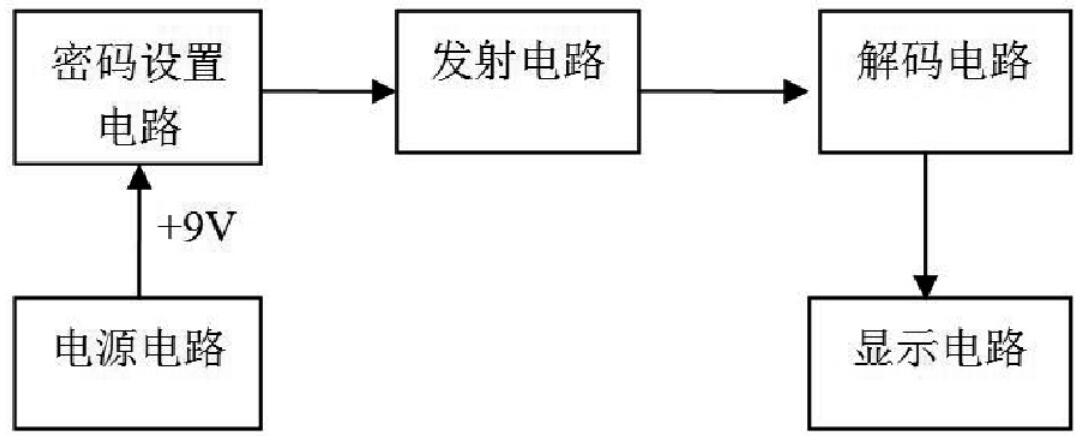

1.按功能分為組合邏輯電路和時序邏輯電路兩大類。

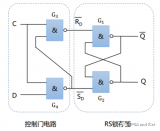

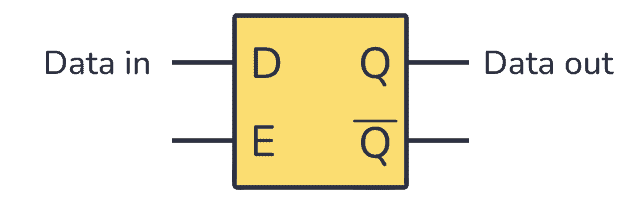

前者在任何時刻的輸出,僅取決于電路此刻的輸入狀態,而與電路過去的狀態無關,它們不具有記憶功能。常用的組合邏輯器件有加法器、譯碼器、數據選擇器等。后者在任何時候的輸出,不僅取決于電路此刻的輸入狀態,而且與電路過去的狀態有關,它們具有記憶功能。

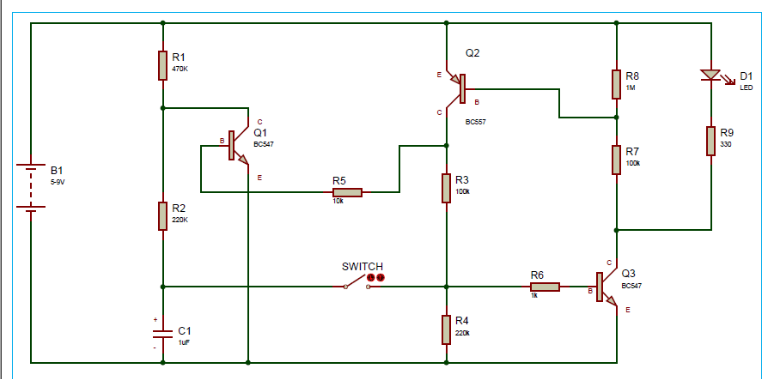

2.按結構分為分立元件電路和集成電路。

前者是將獨立的晶體管、電阻等元器件用導線連接起來的電路。后者將元器件及導線制作在半導體硅片上,封裝在一個殼體內,并焊出引線的電路。集成電路的集成度是不同的。

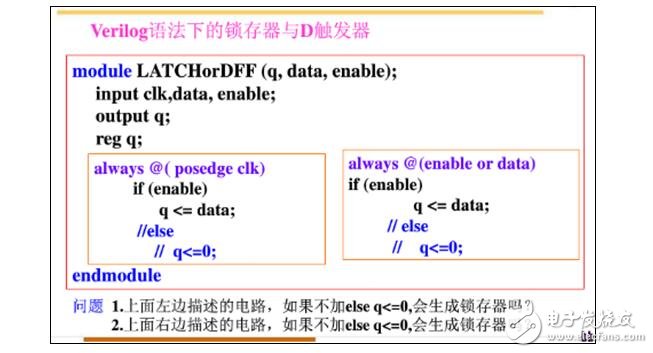

數字電路中如何避免產生不必要的鎖存器方法解析:

1. if……else……結構中缺少else

先看一個實際的例子:

用quartus綜合一下這兩個電路,看看產生的RTL圖是怎樣的:

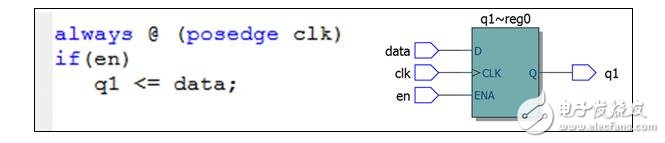

左邊的電路:

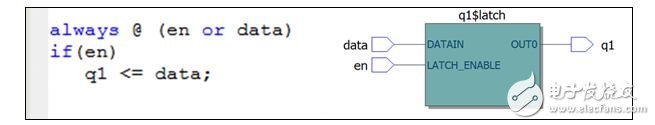

右邊的電路:

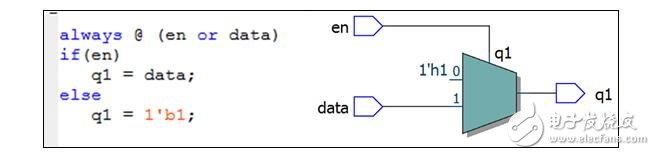

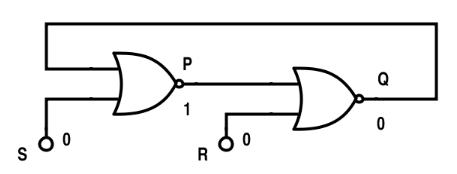

由RTL視圖可以直觀的看出,左邊的電路沒有生成鎖存器,而右邊的電路生成了一個我們不想要的鎖存器(q1$latch)。左邊的電路是時序邏輯,生成觸發器,而觸發器是有使能端(en)的,使能端無效時就可以保存數據,無需鎖存器。右邊的電路是組合邏輯,在en為低電平時,輸出q1要保持不變,而組合邏輯沒有存儲元件,只能生成鎖存器來保持數據。所以在時序邏輯中,不完整的 if…else… 結構并不會生成鎖存器,而組合邏輯中不完整的 if…else… 結構就會生成鎖存器。為了避免我們設計的組合邏輯中出現不想要的鎖存器,在使用 if…else… 結構時一定要寫完整。把剛才例子中右邊的電路寫完整,并查看其RTL視圖如下:

寫完整后,就沒有生成鎖存器,而是生成了一個二選一的選擇器,這正是我們想要設計的。

2. case結構中的分支沒有包含所有情況且沒有default語句

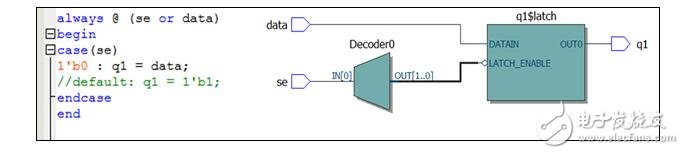

case結構中一般要加上default語句,以保證出現意外情況也可以作出相應的反應。如果沒有加default并且case分支不完整,當出現case分支中沒有列出的情況時,電路狀態保持原來的狀態不變,于是就會生成鎖存器來保存狀態,如下圖的電路所示:

圖中case分支中只寫了(se=0)的情況,而(se=1)的情況未給出,且沒有寫default,于是當(se=1)時,q1保持原來的值不變,這樣就產生了鎖存器(q1$latch)。

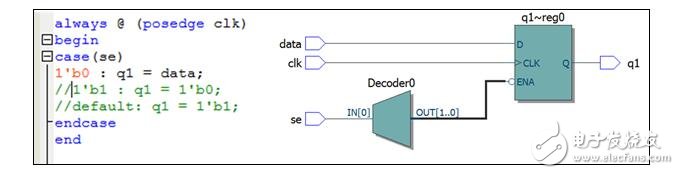

如果將case分支補全,或者加上default語句,則如下圖所示:

補全case分支后,就不會生成鎖存器了。

同樣,只有在組合邏輯中的case結構才有可能產生鎖存器,而在時序邏輯電路中,即使case結構中的分支不完整,也不會產生鎖存器,如下圖所示:

實際上,在時序邏輯中,由于觸發器具有鎖存數據的功能,所以不會生成鎖存器,鎖存器只會在組合邏輯電路中產生。

因此,在設計組合邏輯電路時,要注意將 if…else… 結構中的else寫完整,case結構中一定要加上default語句,這樣可以減少綜合出鎖存器的可能性。

電子發燒友App

電子發燒友App

評論