首先應該明確鎖存器和觸發器也是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合電路的特性。

組合電路就是一個真值表,一個函數,一組輸入對應一組輸出,當前什么輸入就根據函數得到什么輸出,實時跟蹤變化,這樣也就容易有冒險、競爭之類的問題產生毛刺。

鎖存器:電平敏感

always @ (enable)

??if (enable) ?q 《= d;

那就是說,在enable有效的時間內,q完全跟蹤d的值,比如在這個時間內d變化了,q跟著變化,當enable失效的時候,q存儲d最后的值。

觸發器:我們把輸出只在時鐘某個時刻變化的玩意兒叫觸發器。邊沿敏感

always @ (posedge enable)

??if (enable) q 《= d;

這個便是一個d觸發器。只在enable(一般大家都叫它clock)的上升沿q采樣d,而且在每個時鐘的上升沿都會采樣。

在fpga中一般避免用latch,因為在FPGA中觸發器資源豐富,不用白不用,latch由于是電平觸發的,相對觸發器來說容 易產生毛刺,電路不穩定.

latch的優點是完成同一個功能所需要的門較觸發器要少,所以在asic中用的較多

那最后再說寄存器,寄存器這個玩意兒是一個概念層次的東西,1個寄存器就是能存1bit數據的東西。既可以用觸發器實現也可以用鎖存器實現。以觸發器為例,由于觸發器每個時鐘上升沿都會采樣,所以觸發器會有一個反饋邏輯,當load有效的時候才會采樣d,否則保持不變。

always @ (posedge clk or negedge rst_n)

if (!rst_n)

q 《= 0;

else if (load)

q 《= d;

這便就是一個寄存器了。

1. 寄存器

在實際的數字系統中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器.由于觸發器內有記憶功能,因此利用觸發器可以方便地構成寄存器。由于一個觸發器能夠存儲一位二進制碼,所以把n個觸發器的時鐘端口連接起來就能構成一個存儲n位二進制碼的寄存器。

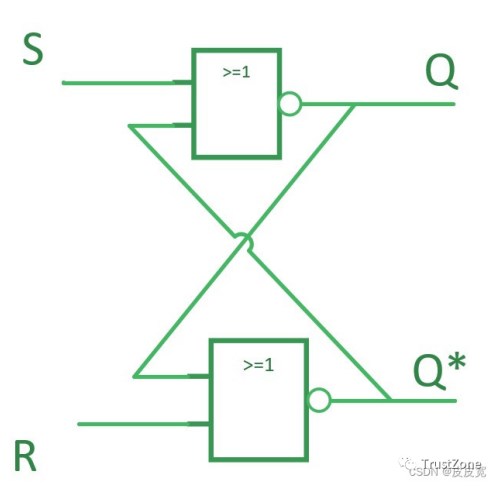

2 .鎖存器

由若干個鐘控D觸發器構成的一次能存儲多位二進制代碼的時序邏輯電路。數據有效遲后于時鐘信號有效。這意味著時鐘信號先到,數據信號后到。在某些運算器電路中有時采用鎖存器作為數據暫存器。

3. 鎖存器與寄存器的區別:

(1)寄存器是同步時鐘控制,而鎖存器是電位信號控制。鎖存器一般由電平信號控制,屬于電平敏感型。寄存器一般由時鐘信號信號控制,屬于邊沿敏感型。

(2)寄存器的輸出端平時不隨輸入端的變化而變化,只有在時鐘有效時才將輸入端的數據送輸出端(打入寄存器),而鎖存器的輸出端平時總隨輸入端變化而變化,只有當鎖存器信號到達時,才將輸出端的狀態鎖存起來,使其不再隨輸入端的變化而變化

可見,寄存器和鎖存器具有不同的應用場合,取決于控制方式以及控制信號 和數據之間的時間關系:若數據有效一定滯后于控制信號有效,則只能使用鎖存器;數據提前于控制信號而到達并且要求同步操作,則可用寄存器來存放數據。

編輯:jq

-

寄存器

+關注

關注

31文章

5343瀏覽量

120426 -

鎖存器

+關注

關注

8文章

906瀏覽量

41520 -

觸發器

+關注

關注

14文章

2000瀏覽量

61165

原文標題:鎖存器與寄存器的區別

文章出處:【微信號:hoperun300339,微信公眾號:潤和軟件】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

鎖存器與寄存器有哪些區別

鎖存器與寄存器有哪些區別

評論