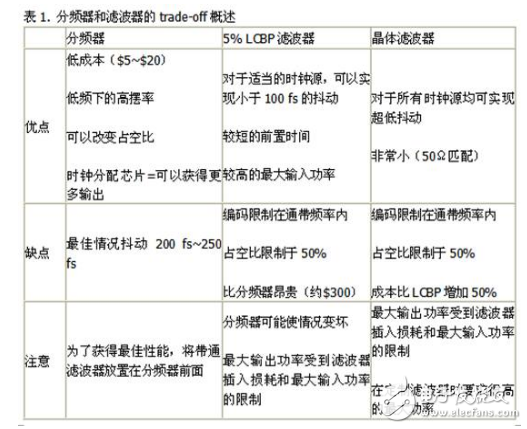

表1中概述了用于改善擺率的分頻器和濾波器解決方案。

注意?

為了獲得最佳性能,將帶通濾波器放置在分頻器前面

分頻器可能使情況變壞

最大輸出功率受到濾波器插入損耗和最大輸入功率的限制

最大輸出功率受到濾波器插入損耗和最大輸入功率的限制

在定制濾波器時要求很高的最大功率

使用背對背Schottky二極管在信號進入ADC時鐘輸入端時將信號箝位是明智的。這使得源幅度增加,因此增加了擺率,同時使得時鐘幅度與轉換器時鐘輸入電平兼容。

如果是小時鐘系統或者最后的電路級具有短的走線,可以結合箝位二極管使用變壓器。變壓器是無源的,不會將抖動添加到整體時鐘信號中。變壓器還可以為振蕩器信號提供增益,增加式4中的A項(幅度)。最后,變壓器自身可提供通帶濾波。具有增益(阻抗比為1:2或1:4)的變壓器有較窄的帶寬,提供了更好的時鐘信號濾波。變壓器還可以將該單端信號轉換為差分信號,這在目前的ADC時鐘輸入接口中是常見的,也是強力推薦的。

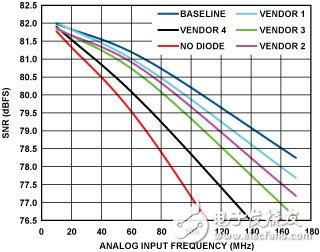

應當注意,并非所有的二極管都能發揮良好的作用(圖14)。在相同的條件下進行測量,其中基線是相對于所有其他二極管的性能最好的二極管的SNR曲線。應當仔細閱讀說明書并且特別注意動態電阻和電容的參數。具有低R和C值的二極管可以加快箝位速度。

?

圖14. 箝位Schottky二極管的選擇影響AD9446-80的性能

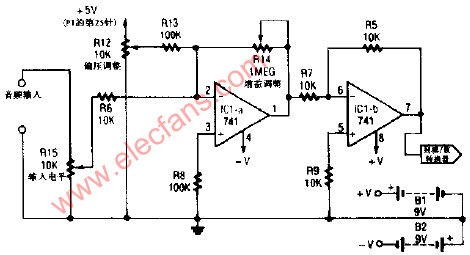

這里將16 bit 80 MSPS ADC AD9446用作測試平臺;其中增加了時鐘源中的背對背二極管。圖15中示出了用于進行評估的電路。

圖15. 測量圖14中數據的AD9446時鐘電路

在時鐘硬件接口中減少抖動

在與ADC的時鐘輸入引腳連接時,可以使用許多電路和解決方案。然而,式5

?

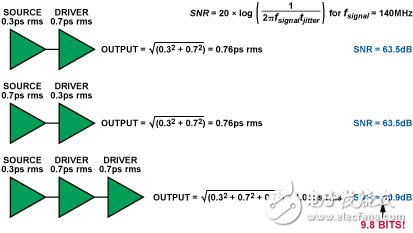

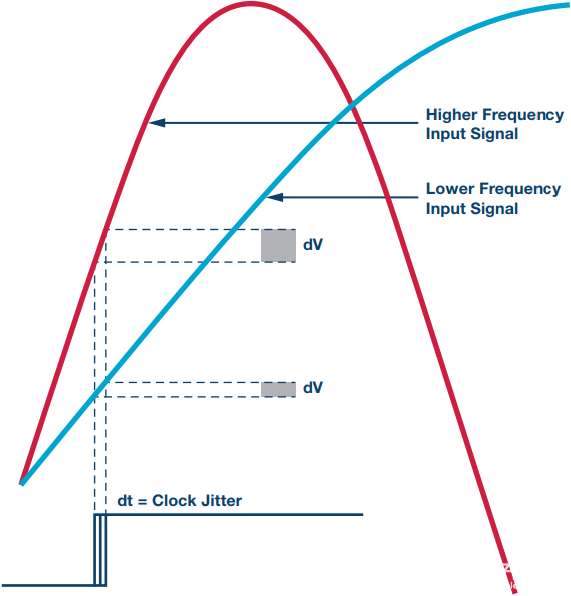

提醒我們,信號鏈路中的每個有源元件(振蕩源、驅動器或扇出門、分頻器等)將增加ADC的時鐘輸入引腳處的總抖動量。圖16示出,增加兩個門(每個門貢獻700 fs的抖動)到具有300 fs抖動的時鐘源中,在140 MHz頻率下會使分辨率從約12 bit下降到小于10 bit。

?

圖16. 多個驅動器門增加抖動并且減小SNR

因此,使時鐘信號鏈路中的元件數目最小有助于降低總的RSS抖動。

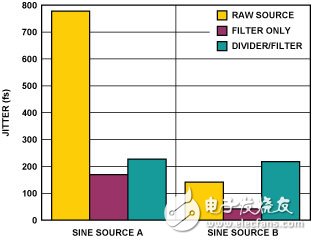

還應當注意所選擇的時鐘門的類型。如果希望在較高的模擬輸入頻率下獲得較好的性能,則簡單的邏輯門可能不是最佳選擇。最好仔細閱讀候選器件的技術資料并理解相關的參數,如抖動和偏移。當這些器件與抖動特別低的時鐘源一起工作時,這是非常重要的。例如,在圖17中,時鐘源A具有800 fs的抖動,時鐘源B具有125 fs的抖動。使用晶體濾波器可以將其抖動分別減少到175 fs和60 fs。然而,分頻器(或者具有類似抖動參數的門電路)可能使抖動均增加到200 fs以上。這再次說明了在時鐘信號鏈路中正確選擇和放置時鐘驅動器的重要性。

?

圖17. 門電路將增加抖動

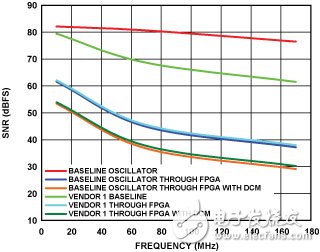

另一種常見方法,即使用FPGA,并不能實現技術資料上的性能。FPGA(其常具有提供分頻的數字時鐘管理器(DCM))可以用作一個靈活的門驅動器。然而,如圖18所示,使用AD9446-80(80 MSPS ADC)進行測試,該方法導致SNR顯著下降;例如,能夠實現13 bit的ENOB。紅色曲線為使用高性能振蕩器時的基線SNR,綠色曲線示出了在相同的時鐘下,使用FPGA作為高性能振蕩器和轉換器之間的門驅動器時獲得的性能與基線性能之間的差異。在40 MHz下,FPGA將SNR減少到52 dB(8.7 bit性能),而DCM貢獻了額外8 dB(1.3 bit)的SNR下降。SNR下降29 dB的性能差異是非常令人擔憂的,在使用式1計算時,意味著FPGA驅動器門自身即可帶來約10 ps的抖動。

圖18. FPGA門驅動電路影響AD9446-80的性能

選擇最佳的時鐘驅動器是困難的。表2給出了市售的多個驅動器門所增加抖動的大致比較結果。表格下方給出的建議有助于獲得優良的ADC性能。

表2. 時鐘驅動器門及其增加的抖動

結論

為了實現轉換器的最佳性能,應當理解整個時鐘系統。對于具有非常高分辨率有抖動限制的ADC或者“完美的”N bit ADC而言,圖3以及式1和2是分析其時鐘要求時非常有用的工具。如果模擬輸入頻率比圖3中的交點高,則必須考慮使用具有更少抖動的時鐘源和相關電路。

可以通過許多方式降低系統時鐘電路的抖動,包括改進時鐘源、濾波和/或分頻,以及適當地選擇時鐘電路硬件。應當注意時鐘的擺率。這將確定在轉換過程中可能惡化轉換器性能的噪聲量。使該轉換時間最小可以改善轉換器的性能。

由于信號鏈路中的每個元件將增加總體抖動,因此應僅使用必要的電路驅動和時鐘分配。最后,不要使用“廉價的”門,它們的性能可能是令人失望的。就象不可能指望價值$70000的汽車在使用$20的輪胎時獲得出眾的性能一樣。

進一步閱讀

AD6645?Data Sheet.

AD9446?Data Sheet.

Barrow, Jeff. "Reducing Ground Bounce in DC-to-DC Converters-Some Grounding Essentials."Analog Dialogue, vol. 41, no. 2 (2007). pp. 3-7.

Brannon, Brad. Application Note?AN-756, "Sampled Systems and the Effects of Clock Phase Noise and Jitter."

Brannon, Brad and Allen Barlow. Application Note?AN-501, "Aperture Uncertainty and ADC System Performance."

Curtin, Mike, and Paul O`Brien. "Phase-Locked Loops for High-Frequency Receivers and Transmitters-Part 2."Analog Dialogue, vol. 33, no. 1 (1999). pp. 13-17.

Custom Discrete Crystal Filters

·Filtronetics ()

·Anatech Electronics, Inc. ().

HSMS-2812?Data Sheet.

Kester, Walt.?Analog-Digital Conversion. Analog Devices (2004). Section 2.3, p. 2.72,?.

K&L Filter?Data Sheets.

Mercer, Doug, Steve Reine, and David Carr. Application Note?AN-642, “Coupling a Single-Ended Clock Source to the Differential Clock Input of Third-Generation TxDAC and TxDAC+ Products."

Monolithic Crystal Filters (used for majority of evaluations)

·QuartzCom ().

Smith, Paul. Application Note?AN-741. "Little-Known Characteristics of Phase Noise."

電子發燒友App

電子發燒友App

評論