VCS是編譯型Verilog模擬器,它完全支持OVI標準的Verilog HDL語言、PLI和SDF。VCS具有目前行業中最高的模擬性能,其出色的內存管理能力足以支持千萬門級的ASIC設計,而其模擬精度也完全滿足深亞微米ASIC Sign-Off的要求。

VCS結合了節拍式算法和事件驅動算法,具有高性能、大規模和高精度的特點,適用于從行為級、RTL到Sign-Off等各個階段。VCS已經將CoverMeter中所有的覆蓋率測試功能集成,并提供VeraLite、CycleC等智能驗證方法。VCS和Scirocco也支持混合語言仿真。VCS和Scirocco都集成了Virsim圖形用戶界面,它提供了對模擬結果的交互和后處理分析。

手機中設置的“待辦事項”屬于.vcs格式。

什么是VCS

- VCS(9413)

相關推薦

VCS232Z_08

VCS232Z_08 - Ultra High Precision Z-Foil Power Current Sensing Resistor with Absolute TCR

1970-01-01 08:00:00

VCS實用技巧分享

VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2023-05-30 09:26:05 463

463

463

463

基于linux系統實現的vivado調用VCS仿真教程

在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最好安裝

2018-07-05 03:30:00 10452

10452

10452

10452

EDA仿真:VCS編譯Xilinx仿真步驟

選擇VCS,再指定庫文件存放的路徑;如果VCS的環境變量設置好了,那么會自動跳出Simulator executable path的路徑的。

2023-03-31 10:21:43 613

613

613

613淺談VCS的兩種仿真flow

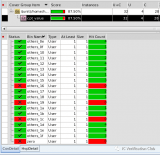

幾乎所有的芯片設計、芯片驗證工程師,每天都在和VCS打交道,但是由于驗證環境的統一化管理,一般將不同的編譯仿真選項集成在一個文件里,只需要一兩個人維護即可。所以大部分人比較少有機會去深入地學習VCS的仿真flow。基于此,本文將介紹VCS仿真的 兩種flow ,概述這兩種flow分別做了哪些事!

2023-01-10 11:20:38 1430

1430

1430

1430VCS的調試模式

VCS-verilog compiled simulator是synopsys公司的產品.其仿真速度相當快,而且支持多種調用方式;使用的步驟和modelsim類似,都要先做

2010-10-09 16:59:08 4891

4891

4891

4891SpinalHDL運行VCS+Vivado相關仿真

本篇文章來源于微信群中的網友,分享下在SpinalHDL里如何絲滑的運行VCS跑Vivado相關仿真。自此仿真設計一體化不是問題。

2022-08-10 09:15:17 1702

1702

1702

1702如何用vcs+verdi仿真Verilog文件

我們以一個簡單的加法器為例,來看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件內容如下:

2023-05-11 17:03:36 652

652

652

652

使用VCS仿真Vivado IP核時遇到的問題及解決方案

前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 1264

1264

1264

1264EDA工具vcs2014.03的環境搭建

由于vcs2014只支持gcc4.4的版本,而ubuntu16.4的gcc是5.4,所以需要先把gcc的版本降到4.4。

2018-12-02 09:23:48 3735

3735

3735

3735vcs和verdi的調試及聯合仿真案例

若想用Verdi觀察波形,需要在仿真時生成fsdb文件,而fsdb在vcs或者modelsim中的生成是通過兩個系統調用$fsdbDumpfile $fsdbDumpvars來實現的。

2020-09-22 15:01:55 7459

7459

7459

7459記錄VCS仿真的IP核只有VHDL文件的解決方法

使用VCS仿真Vivado里面的IP核時,如果Vivado的IP核的仿真文件只有VHDL時,仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 951

951

951

951

VCS獨立仿真Vivado IP核的一些方法總結

最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 1008

1008

1008

1008

vcs學習筆記(常用選項/仿真流程/代碼覆蓋率/綜合后仿真/圖一樂技巧)

VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2022-05-23 16:04:45 6545

6545

6545

6545如何使用Synopsys VCS仿真器進行ZYNQ BFM IPI設計仿真

了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI設計運行仿真。

我們將演示如何編譯仿真庫,為IP或整個項目生成仿真腳本,然后運行仿真。

2018-11-29 06:59:00 4339

4339

4339

4339如何使用Vivado中的Synopsys VCS仿真器進行仿真

了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI設計運行仿真。

我們將演示如何編譯仿真庫,為IP或整個項目生成仿真腳本,然后運行仿真。

2018-11-29 06:57:00 6584

6584

6584

6584利用vcs+verdi仿真工具蜂鳥E200系列處理器仿真分析

開源RISC-V Hummingbird E203(蜂鳥E203)的仿真工具是開源的iverilog,這里利用vcs+verdi仿真工具進行仿真;

2022-11-17 10:28:36 1531

1531

1531

1531VCS獨立仿真Vivado IP核的一些方法總結

前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有

2021-03-22 10:31:16 3027

3027

3027

3027使用VCS兩種仿真flow的基本步驟

VCS是一個高性能、高容量的編譯代碼仿真器,它將高級抽象的驗證技術集成到一個開放的本地平臺中。它能夠分析、編譯和編譯Verilog、VHDL、SystemVerilog和OpenVera所描述

2022-05-07 14:20:57 3333

3333

3333

3333VCS ICO的主要功能有哪些呢?

ico是vcs提供的用于優化覆蓋率的feature;一般用戶通過dist solver bofore等約束了變量的隨機概率,而ico會在用戶約束的基礎上,做一些自動“修正”,以此來優化隨機激勵,提高隨機多樣性,加速覆蓋率收斂,縮短 turn-around time TAT。

2023-09-19 14:59:31 270

270

270

270

新思科技采用VCS 與 Verdi 結合,推出與眾不同的芯片設計

Graphcore 芯片業務副總裁 Phil Horsfield 說:“為了對我們的 IPU 加速器進行全面驗證,需要每天進行涵蓋數以千計的復雜測試場景的仿真回歸分析。新思科技 VCS

2020-08-28 15:22:16 2964

2964

2964

2964VCS2373磁阻開關

VCS2373 是一款高度集成的二維低功耗磁開關傳感器,華芯 13771114899 它在一個超小型封裝內集成了 AMR 磁傳 感器和高精度 CMOS 處理電路,CMOS 處理電路提供精確控制

2022-12-16 10:05:59 289

289

289

289新思科技VCS技術上云,將加速亞馬遜SoC的開發與驗證

? 新思科技(Synopsys)近日宣布,亞馬遜公司旗下云計算服務平臺(Amazon Web Services, Inc., AWS)已在其基于Arm的Graviton2服務器上部署了新思科技VCS

2021-01-07 11:28:06 7842

7842

7842

7842 電子發燒友App

電子發燒友App

評論